# M4G Group (1) Application Note Serial Peripheral Interface (TSPI-C)

## **Outlines**

This application note is a reference material for developing products using Serial peripheral interface (TSPI) function of M4G group (1). This document helps the user check operation of the product and develop its program.

Target sample program: TSPI\_ChToCh\_rx\_int

# **Table of Contents**

| Outlines                                    | 1  |

|---------------------------------------------|----|

| Table of Contents                           | 2  |

| 1. Preface                                  | 3  |

| 2. Reference Document                       | 4  |

| 3. Function to Use                          | 4  |

| 4. Target Device                            | 4  |

| 5. Operation Confirmation Condition         | 5  |

| 6. Evaluation Board Setting                 | 6  |

| 7. Operation of Evaluation Board            | 6  |

| 8. Outline of TSPI Function                 | 7  |

| 9. Sample Program                           | 12 |

| 9.1. Initialization                         | 12 |

| 9.2. Sample Program Main Operation          | 12 |

| 9.3. Output Example of Sample Program       | 13 |

| 9.3.1. Setting Example of Terminal Software | 13 |

| 9.4. Operating Flow of Sample Program       | 14 |

| 10. Precaution                              | 22 |

| 11. Revision History                        | 22 |

| RESTRICTIONS ON PRODUCT USE                 | 23 |

## 1. Preface

This sample program should be used to check the operation of the Serial peripheral interface function. The "write" command transmits data. And the "read" command reads the reception data and outputs to the terminal software.

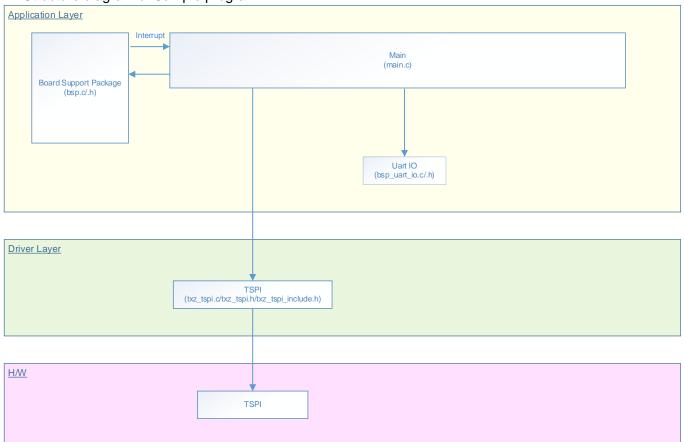

Structure diagram of Sample program

#### 2. Reference Document

Datasheet

TMPM4G Group (1) datasheet Rev1.0 (Japanese edition)

· Reference manual

Serial Communication (TSPI) Rev1.0 (Japanese edition)

Asynchronous Serial Communication Circuit (UART-C) Rev3.0 (Japanese edition)

· Application note

M4G Group (1) Application Note Startup (CMSIS System & Clock Configuration) Rev1.0

· Other reference document

TMPM4G (1) Group Peripheral Driver User Manual (Doxygen)

#### 3. Function to Use

| IP                    | Channel | Port            | Function/Operation mode |

|-----------------------|---------|-----------------|-------------------------|

| Serial Peripheral     | ch2     | PA4 (TSPI2TXD)  | SPI mode: Master        |

| Interface             |         | PA6 (TSPI2SCK)  |                         |

|                       |         | PA7 (TSPI2CS0)  |                         |

|                       | ch4     | PD0 (TSPI4CSIN) | SPI mode: Slave         |

|                       |         | PD1 (TSPI4SCK)  |                         |

|                       |         | PD2 (TSPI4RXD)  |                         |

| Asynchronous Serial   | ch0     | PE2 (UT0RXD)    | UART mode               |

| Communication Circuit |         | PE3 (UT0TXDA)   |                         |

## 4. Target Device

The target devices of this application note are as follows;

| TMPM4G9F15FG  | TMPM4G9F10FG  | TMPM4G9FEFG  | TMPM4G9FDFG  |

|---------------|---------------|--------------|--------------|

| TMPM4G9F15XBG | TMPM4G9F10XBG | TMPM4G9FEXBG | TMPM4G9FDXBG |

| TMPM4G8F15FG  | TMPM4G8F10FG  | TMPM4G8FEFG  | TMPM4G8FDFG  |

| TMPM4G8F15XBG | TMPM4G8F10XBG | TMPM4G8FEXBG | TMPM4G8FDXBG |

|               | TMPM4G7F10FG  | TMPM4G7FEFG  | TMPM4G7FDFG  |

|               | TMPM4G6F10FG  | TMPM4G6FEFG  | TMPM4G6FDFG  |

<sup>\*</sup> This sample program operates on the evaluation board of TMPM4G9F15FG.

If other function than the TMPM4G9F15 one is checked, it is necessary that CMSIS Core related files (C startup file and I/O header file) should be changed properly.

The BSP related file is dedicated to the evaluation board (TMPM4G9F15). If other function than the TMPM4G9F15 one is checked, the BSP related file should be changed properly.

## 5. Operation Confirmation Condition

Used microcontroller

Used board

Unified development environment

Unified development environment

Terminal software

Sample program

TMPM4G9F15FG

TMPM4G9F15FG Evaluation Board by Sensyst

IAR Embedded Workbench for ARM 8.11.2.13606

µVision MDK Version 5.24.2.0

Tera Term V4.96

V1000

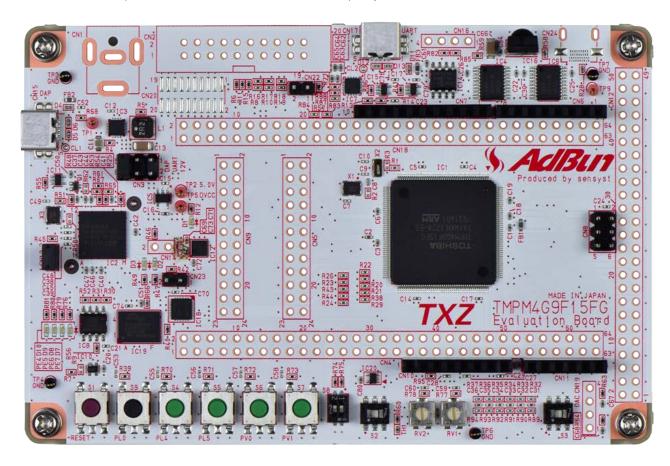

Evaluation board (TMPM4G9F15FG Evaluation Board) Top view

## 6. Evaluation Board Setting

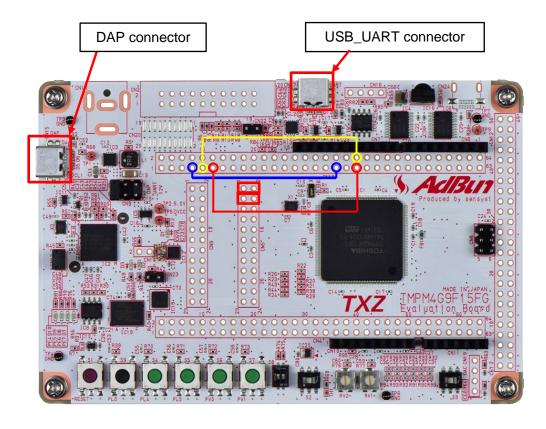

The following pin connections should be done on the evaluation board.

| CN5                 |                  |                  |

|---------------------|------------------|------------------|

| Board function      | Through-hole No. | Through-hole No. |

| USB UART conversion | 1: USB_UT_RX     | 2: PE2           |

| USB UART conversion | 3: USB_UT_TX     | 4: PE3           |

| CN18                              |                  |                  |  |

|-----------------------------------|------------------|------------------|--|

| Board function                    | Through-hole No. | Through-hole No. |  |

| SPI communication (Inter-channel) | 7: PD2           | 35: PA4          |  |

| SPI communication (Inter-channel) | 9: PD1           | 40: PA6          |  |

| SPI communication (Inter-channel) | 11: PD0          | 39: PA7          |  |

## 7. Operation of Evaluation Board

PC and the USB UART are connected for communication with the terminal software.

The sample program should be started up.

The sample program waits for data input to the terminal software.

The "write" command should be input to the terminal software. Then the "read" command should be input.

The data received by the "write" command is read and the character string "TOSHIBA" is output to the terminal software.

## 8. Outline of TSPI Function

TSPI (serial peripheral interface) has four operation mode as SPI/SIO mode, and the clock master/ clock slave mode. One channel/unit which is built-in TSPIxTXD, TSPIxRXD, TSPIxCS0, TSPIxCS0, TSPIxCS1, TSPIxCS3, and TSPIxCSIN can be transmit and receive circuit. Functions are as below.

Table 8.1 Functional outline (SPI mode, master)

|                      | inction<br>sification | Function                                                    | A Functional Description or the range                                                                                                                                                                                |

|----------------------|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmission         |                       | Prescaler dividing selection                                | The clock inputted from the prescaler can be divided 1/1,1/2,1/4up to 1/512.                                                                                                                                         |

|                      | Speed<br>Control      | Baud rate generator                                         | The input clock to baud rate generator. dividing 1/N x 1/2 (N= 1 to 16)                                                                                                                                              |

|                      |                       | Data length                                                 | The data length can be setup in a 1-bit unit. 8 to 32bits (with no parity) 7 to 31bits (with parity)                                                                                                                 |

|                      | Data<br>Format        | Parity                                                      | Selection of with parity/without parity is possible. Selection of even parity/odd parity is possible.                                                                                                                |

|                      |                       | The direction of data transfer                              | Selection of the LSB first/ MSB first is possible.                                                                                                                                                                   |

|                      |                       | FIFO number of section                                      | Transmission: 8 steps (16bits), 4 steps (32bits) Reception: 8 steps (16bits), 4 steps (32bits)                                                                                                                       |

|                      |                       | Communication                                               | Full duplexes (transmission and reception), transmission,                                                                                                                                                            |

|                      | T                     | Operation mode                                              | reception                                                                                                                                                                                                            |

|                      | Transmission and      |                                                             | Single transfer (one burst transfer)                                                                                                                                                                                 |

|                      | Reception             | Transfer mode                                               | Burst transfer (2 to 255 times transfer)                                                                                                                                                                             |

|                      | Control               |                                                             | Continuously transfer (No limit of transfer times specification)                                                                                                                                                     |

|                      |                       | Data sampling timing                                        | Data is sampled with 1st edge.                                                                                                                                                                                       |

|                      |                       | 1 0 0                                                       | Data is sampled with 2nd edge.                                                                                                                                                                                       |

|                      |                       | CS control                                                  | Selection of TSPIxCS0/1/2/3 is possible. Polarity: Selection of positive logic/ negative logic is possible.                                                                                                          |

| SPI                  |                       | Interruption                                                | Transmit interrupt (Transmit completion interrupt, Transmit FIFO interrupt) Receive interrupt (Receive completion interrupt, Receive FIFO interrupt) Error Interrupt (Vertical parity error interrupt, Trigger error |

| mode<br>(Master) Gai | Ganged<br>Control     | Various status<br>detection                                 | interrupt) TSPI modify status, Transmit shift operation, Transmit completion, Transmit FIFO fill level/ empty detection, Receive operation, Receive completion, Receive FIFO fill level/full detection               |

|                      |                       | DMA request                                                 | Transmit: Single DMA request, burst DMA request Receive: Single DMA transfer, burst DMA request                                                                                                                      |

|                      |                       | Trigger communication                                       | Starting communication by trigger. Refer to the "Product                                                                                                                                                             |

|                      |                       | control                                                     | Information" on a reference manual for a trigger source.                                                                                                                                                             |

|                      |                       | Output level of TSPIxTXD during an idle term                | High, Low, a last bit data hold, Hi-z                                                                                                                                                                                |

|                      |                       | Polarity of TSPIxSCK                                        | It is Low to during idle term.                                                                                                                                                                                       |

|                      |                       | during an idle term                                         | It is High to during idle term.                                                                                                                                                                                      |

|                      |                       | Interval time between frames at the time of burst transfer. | 0 x TSPIxSCK cycle to 15 x TSPIxSCK cycles                                                                                                                                                                           |

|                      | Special<br>Control    | Idle time at the time of continuously transfer.             | Period of changing TSPIxCS0/1/2/3 pin to asserted, deasserted, asserted.  1 x TSPIxSCK cycle to 15 x TSPIxSCK cycles                                                                                                 |

|                      |                       | TSPIxSCK delay of deassert                                  | Time of delay between from TSPIxCS0/1/2/3 is asserted to TSPIxSCK is started.  1 x TSPIxSCK cycle to 16 x TSPIxSCK cycles                                                                                            |

|                      |                       | TSPIxCS0/1/2/3<br>deassertion delay                         | Time until TSPIxCS0/1/2/3 pin is deasserted from last data 1 x TSPIxSCK cycle to 16 x TSPIxSCK cycle                                                                                                                 |

|                      |                       | Software reset                                              | Reset by software is possible.                                                                                                                                                                                       |

Table 8.2 Outline of function (SPI mode and Slave)

| Function of                      | lassification              | Function                                              | A Functional Description or the range                                                                                                                                                                                                         |

|----------------------------------|----------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | Data                       | Data length                                           | The data length can be setup in a 1-bit unit. 8 to 32bits (with no parity) 7 to 31bits (with parity)                                                                                                                                          |

|                                  | Format                     | Parity                                                | Selection of with parity/without parity is possible. Selection of even parity/odd parity is possible.                                                                                                                                         |

|                                  |                            | The direction of data transfer                        | Selection of the LSB first/ MSB first is possible.                                                                                                                                                                                            |

|                                  |                            | FIFO number of section                                | Transmission: 8 steps (16bits), 4 steps (32bits)<br>Reception: 8 steps (16bits), 4 steps (32bits)                                                                                                                                             |

|                                  |                            | Communication Operation mode                          | Full duplexes (transmission and reception), transmission, reception                                                                                                                                                                           |

|                                  | Transmission and Reception | Transfer mode                                         | Single transfer (one burst transfer) Burst transfer (2 to 255 times transfer) Continuously transfer (No limit of transfer times specification)                                                                                                |

|                                  | Control                    | Data sampling timing                                  | Data is sampled with 2nd edge.                                                                                                                                                                                                                |

| SPI mode (Slave)  Ganged Control |                            | CS control                                            | TSPIxCSIN Polarity: Selection of positive logic/ negative logic is possible.                                                                                                                                                                  |

|                                  |                            | Interruption                                          | Transmit interrupt (Transmit completion interrupt, Transmit FIFO interrupt) Receive interrupt (Receive completion interrupt, Receive FIFO interrupt) Error Interrupt (Vertical parity error interrupt, Overrun interrupt, Underrun interrupt) |

|                                  |                            | Various status detection                              | TSPI modify status, Transmit shift operation, Transmit completion, Transmit FIFO fill level/ empty detection, Receive operation, Receive completion, Receive FIFO fill level /full detection                                                  |

|                                  |                            | DMA request                                           | Transmit: Single DMA request, burst DMA request Receive: Single DMA transfer, burst DMA request                                                                                                                                               |

|                                  | Special<br>Control         | Output level of TSPIxTXD during an idle term          | High, Low, a last bit data hold, Hi-z                                                                                                                                                                                                         |

|                                  |                            | Output level of TSPIxTXD when underrun error occurred | High, Low                                                                                                                                                                                                                                     |

|                                  |                            | Software reset                                        | Reset by software is possible.                                                                                                                                                                                                                |

Table 8.3 Outline of function (SIO mode and Master)

| Function of                       | classification     | Function                                                                                                                                       | A Functional Description or the range                                                                                                                                                                                           |

|-----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | Transmission       | Prescaler dividing selection                                                                                                                   | The clock inputted from the prescaler can be divided 1/1,1/2,1/4up to 1/512.                                                                                                                                                    |

| speed<br>Control                  |                    | Baud rate generator                                                                                                                            | The input clock to baud rate generator. dividing 1/N x 1/2 (N= 1 to 16)                                                                                                                                                         |

|                                   | Data               | Data length                                                                                                                                    | The data length can be setup in a 1-bit unit. 8 to 32bits (with no parity) 7 to 31bits (with parity)                                                                                                                            |

|                                   | Format             | Parity                                                                                                                                         | Selection of with parity/without parity is possible. Selection of even parity/odd parity is possible.                                                                                                                           |

|                                   |                    | The direction of data transfer                                                                                                                 | Selection of the LSB first/ MSB first is possible.                                                                                                                                                                              |

|                                   |                    | FIFO number of section                                                                                                                         | Transmission: 8 steps (16bits), 4 steps (32bits)<br>Reception: 8 steps (16bits), 4 steps (32bits)                                                                                                                               |

|                                   | Transmission       | Communication Operation mode                                                                                                                   | Full duplexes (transmission and reception), transmission, reception                                                                                                                                                             |

| SIO mode (Master)  Ganged Control | Transfer mode      | Single transfer (one burst transfer) Burst transfer (2 to 255 times transfer) Continuously transfer (No limit of transfer times specification) |                                                                                                                                                                                                                                 |

|                                   |                    | Data sampling timing                                                                                                                           | Data is sampled with 1st edge. Data is sampled with 2nd edge.                                                                                                                                                                   |

|                                   |                    | Interruption                                                                                                                                   | Transmit interrupt (Transmit completion interrupt, Transmit FIFO interrupt) Receive interrupt (Receive completion interrupt, Receive FIFO interrupt) Error Interrupt (Vertical parity error interrupt, Trigger error interrupt) |

|                                   |                    | Various status detection                                                                                                                       | TSPI modify status, Transmit shift operation, Transmit completion, Transmit FIFO fill level/ empty detection, Receive operation, Receive completion, Receive FIFO fill level /full detection                                    |

|                                   |                    | DMA request                                                                                                                                    | Transmit: Single DMA request, burst DMA request Receive: Single DMA transfer, burst DMA request                                                                                                                                 |

|                                   |                    | Trigger communication control                                                                                                                  | Starting communication by trigger. Refer to the "Product Information" on a reference manual for a trigger source.                                                                                                               |

|                                   |                    | Output level of TSPIxTXD during an idle term                                                                                                   | High, Low, a last bit data hold, Hi-z                                                                                                                                                                                           |

|                                   | Special<br>Control | Polarity of TSPIxSCK during an idle term                                                                                                       | It is Low to during idle term. It is High to during idle term.                                                                                                                                                                  |

|                                   |                    | Interval time between frames at the time of burst transfer.                                                                                    | 0 x TSPIxSCK cycle to 15 x TSPIxSCK cycles                                                                                                                                                                                      |

|                                   |                    | Idle time at the time of continuously transfer.                                                                                                | Period of changing TSPIxCS0/1/2/3 pin to asserted, deasserted, asserted  1 x TSPIxSCK cycle to 15 x TSPIxSCK cycles                                                                                                             |

|                                   |                    | Software reset                                                                                                                                 | Reset by software is possible.                                                                                                                                                                                                  |

Table 8.4 Outline of function (SIO mode and Slave)

| Function classification |                             | Function                                     | A Functional Description or the range                                                                                                                                                                                                         |

|-------------------------|-----------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Data<br>Format              | Data length                                  | The data length can be setup in a 1-bit unit. 8 to 32bits (with no parity) 7 to 31bits (with parity)                                                                                                                                          |

|                         |                             | Parity                                       | Selection of with parity/without parity is possible. Selection of even parity/odd parity is possible.                                                                                                                                         |

|                         |                             | The direction of data transfer               | Selection of the LSB first/ MSB first is possible.                                                                                                                                                                                            |

|                         |                             | FIFO number of section                       | Transmission: 8 steps (16bits), 4 steps (32bits)<br>Reception: 8 steps (16bits), 4 steps (32bits)                                                                                                                                             |

|                         | Transmission                | Communication Operation mode                 | Full duplexes (transmission and reception), transmission, reception                                                                                                                                                                           |

|                         | and<br>Reception<br>Control | Transfer mode                                | Single transfer (one burst transfer) Burst transfer (2 to 255 times transfer) Continuously transfer (No limit of transfer times specification)                                                                                                |

|                         |                             | Data sampling timing                         | Data is sampled with 2nd edge.                                                                                                                                                                                                                |

| SIO mode<br>(Slave)     | Ganged<br>Control           | Interruption                                 | Transmit interrupt (Transmit completion interrupt, Transmit FIFO interrupt) Receive interrupt (Receive completion interrupt, Receive FIFO interrupt) Error Interrupt (Vertical parity error interrupt, Overrun interrupt, Underrun interrupt) |

|                         |                             | Various status detection                     | TSPI modify status, Transmit shift operation, Transmit completion, Transmit FIFO fill level/ empty detection, Receive operation, Receive completion, Receive FIFO fill level /full detection                                                  |

|                         |                             | DMA request                                  | Transmit: Single DMA request, burst DMA request Receive: Single DMA transfer, burst DMA request                                                                                                                                               |

|                         | Special<br>Control          | Final bit hold time of a TSPIxTXD pin        | 2/fsys to 128/fsys                                                                                                                                                                                                                            |

|                         |                             | Output level of TSPIxTXD during an idle term | High, Low, a last bit data hold, Hi-z                                                                                                                                                                                                         |

|                         |                             | Software reset                               | Reset by software is possible.                                                                                                                                                                                                                |

## 9. Sample Program

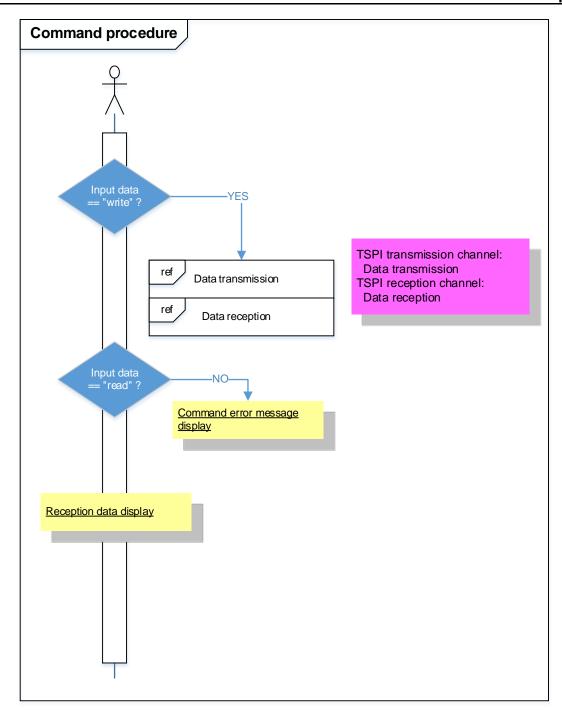

The TSPI is used to communicate data. The "write" command transmits data. And the "read" command reads the reception data and outputs to the terminal software.

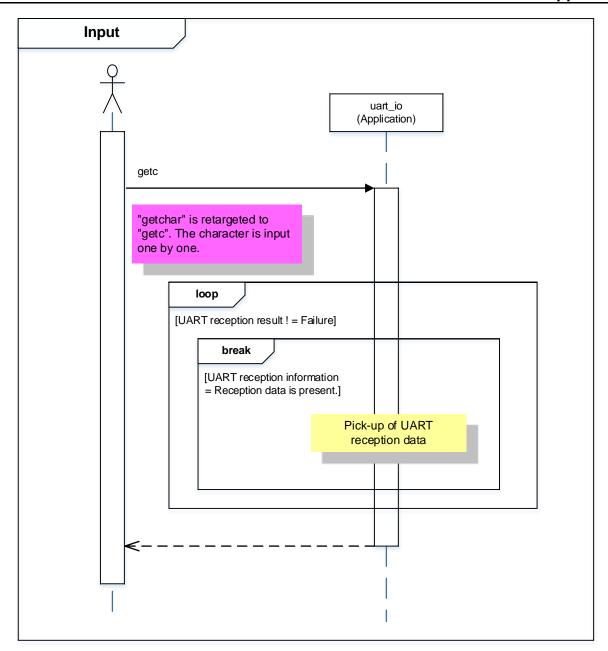

The UART communication is used to transfer the commands and data to the terminal software.

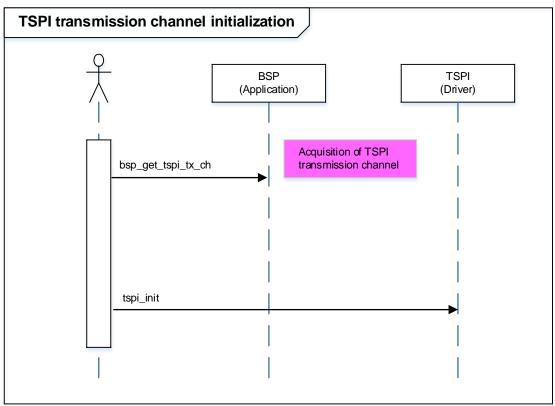

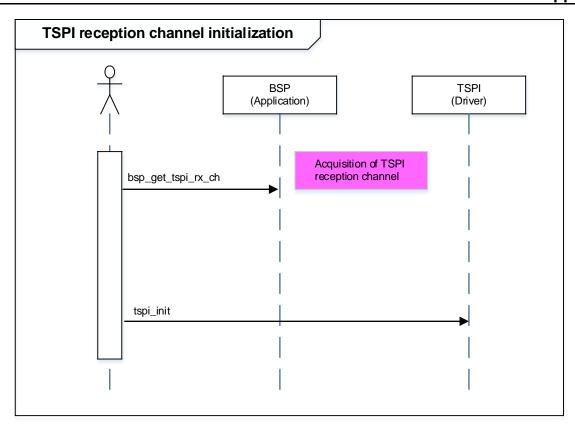

#### 9.1. Initialization

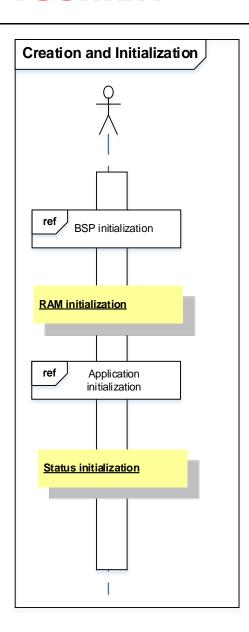

The following initialization is done after power is supplied.

The initialization of each clock setting and the setting of the watchdog timer are done.

#### 9.2. Sample Program Main Operation

The BSP (Board Support Package) is initialized.

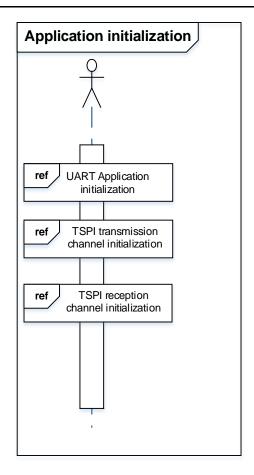

As initialization of the application software, the initialization of the transmission and reception for the UART and the TSPI is done.

The sample program waits for the "write" or "read" command which is input with the terminal software.

The execution of each command is as follows;

#### write

After the TSPI transmission and reception interrupts are enabled, the preset character string "TOSHIBA" is transmitted. After the data is transmitted, the TSPI ch4 reception interrupt is generated, and the data is received.

#### read

The reception data is read and output to the terminal software.

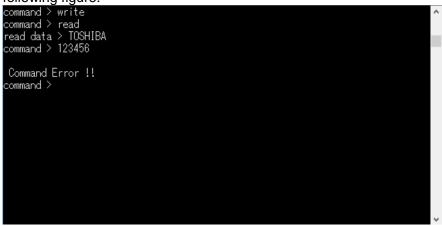

### 9.3. Output Example of Sample Program

When the sample program executes, the command input and its result are displayed as shown in the following figure.

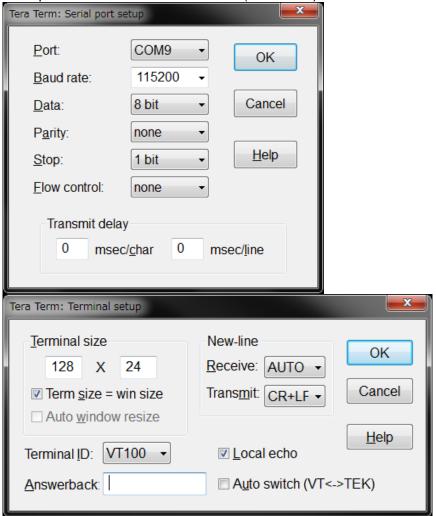

#### 9.3.1. Setting Example of Terminal Software

The operation of the terminal software (Tera Term) has been checked with the following settings.

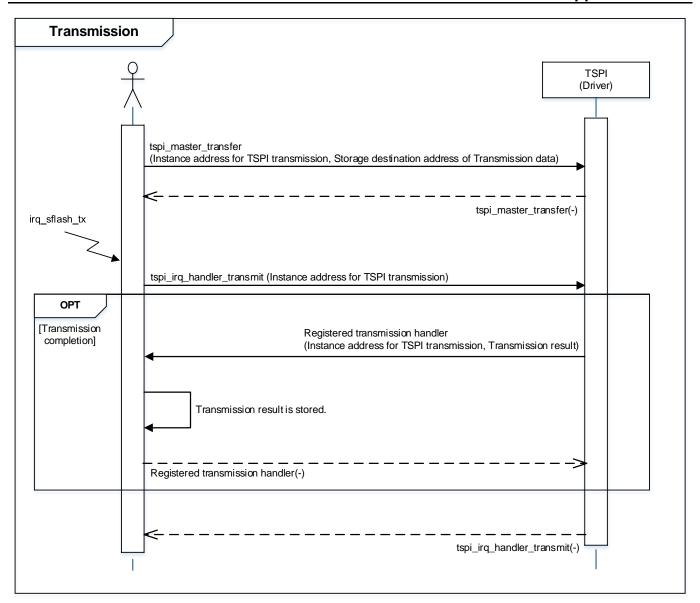

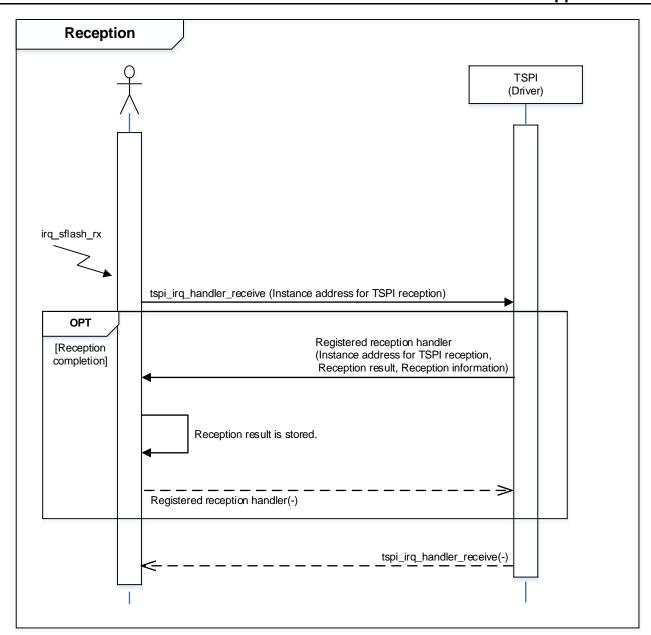

## 9.4. Operating Flow of Sample Program

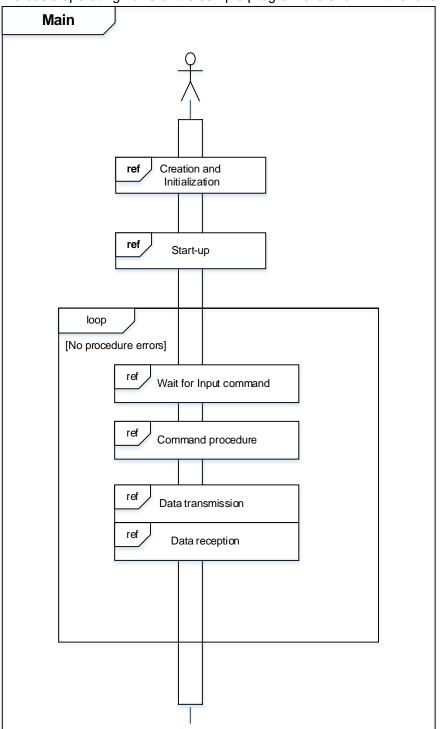

The basic operating flows of the sample program are shown in the following;

## 10. Precaution

When using the sample program with CPU other than TMPM4G9F15, please check operation sufficiently.

# 11. Revision History

| Rev | Date       | Page | Description   |

|-----|------------|------|---------------|

| 1.0 | 2018-12-14 | -    | First release |

#### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- · TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY

HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF

HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for

specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities,

equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships

and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and

escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR

PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our website.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any

infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any

intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR

PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER,

INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING

WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2)

DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR

INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE,

ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the

design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass

destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations

including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export

and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and

regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please

use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without

limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF

NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION

https://toshiba.semicon-storage.com/