# 32-Bit RISC Microcontroller

# TMPM4L Group(1)

Reference Manual Exception (EXCEPT-M4L(1))

**Revision 1.1**

2019-06

**TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

# Contents

| Preface                                                                         | 5  |

|---------------------------------------------------------------------------------|----|

| Related document                                                                | 5  |

| Conventions                                                                     | 6  |

| Terms and Abbreviations                                                         | 8  |

| 1. Outlines                                                                     | 9  |

| 1.1. Exception Types                                                            | 9  |

| 1.2. Exception Handling Flowchart                                               | 10 |

| 1.2.1. Exception Request and Detection                                          | 10 |

| 1.2.2. Exception Handling and Branch to Interrupt Service Routine (Pre-emption) | 12 |

| 1.2.3. Executing an ISR                                                         | 14 |

| 1.2.4. Exception Exit                                                           | 14 |

| 2. Reset Exception                                                              | 15 |

| 3. SysTick                                                                      | 15 |

| 4. Interrupts                                                                   | 16 |

| 4.1. Non-Maskable Interrupt (NMI)                                               | 16 |

| 4.2. Maskable Interrupt                                                         | 16 |

| 4.3. Interrupt Request                                                          | 16 |

| 4.3.1. Interrupt Route                                                          | 16 |

| 4.3.2. Interrupt Request Generation                                             | 18 |

| 4.3.3. Monitor of the Interrupt Request                                         | 19 |

| 4.3.4. Transmission of Interrupt Request                                        | 19 |

| 4.3.5. Precautions When Using External Interrupt Pins                           | 19 |

| 4.4. List of Interrupt Sources                                                  | 20 |

| 4.5. Interrupt detection level                                                  | 23 |

| 4.5.1. Precautions When Releasing the Low Power Consumption Mode                | 23 |

| 4.6. Interrupt Handling                                                         | 24 |

| 4.6.1. Flowchart                                                                | 24 |

| 4.6.2. Preparation                                                              | 25 |

| 4.6.3. Detection(INTIF)                                                         | 27 |

| 4.6.4. Detection(CPU)                                                           |    |

| 4.6.5. CPU Processing                                                           | 27 |

| 4.6.6. Interrupt Service Routine (ISR) (Clearing an interrupt Source)           |    |

| 5. Exception/ Interrupt-Related Registers                                       |    |

| 5.1. Register List                                                              |    |

| 5.2. Interrupt Control Registers A                                              | 32 |

| 5.2.1. [IANIC00] (Non-Maskable Interrupt A Control Register 00)                 | 32 |

| 5.3. Interrupt Control Registers B                                              | 32 |

| 5.3.1. [IBNIC00] (Non-Maskable Interrupt B Control Register 00)                 | 32 |

| 5.3.2. [IBIMC000 to 043] (Interrupt B Mode Control Registers n)                 |    |

| 5.4. Reset Flag Registers                                                       | 34 |

| 5.4.1. [RLMRSTFLG0] (Reset Flag Register 0)                       | 34 |

|-------------------------------------------------------------------|----|

| 5.4.2. [RLMRSTFLG1] (Reset Flag Register 1)                       | 35 |

| 5.5. Interrupt Monitor Registers                                  | 36 |

| 5.5.1. [IMNFLGNMI] (Non-Maskable Interrupt Monitor Flag Register) | 36 |

| 5.5.2. [IMNFLG3] (Interrupt Monitor Flag Register 3)              | 36 |

| 5.5.3. [IMNFLG4] (Interrupt Monitor Flag Register 4)              | 39 |

| 5.6. NVIC Registers                                               | 40 |

| 5.6.1. SysTick Control and Status Register                        | 40 |

| 5.6.2. SysTick Reload Value Register                              | 40 |

| 5.6.3. SysTick Current Value Register                             | 40 |

| 5.6.4. SysTick Calibration Value Register                         | 40 |

| 5.6.5. Interrupt Control Registers                                | 41 |

| 5.6.5.1. Interrupt Set-Enable Register                            | 41 |

| 5.6.5.2. Interrupt Clear-Enable Register                          | 43 |

| 5.6.5.3. Interrupt Set-Pending Register                           | 45 |

| 5.6.5.4. Interrupt Clear-Pending Register                         | 47 |

| 5.6.6. Interrupt Priority Register                                | 49 |

| 5.6.7. Vector Table Offset Register                               | 50 |

| 5.6.8. Application Interrupt and Reset Control Register           | 51 |

| 5.6.9. System Handler Priority Register                           | 52 |

| 5.6.10. System Handler Control and State Register                 | 53 |

| 6. List of Interrupt Sources for Each Product                     | 54 |

| 6.1. TMPM4L2/TMPM4L1                                              | 54 |

| 7. Revision History                                               | 57 |

| RESTRICTIONS ON PRODUCT USE                                       | 58 |

#### List of Figures List of Tables Exception Types and Priority .......11 Table 1.1 Table 1.2 Table 4.1 Table 4.2 Table 4.3 List of Interrupt Sources (Interrupt Control Register B(2)) (1/3) ......21 Table 4.4 Table 4.5 Table 4.6 Table 7.1

# **Preface**

# **Related document**

| Document name                                        |

|------------------------------------------------------|

| Power supply and reset operation                     |

| Oscillation Frequency Detector                       |

| Clock Selective Watchdog Timer                       |

| Voltage Detection Circuit                            |

| Clock Control and Operation Mode                     |

| Arm® Cortex®-M4 Processor Technical Reference Manual |

#### **Conventions**

• Numeric formats follow the rules as shown below:

Hexadecimal: 0xABC

Decimal: 123 or 0d123 – Only when it needs to be explicitly shown that they are decimal numbers.

Binary: 0b111 – It is possible to omit the "0b" when the number of bit can be distinctly understood from a sentence.

- "\_N" is added to the end of signal names to indicate low active signals.

- It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

- When two or more signal names are referred, they are described like as [m: n].

Example: S[3: 0] shows four signal names S3, S2, S1 and S0 together.

• The characters surrounded by [ ] defines the register.

Example: [ABCD]

• "n" substitutes suffix number of two or more same kind of registers, fields, and bit names.

Example:  $[XYZ1], [XYZ2], [XYZ3] \rightarrow [XYZn]$

• "x" substitutes suffix number or character of units and channels in the Register List.

In case of unit, "x" means A, B, and C ...

Example: [ADACR0], [ADBCR0],  $[ADCCR0] \rightarrow [ADxCR0]$

In case of channel, "x" means 0, 1, and 2 ...

Example:  $[T32A0RUNA], [T32A1RUNA], [T32A2RUNA] \rightarrow [T32AxRUNA]$

• The bit range of a register is written like as [m: n].

Example: Bit[3: 0] expresses the range of bit 3 to 0.

• The configuration value of a register is expressed by either the hexadecimal number or the binary number.

Example: [ABCD]<EFG>=0x01 (hexadecimal), [XYZn]<VW>=1 (binary)

• Word and Byte represent the following bit length.

Byte: 8 bits

Half word: 16 bits

Word: 32 bits

Double word: 64 bits

• Properties of each bit in a register are expressed as follows:

R: Read only W: Write only

R/W: Read and Write are possible

- Unless otherwise specified, register access supports only word access.

- The register defined as reserved must not be rewritten. Moreover, do not use the read value.

- The value read from the bit having default value of "—" is unknown.

- When a register containing both of writable bits and read-only bits is written, read-only bits should be written with their default value, in the cases that default is "—", follow the definition of each register.

- Reserved bits of the Write-only register should be written with their default value. In the cases that default is "—", follow the definition of each register.

- Do not use read-modified-write processing to the register of a definition which is different by writing and read out.

Arm, Cortex and Thumb are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

The Flash memory uses the Super Flash® technology under license from Silicon Storage Technology, Inc. Super Flash® is registered trademark of Silicon Storage Technology, Inc.

All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

#### **Terms and Abbreviations**

Some of abbreviations used in this document are as follows:

ADC Analog to Digital Converter

A-ENC32 Advanced Encoder input Circuit (32-bit)

A-VE Advanced Vector Engine

IA Interrupt control register A

IB Interrupt control register B

IMCxx Interrupt Mode Control xx

IMNFLGNMI Interrupt Monitor Flag NMI

IMNFLGX Interrupt Monitor Flag x

INT Interrupt

INTIF Interrupt Interface Logic

ISR Interrupt Service Routine

LVD Voltage Detection Circuit

NICxx Non-Maskable Interrupt Control xx NVIC Nested Vectored Interrupt Controller OFD Oscillation Frequency Detector

PMD+ Programmable Motor Control Circuit Plus

POR Power On Reset Circuit

RAMP RAM parity

RLMRSTFLGx RLM Reset Flag x

SIWDT Clock Selective Watchdog Timer

TSPI Toshiba Serial Peripheral Interface

T32A 32-bit Timer Event Counter

UART Universal Asynchronous Receiver Transmitter

Exceptions have close relation to the CPU core. Refer to "Arm® Cortex®-M4 Processor Technical Reference Manua" if needed.

# 1. Outlines

Exceptions require CPU to suspend the currently executing process, and to start another process.

There are two types of exceptions: those that are generated when some error condition occurs or when an instruction to generate an exception is executed; and those that are generated by hardware, such as an interrupt request signal from an external pin or peripheral function.

All exceptions are handled by the Nested Vectored Interrupt Controller (NVIC) in the CPU according to the respective priority levels. When an exception occurs, the CPU stores the current state to the stack and branches to the corresponding interrupt service routine (ISR). Upon completion of the ISR, the information stored to the stack is automatically restored.

# 1.1. Exception Types

The following types of exceptions exist in this product.

For detailed descriptions on each exception, refer to "Arm Cortex-M4 Processor Technical Reference Manual".

- Reset

- Non-Maskable Interrupt(NMI)

- Hard Fault

- Memory Management

- Bus Fault

- Usage Fault

- SVCall (Supervisor Call)

- Debug Monitor

- PendSV

- SysTick

- External Interrupt

# 1.2. Exception Handling Flowchart

The following shows how an exception/interrupt is handled. In the following descriptions, exception handling by hardware and that by software are explained.

Each step is described later in this reference manual.

| Process                | Description                                                            | See            |

|------------------------|------------------------------------------------------------------------|----------------|

| Detection by INTIF/CPU | The INTIF/CPU detects the exception request.                           | Section 1.2.1. |

|                        |                                                                        |                |

| Handling by CPU        | The CPU handles the exception request.                                 | Section 1.2.2. |

| $\overline{\Box}$      |                                                                        |                |

| Branch to ISR          | The CPU branches to the corresponding interrupt service routine (ISR). | Section 1.2.2. |

| $\bigcirc$             |                                                                        |                |

| Execution of ISR       | Necessary processing is executed                                       | Section 1.2.3. |

| $\Box$                 |                                                                        |                |

| Return from exception  | The CPU branches to another ISR or returns to the previous program.    | Section 1.2.4. |

# 1.2.1. Exception Request and Detection

#### (1) Exception Occurrence

Exception sources include instruction execution by the CPU, memory accesses, and interrupt requests from external interrupt pins or peripheral functions.

An exception by the instruction execution occurs when the CPU executes an instruction that causes an exception or when an error condition occurs during instruction execution.

An exception also occurs by an instruction fetch from the Execute Never region or an access violation to the Fault region.

The request of the exception by the external interrupt pin or the peripheral function occurs by each functional factor. Regarding to interrupt which connected via INTIF, the setup of the interrupt control register is also needed. For details, refer to the chapter, "4.Interrupts".

#### (2) Exception Detection

If multiple exceptions occur simultaneously, the CPU takes the exception with the highest priority.

Table 1.1 shows the priority of exceptions. "Configurable" means that you can assign a priority level to that exception. Memory Management, Bus Fault and Usage Fault exceptions can be enabled or disabled. If a disabled exception occurs, it is handled as Hard Fault.

| <b>Exception Type</b>     | Priority     | Description                                                                                          | Offset      |

|---------------------------|--------------|------------------------------------------------------------------------------------------------------|-------------|

| Reset                     | -3(highest)  | Reset pin, POR reset, OFD reset, SIWDT reset, LVD reset, SYSRESETREQ reset, LOCKUP reset             | 0x00        |

| Non-Maskable<br>Interrupt | -2           | SIWDT, LVD                                                                                           | 0x08        |

| Hard Fault                | -1           | Fault that cannot activate because a higher-priority fault is being handled or it is disabled        | 0x0C        |

| Memory<br>Management      | Configurable | Exception from the Memory Protection Unit (MPU) Instruction fetch from the Execute Never (XN) region | 0x10        |

| Bus Fault                 | Configurable | Access violation to the Hard Fault region of the memory map                                          | 0x14        |

| Usage Fault               | Configurable | Undefined instruction execution or other faults related to instruction execution                     | 0x18        |

| Reserved                  | _            | _                                                                                                    | 0x1C - 0x28 |

| SVCall                    | Configurable | System service call with SVC instruction                                                             | 0x2C        |

| Debug Monitor             | Configurable | Debug monitor when the CPU is not faulting                                                           | 0x30        |

| Reserved                  | _            | _                                                                                                    | 0x34        |

| PendSV                    | Configurable | Pending system service request                                                                       | 0x38        |

| SysTick                   | Configurable | Notification from system timer                                                                       | 0x3C        |

| External Interrupt        | Configurable | External interrupt pin or peripheral function (Note)                                                 | 0x40        |

**Table 1.1 Exception Types and Priority**

Note: External interrupts have different sources and numbers in each product. For details, see "4.4.List of Interrupt Sources".

### (3) Priority Setting

#### Priority Level

The external interrupt priority is set to the Interrupt Priority Register and other exceptions are set to <PRI n> bit in the System Handler Priority Register.

The configuration <PRI\_n> can be changed, and the number of bits required for setting the priority varies from 3 bits to 8 bits depending on products. Thus, the range of priority values you can specify is different depending on products.

In the case of 8-bit configuration, the priority can be configured in the range from 0 to 255. The highest priority is "0". If multiple elements with the same priority exist, the smaller the number, the higher the priority becomes.

<PRI\_n[7:0]> bit is defined as the upper 4-bit configuration with TMPM4L Group(1) products. The priority can be configured in the range from 0 to 15.

#### Priority Grouping

The priority group can be split into groups. By setting the <PRIGROUP> of the Application Interrupt and Reset Control Register, <PRI\_n> can be divided into the pre-emption priority and the sub priority. A priority is compared with the pre-emption priority. If the priority is the same as the pre-emption priority, then it is compared with the sub priority. If the sub priority is the same as the priority, the

smaller the exception number, the higher the priority.

The Table 1.2 shows the priority group setting. The pre-emption priority and the sub priority in the table are the number in the case that <PRI\_n> is defined as an 8-bit configuration.

Table 1.2 Priority grouping setting

| *DDICDOUD[3:0]                          | <pri_n[7:0]> Number of Number of</pri_n[7:0]> |                    | Number of sub          |            |  |

|-----------------------------------------|-----------------------------------------------|--------------------|------------------------|------------|--|

| <prigroup[2:0]> setting</prigroup[2:0]> | Pre-emption field                             | Sub priority field | pre-emption priorities | priorities |  |

| 000                                     | [7:1]                                         | [0]                | 128                    | 2          |  |

| 001                                     | [7:2]                                         | [1:0]              | 64                     | 4          |  |

| 010                                     | [7:3]                                         | [2:0]              | 32                     | 8          |  |

| 011                                     | [7:4]                                         | [3:0]              | 16                     | 16         |  |

| 100                                     | [7:5]                                         | [4:0]              | 8                      | 32         |  |

| 101                                     | [7:6]                                         | [5:0]              | 4                      | 64         |  |

| 110                                     | [7]                                           | [6:0]              | 2                      | 128        |  |

| 111                                     | None                                          | [7:0]              | 1                      | 256        |  |

Note: If the configuration of <PRI\_n> is less than 8 bits, the lower bit is "0". For the example in the case of 4-bit configuration, the priority is set as <PRI\_n[7:4]> and <PRI\_n[3:0]> is "0000".

# 1.2.2. Exception Handling and Branch to Interrupt Service Routine (Pre-emption)

When an exception occurs, the CPU suspends the currently executing process and branches to the interrupt service routine. This is called "pre-emption".

# (1) Stacking

When the CPU detects an exception, it pushes the contents of the following eight registers to the stack in the following order:

- 1. Program Counter (PC)

- 2. Program Status Register (xPSR)

- 3. r0 to r3

- 4. r12

- 5. Link Register (LR)

The SP is decremented by eight words by the completion of the stack push. The following shows the state of the stack after the register contents have been pushed.

| Old SP→ | <pre><previous></previous></pre> |

|---------|----------------------------------|

|         | xPSR                             |

|         | PC                               |

|         | LR                               |

|         | r12                              |

|         | r3                               |

|         | r2                               |

|         | r1                               |

| SP→     | r0                               |

#### (2) Fetching an ISR

The CPU performs the evacuation of the register. In addition, the CPU performs instruction fetch of the interrupt service routine at the same time.

Prepare a vector table containing the top addresses of ISRs for each exception. After reset, the vector table is located at address 0x00000000 in the Code area. By setting the Vector Table Offset Register, you can place the vector table at any address in the Code or SRAM space.

The vector table should also contain the initial value of the main stack.

#### (3) Late-arriving

If the CPU detects a higher priority exception before executing the ISR for a previous exception, the CPU handles the higher priority exception first. This is called "late-arriving".

A late-arriving exception causes the CPU to fetch a new vector address for branching to the corresponding ISR, but the CPU does not newly push the register contents to the stack.

#### (4) Vector Table

The vector table is configured as shown below.

You must always set the first four words (stack top address, reset ISR address, NMI ISR address, and Hard Fault ISR address). Set ISR addresses for other exceptions if necessary.

For other exceptions, you may prepare the ISR addresses if necessary.

| Offset       | Exception              | Contents                        | Setting  |

|--------------|------------------------|---------------------------------|----------|

| 0x00         | Reset                  | Initial value of the main stack | Required |

| 0x04         | Reset                  | ISR address                     | Required |

| 0x08         | Non-Maskable Interrupt | ISR address                     | Required |

| 0x0C         | Hard Fault             | ISR address                     | Required |

| 0x10         | Memory Management      | ISR address                     | Optional |

| 0x14         | Bus Fault              | ISR address                     | Optional |

| 0x18         | Usage Fault            | ISR address                     | Optional |

| 0x1C to 0x28 | Reserved               | _                               | _        |

| 0x2C         | SVCall                 | ISR address                     | Optional |

| 0x30         | Debug Monitor          | ISR address                     | Optional |

| 0x34         | Reserved               | _                               | _        |

| 0x38         | PendSV                 | ISR address                     | Optional |

| 0x3C         | SysTick                | ISR address                     | Optional |

| 0x40         | External Interrupt     | ISR address                     | Optional |

# 1.2.3. Executing an ISR

An ISR performs necessary processing for the corresponding exception. ISRs must be prepared by the user.

An ISR may need to include code for clearing the interrupt request so that the same interrupt will not occur again upon return to normal program execution.

For details about interrupt handling, see "4.Interrupts".

If a higher priority exception occurs during ISR execution for the current exception, the CPU abandons the currently executing ISR and services the newly detected exception.

### 1.2.4. Exception Exit

#### (1) Execution after Returning from ISR

When returning from an ISR, the CPU takes one of the following actions:

Tail-chaining

If a pending exception exists and there are no stacked exceptions or the pending exception has higher priority than all stacked exceptions, the CPU returns to the ISR of the pending exception. In this case, the CPU skips the pop of eight registers and push of eight registers when exiting one ISR and entering another. This is called "tail-chaining".

- Returning to the last stacked ISR

- If there are no pending exceptions or if the highest priority stacked exception is of higher priority than the highest priority pending exception, the CPU returns to the last stacked ISR.

- Returning to the previous program

If there are no pending or stacked exceptions, the CPU returns to the previous program.

#### (2) Exception Exit Sequence

When returning from an ISR, the CPU performs the following operations:

- Pop eight registers

Pop eight registers (PC, xPSR, r0 to r3, r12, and LR) from the stack and adjust the SP.

- Load current active interrupt number

Loads the current active interrupt number from the stacked xPSR. The CPU uses this to track which interrupt to return to.

- Select SP

If returning to an exception (Handler Mode), SP is SP\_main. If returning to Thread Mode, SP can be SP\_main or SP\_process.

# 2. Reset Exception

Reset exceptions are generated from the following seven sources.

Use the [RLMRSTFLGn] of the Reset Flag Register to identify the source of a reset.

Reset exception by external reset pin

A reset exception occurs when an external reset pin changes from "Low" level to "High" level.

Reset exception by POR

A reset exception occurs by POR. For details, refer to reference manual "Power supply and Reset operation"

Reset exception by OFD

A reset exception occurs by OFD. For details, refer to reference manual "Oscillation Frequency Detector".

Reset exception by SIWDT

The watchdog timer (SIWDT) has a reset generating feature. For details, refer to reference manual "Clock Selective Watchdog Timer".

Reset exception by LVD

The LVD has a reset generating feature. For details, refer to reference manual "Voltage Detector Circuit".

Reset exception by <SYSRESETREQ>

A reset can be generated by setting the <SYSRESETREQ> bit in the NVIC's Application Interrupt and Reset Control Register.

Reset exception by LOCKUP signal

A reset can be generated by the LOCKUP signal which can be output from the CPU when the un-recoverable interrupt occurs. For details on the LOCKUP signal, please refer to "Arm Cortex-M4 Processor Technical Reference Manual".

# 3. SysTick

SysTick provides interrupt features using the CPU's system timer.

When you set a value in the SysTick Reload Value Register and enable the SysTick features in the SysTick Control and Status Register, the counter loads with the value set in the Reload Value Register and begins counting down. When the counter reaches "0", a SysTick exception occurs. You may be pending exceptions and use a flag to know when the timer reaches "0".

# 4. Interrupts

This chapter explains the route from which a factor and an interrupt request are transmitted, and a required setup.

# 4.1. Non-Maskable Interrupt (NMI)

Non-maskable interrupts are generated from the following two sources.

- Non-maskable interrupt by SIWDT

The watchdog timer (SIWDT) has a non-maskable interrupt generating feature. For details of SIWDT, refer to reference manual "Clock Selective Watchdog Timer".

- Non-maskable interrupt by LVD

The LVD has a non-maskable interrupt generating feature. For details of LVD, refer to reference manual "Voltage Detector Circuit".

# 4.2. Maskable Interrupt

Please refer to interrupt control register A / interrupt control register B of the "4.4.List of Interrupt Sources" for the factor of maskable interrupt.

# 4.3. Interrupt Request

The CPU is notified of interrupt requests by the interrupt signal from each interrupt source. It sets priority on interrupts and handles an interrupt request with the highest priority.

### 4.3.1. Interrupt Route

The interrupt is available for the cancellation from a low power consumption mode, and a route varies according to a factor.

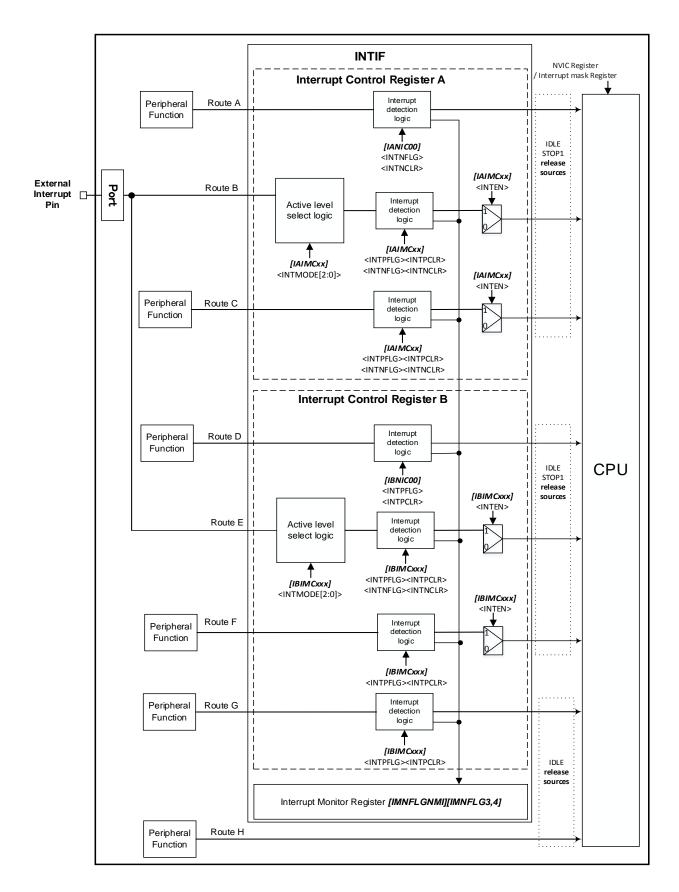

Figure 4.1 shows the interrupt transfer route diagram and Table 4.1 shows the explanation of each interrupt transfer route.

- The interrupt that is releasable from IDLE, STOP1 mode

It has two interrupt transfer routes via INTIF that can release IDLE and STOP 1 mode.

- (1) It is controlled by interrupt control register A in INTIF, and notified to CPU. (Route A, B, C)

- (2) It is controlled by interrupt control register B in INTIF, and notified to CPU. (Route D, E, F)

- The interrupt that is releasable from IDLE mode Although some factors of interrupt which can be released of IDLE mode are controlled by the interrupt control register B via INTIF (Route G), other factors are notified to CPU directly (Route H) not passing through INTIF.

When the interrupt factor that went by way of an interrupt regardless of low power consumption mode cancellation is used, setting of interrupt control register A or B is necessary.

Please refer to the chapter of "Release sources of a Low Power Consumption mode" of a reference manual "Clock

Control and Operation Mode" for the details of a low power consumption mode release factor.

Figure 4.1 Interrupt transfer route Diagram

|       | Table 4.1 Explanation of each interrupt transfer route |                                                                        |                                                                                                                                                                                                                                                                         |  |  |

|-------|--------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Route | Interrupt<br>No.                                       | Interrupt Request                                                      | Route Description                                                                                                                                                                                                                                                       |  |  |

| А     | _                                                      | LVD interrupt                                                          | This route is NMI interrupt. It is a route inputted into CPU via INTIF. An interrupt release setup is carried out by the interrupt control register A ( <i>[IANIC00]</i> ).                                                                                             |  |  |

| В     | _                                                      | _                                                                      | The interrupt request of a port is a route inputted into CPU via INTIF.  Permission/prohibition of selection of an Interrupt detection level, interrupt release, and an interrupt request are set up by the interrupt control register A ([IAIMCxx]) for every factor.  |  |  |

| С     | _                                                      | _                                                                      | It is a route inputted into CPU via INTIF.  Permission/prohibition of interrupt release and an interrupt request are set up by the interrupt control register A ([IAIMCxx]) for every factor.                                                                           |  |  |

| D     | _                                                      | WDT interrupt                                                          | It is mask impossible interrupt. It is a route inputted into CPU via INTIF. An interrupt release setup is carried out by the interrupt control register B ( <i>[IBNIC00]</i> ).                                                                                         |  |  |

| E     | 0 to 7                                                 | External interrupts (00 to 07)                                         | The interrupt request of a port is a route inputted into CPU via INTIF.  Permission/prohibition of selection of an Interrupt detection level, interrupt release, and an interrupt request are set up by the interrupt control register B ([IBIMCxxx]) for every factor. |  |  |

| F     | 8 to 23                                                | T32A timer match, overflow, underflow interrupt T32A capture interrupt | It is a route inputted into CPU via INTIF.  Permission/prohibition of interrupt release and an interrupt request are set up by the interrupt control register B ([IBIMCxxx]) for every factor.                                                                          |  |  |

| G     | _                                                      | _                                                                      | It is a route inputted into CPU via INTIF.  An interrupt release setup is carried out by the interrupt control register B ([IBIMCxxx]) for every factor.                                                                                                                |  |  |

| Н     | 24 to 58                                               | Other interrupts (Note)                                                | It is a route as which an interrupt request is directly inputted into CPU not passing through INTIF.                                                                                                                                                                    |  |  |

Table 4.1 Explanation of each interrupt transfer route

Note: For the details of other interrupts, refer to "4.4.List of Interrupt Sources".

# 4.3.2. Interrupt Request Generation

An interrupt request is generated from an external interrupt pin or peripheral function which are assigned as interrupt request sources, or by setting the relevant bit of NVIC's Interrupt Set-Pending Register for interrupt request source.

- Interrupt from external interrupt pin

Set the port control register so that the external pin can perform as an interrupt function pin.

- Interrupt from peripheral function

Set the peripheral function to make it possible to output interrupt requests.

See the chapter of each peripheral function for details.

- By setting Interrupt Set-Pending Register (forced pending)

An interrupt request can be forced to be generated by setting the relevant bit of the Interrupt Set-Pending Register of NVIC.

CPU will recognize the "High" level of the interrupt request as an interrupt.

# 4.3.3. Monitor of the Interrupt Request

INTIF has the interrupt monitor flags. It can know that the interrupt request has occurred by monitoring the flag. If one request source is representing several interrupt requests, Interrupt Monitor Register can be used to identify the actual interrupt request source.

For detail, please refer to "4.4.List of Interrupt Sources".

#### 4.3.4. Transmission of Interrupt Request

An interrupt request which is not passing through the Interrupt Control Register will be directly input to the CPU. The interrupts connected to the CPU through INTIF, which are used as interrupt request sources for releasing the low power consumption mode, will need proper setting of the Interrupt Control Register in INTIF. A "High" level interrupt signal will be sent to the CPU, when the interrupt is used to release the low power consumption mode.

Please setup an interrupt detection level and interrupt detection enable/disable by INTIF.

By the way, please be cautious about external interrupt pin as in the next section.

### 4.3.5. Precautions When Using External Interrupt Pins

When you use external interrupt, please care about the following points so that an unexpected interrupt does not occur.

If input is disabled (*[PxIE]*<PxmIE>=0), inputs from external interrupt pins are "Low" level. When the <INTMODE> bit of Interrupt Control Register A (*[IAIMCxx]*) is "Low" level, then input signals from the external interrupt pins are sent to the CPU as is. Since the CPU recognizes "Low" level input as an interrupt, interrupts occur if corresponding interrupts are enabled by the CPU as inputs are being disabled.

To use the external interrupt without setting it as a trigger to release the low power consumption mode, set the interrupt pin input as "High" level and enable it. Then, enable interrupts on the CPU.

# 4.4. List of Interrupt Sources

Table 4.2 shows the list of interrupt sources of non-maskable interrupts. The setting for clearing the NMI sources can be done by Interrupt Control Registers A and B.

**Interrupt Control Interrupt Monitor Interrupt Source** Interrupt Request Register Register [IMNFLGNMI] INTLVD LVD interrupt [IANIC00] <INT000FLG> [IMNFLGNMI] INTWDT0 WDT interrupt [IBNIC00] <INT016FLG>

Table 4.2 List of Interrupt Sources (Non-Maskable Interrupt)

Table 4.3 shows the list of interrupt sources of Interrupt Control Register B. These interrupt sources can be the sources for releasing the low power consumption mode. The Interrupt Control Register B will perform several setting for detecting the release of the low power consumption mode, and interrupt detection enable/disable.

| rable 7.5 List of interrupt oources (interrupt control Negister D( i) | Table 4.3 | List of Interrupt Sources | (Interrupt Control Register B(1) | )) |

|-----------------------------------------------------------------------|-----------|---------------------------|----------------------------------|----|

|-----------------------------------------------------------------------|-----------|---------------------------|----------------------------------|----|

| Interrupt<br>No. | Interrupt Source | Interrupt Request     | Interrupt Control<br>Register | Interrupt Monitor<br>Register               |

|------------------|------------------|-----------------------|-------------------------------|---------------------------------------------|

| 0                | INT00            | External interrupt 00 | [IBIMC000]                    | <i>[IMNFLG3]</i><br><int096flg></int096flg> |

| 1                | INT01            | External interrupt 01 | [IBIMC001]                    | <i>[IMNFLG3]</i><br><int097flg></int097flg> |

| 2                | INT02            | External interrupt 02 | [IBIMC002]                    | [IMNFLG3]<br><int098flg></int098flg>        |

| 3                | INT03            | External interrupt 03 | [IBIMC003]                    | [IMNFLG3]<br><int099flg></int099flg>        |

| 4                | INT04            | External interrupt 04 | [IBIMC004]                    | [IMNFLG3]<br><int100flg></int100flg>        |

| 5                | INT05            | External interrupt 05 | [IBIMC005]                    | [IMNFLG3]<br><int101flg></int101flg>        |

| 6                | INT06            | External interrupt 06 | [IBIMC006]                    | [IMNFLG3]<br><int102flg></int102flg>        |

| 7                | INT07            | External interrupt 07 | [IBIMC007]                    | [IMNFLG3]<br><int103flg></int103flg>        |

The factor list of the interrupt control registers B is shown in Table 4.4 to Table 4.6. A part of interrupt sets up interrupt detection enable/disable by the interrupt control register B.

Table 4.4 List of Interrupt Sources (Interrupt Control Register B(2)) (1/3)

| Interrupt<br>No. | Interrupt Source | Interrupt Request                                               | Interrupt Control<br>Register | Interrupt Monitor<br>Register                      |

|------------------|------------------|-----------------------------------------------------------------|-------------------------------|----------------------------------------------------|

| NO.              |                  | Took to d                                                       | ivedistei                     |                                                    |

| 8                | INTT32A00_AT_CT  | T32A ch0 timer A match,overflow, and underflow                  | [IBIMC008]                    | [IMNFLG3]<br><int104flg></int104flg>               |

|                  | N1132A00_A1_C1   | T32A ch0 timer C match,overflow, and underflow                  | [IBIMC009]                    | <i>[IMNFLG3]</i><br><int105flg></int105flg>        |

|                  |                  | T32A ch0 timer A capture 0                                      | [IBIMC010]                    | [IMNFLG3]<br><int106flg></int106flg>               |

| 9                | INTT32A00_A01_C0 | T32A ch0 timer A capture 1                                      | [IBIMC011]                    | [IMNFLG3]<br><int107flg></int107flg>               |

|                  |                  | T32A ch0 timer C capture 0                                      | [IBIMC012]                    | [IMNFLG3]<br><int108flg></int108flg>               |

| 10               | INTT32A00_BT_C1  | T32A ch0 timer B match,overflow, and underflow                  | [IBIMC013]                    | <i>[IMNFLG3]</i><br><int109flg></int109flg>        |

| 10               | INT 102A00_B1_C1 | T32A ch0 timer C capture 1                                      | [IBIMC014]                    | [IMNFLG3]<br><int110flg></int110flg>               |

| 11               | INTT32A00_B01    | T32A ch0 timer B capture 0                                      | [IBIMC015]                    | [IMNFLG3]<br><int111flg></int111flg>               |

| 11               | IIV1132A00_B01   | T32A ch0 timer B capture 1                                      | [IBIMC016]                    | <i>[IMNFLG3]</i><br><int112flg></int112flg>        |

| 12               | INTT32A01_AT_CT  | T32A ch1 timer A match,overflow, and underflow                  | [IBIMC017]                    | <i>[IMNFLG3]</i><br><int113flg></int113flg>        |

| 12               | N1132A01_A1_C1   | T32A ch1 timer C match,overflow, and underflow                  | [IBIMC018]                    | <i>[IMNFLG3]</i><br><int114flg></int114flg>        |

|                  |                  | T32A ch1 timer A capture 0                                      | [IBIMC019]                    | [IMNFLG3]<br><int115flg></int115flg>               |

| 13               | INTT32A01_A01_C0 | T32A ch1 timer A capture 1                                      | [IBIMC020]                    | [IMNFLG3]<br><int116flg></int116flg>               |

|                  |                  | T32A ch1 timer C capture 0                                      | [IBIMC021]                    | <i>[IMNFLG3]</i><br><int117flg></int117flg>        |

| 14               | INTT32A01_BT_C1  | T32A ch1 timer B match,overflow, and underflow                  | [IBIMC022]                    | [IMNFLG3]<br><int118flg></int118flg>               |

| 17               | INT 132A01_B1_C1 | T32A ch1 timer C capture 1                                      | [IBIMC023]                    | [IMNFLG3]<br><int119flg></int119flg>               |

| 15               | INTT32A01_B01    | T32A ch1 timer B capture 0                                      | [IBIMC024]                    | [IMNFLG3]<br><int120flg></int120flg>               |

|                  | _                | T32A ch1 timer B capture 1                                      | [IBIMC025]                    | [IMNFLG3]<br><int121flg></int121flg>               |

| 16               | INTT32A02_AT_CT  | T32A ch2 timer A match,overflow, and underflow T32A ch2 timer C | [IBIMC026]                    | [IMNFLG3]<br><int122flg><br/>[IMNFLG3]</int122flg> |

|                  |                  | match,overflow, and underflow                                   | [IBIMC027]                    | <pre><int123flg> [IMNFLG3]</int123flg></pre>       |

|                  |                  | T32A ch2 timer A capture 0                                      | [IBIMC028]                    | <pre></pre>                                        |

| 17               | INTT32A02_A01_C0 | T32A ch2 timer A capture 1                                      | [IBIMC029]                    | <pre><int125flg> [IMNFLG3]</int125flg></pre>       |

|                  |                  | T32A ch2 timer C capture 0 T32A ch2 timer B                     | [IBIMC030]                    | <pre><int126flg> [IMNFLG3]</int126flg></pre>       |

| 18               | INTT32A02_BT_C1  | match,overflow, and underflow                                   | [IBIMC031]                    | <pre><int127flg> [IMNFLG4]</int127flg></pre>       |

|                  |                  | T32A ch2 timer C capture 1                                      | [IBIMC032]                    | <pre><int128flg> [IMNFLG4]</int128flg></pre>       |

| 19               | INTT32A02_B01    | T32A ch2 timer B capture 0                                      | [IBIMC033]                    | <pre><int129flg> [IMNFLG4]</int129flg></pre>       |

|                  |                  | T32A ch2 timer B capture 1                                      | [IBIMC034]                    | <int130flg></int130flg>                            |

Table 4.5 List of Interrupt Sources (Interrupt Control Register B(2)) (2/3)

| Interrupt<br>No. | Interrupt Source  | Interrupt Request                                                            | Interrupt Control<br>Register | Interrupt Monitor<br>Register                                     |

|------------------|-------------------|------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------|

| 140.             |                   | T32A ch3 timer A                                                             | [IBIMC035]                    | [IMNFLG4]                                                         |

| 20               | INTT32A03_AT_CT   | match,overflow, and underflow T32A ch3 timer C match,overflow, and underflow | [IBIMC036]                    | <int131flg><br/>[IMNFLG4]<br/><int132flg></int132flg></int131flg> |

|                  |                   | T32A ch3 timer A capture 0                                                   | [IBIMC037]                    | [IMNFLG4]<br><int133flg></int133flg>                              |

| 21               | INTT32A03_A01_C0  | T32A ch3 timer A capture 1                                                   | [IBIMC038]                    | [IMNFLG4]<br><int134flg></int134flg>                              |

|                  |                   | T32A ch3 timer C capture 0                                                   | [IBIMC039]                    | [IMNFLG4]<br><int135flg></int135flg>                              |

| 22               | INTT32A03_BT_C1   | T32A ch3 timer B match,overflow, and underflow                               | [IBIMC040]                    | [IMNFLG4]<br><int136flg></int136flg>                              |

|                  | 11111027100_51_61 | T32A ch3 timer C capture 1                                                   | [IBIMC041]                    | <i>[IMNFLG4]</i><br><int137flg></int137flg>                       |

| 23               | INTT32A03_B01     | T32A ch3 timer B capture 0                                                   | [IBIMC042]                    | [IMNFLG4]<br><int138flg></int138flg>                              |

| 20               | 1111102/103_B01   | T32A ch3 timer B capture 1                                                   | [IBIMC043]                    | <i>[IMNFLG4]</i><br><int139flg></int139flg>                       |

| 24               | INTVCN0           | A-VE ch0 Schedule end interrupt                                              |                               |                                                                   |

| 25               | INTVCT0           | A-VE ch0 Task end interrupt                                                  |                               |                                                                   |

| 26               | INTEMG0           | PMD+ ch0 EMG interrupt                                                       |                               |                                                                   |

| 27               | INTOVV0           | PMD+ ch0 OVV interrupt                                                       |                               |                                                                   |

| 28               | INTPWM0           | PMD+ ch0 PWM interrupt                                                       |                               |                                                                   |

| 29               | INTENC00          | A-ENC32 ch0 Encoder input interrupt 0                                        |                               |                                                                   |

| 30               | INTENC01          | A-ENC32 ch0 Encoder input interrupt 1                                        |                               |                                                                   |

| 31               | _                 | _                                                                            |                               |                                                                   |

| 32               | INTADAPDA         | ADC unitA PMD trigger interrupt A                                            |                               |                                                                   |

| 33               | INTADAPDB         | ADC unitA PMD trigger interrupt B                                            |                               |                                                                   |

| 34               | INTADACP0         | ADC unitA Monitor function 0 interrupt                                       |                               |                                                                   |

| 35               | INTADACP1         | ADC unitA Monitor function 1 interrupt                                       |                               |                                                                   |

| 36               | INTADATRG         | ADC unitA General purpose trigger interrupt                                  |                               |                                                                   |

| 37               | INTADASGL         | ADC unitA Single conversion interrupt                                        |                               |                                                                   |

| 38               | INTADACNT         | ADC unitA Continuous conversion interrupt                                    |                               |                                                                   |

| 39               | INTT0RX           | TSPI ch0 Receive interrupt                                                   |                               |                                                                   |

| 40               | INTT0TX           | TSPI ch0 Transmit interrupt                                                  |                               |                                                                   |

| 41               | INTT0ERR          | TSPI ch0 Error interrupt                                                     |                               |                                                                   |

| 42               | INTT1RX           | TSPI ch1 Receive interrupt                                                   |                               |                                                                   |

| 43               | INTT1TX           | TSPI ch1 Transmit interrupt                                                  |                               |                                                                   |

| 44               | INTT1ERR          | TSPI ch1 Error interrupt                                                     |                               |                                                                   |

|                  | rubic 4.0 List of interrupt courses (interrupt control register b(z)) (6/6) |                                 |                               |                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------------|---------------------------------|-------------------------------|-------------------------------|--|--|--|--|

| Interrupt<br>No. | Interrupt Source                                                            | Interrupt Request               | Interrupt Control<br>Register | Interrupt Monitor<br>Register |  |  |  |  |

| 45               | INTT2RX                                                                     | TSPI ch2 Receive interrupt      |                               |                               |  |  |  |  |

| 46               | INTT2TX                                                                     | TSPI ch2 Transmit interrupt     |                               |                               |  |  |  |  |

| 47               | INTT2ERR                                                                    | TSPI ch2 Error interrupt        |                               |                               |  |  |  |  |

| 48               | INTUART0RX                                                                  | UART ch0 Reception interrupt    |                               |                               |  |  |  |  |

| 49               | INTUART0TX                                                                  | UART ch0 Transmission interrupt |                               |                               |  |  |  |  |

| 50               | INTUART0ERR                                                                 | UART ch0 Error interrupt        |                               |                               |  |  |  |  |

| 51               | INTUART1RX                                                                  | UART ch1 Reception interrupt    |                               |                               |  |  |  |  |

| 52               | INTUART1TX                                                                  | UART ch1 Transmission interrupt |                               |                               |  |  |  |  |

| 53               | INTUART1ERR                                                                 | UART ch1 Error interrupt        |                               |                               |  |  |  |  |

| 54               | INTUART2RX                                                                  | UART ch2 Reception interrupt    |                               |                               |  |  |  |  |

| 55               | INTUART2TX                                                                  | UART ch2 Transmission interrupt |                               |                               |  |  |  |  |

| 56               | INTUART2ERR                                                                 | UART ch2 Error interrupt        |                               |                               |  |  |  |  |

| 57               | INTPARIO                                                                    | RAMP ch0 RAM parity interrupt   |                               |                               |  |  |  |  |

| 58               | INTFLCRDY                                                                   | Code FLASH Ready interrupt      |                               |                               |  |  |  |  |

Table 4.6 List of Interrupt Sources (Interrupt Control Register B(2)) (3/3)

# 4.5. Interrupt detection level

When using interrupt via INTIF, interrupt detection level ("Low" level / "High" level / Rising edge / Falling edge) can be selected by interrupt control register A or B. The detected interrupt is output to the CPU with a "High" level signal.

The interrupt signals which are directly transmitted from the various peripheral functions to the CPU, a "High" pulse is output to the CPU as an interrupt request.

The CPU detects the interrupt signal "High" level to be an interrupt factor.

# 4.5.1. Precautions When Releasing the Low Power Consumption Mode

Following setting should be done when releasing STOP1 mode

- The setup of the interrupt control register B. ( [IBIMCxxx]) Interrupt detection level, Interrupt detection enable/disable

- The setup of the NVIC interrupt enable set register enable/disable setup

In order to return to NORMAL mode from STOP1 mode, resume suspended instruction by jumping into interrupt after high speed clock oscillation.

# 4.6. Interrupt Handling

# 4.6.1. Flowchart

The following shows how an interrupt is handled.

The flowchart below explains the interrupt handling process by hardware and software.

| Processing                                             | Details                                                                                                                                                                                                                                                                                                                                | See                                                 |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Setting for detection                                  | Set the relevant NVIC registers for detecting interrupts.  Setting to INTIF will be necessary when the interrupt detection level setting for releasing the low power consumption mode. <common setting="">  NVIC registers  <setting control="" for="" interrupt="" register="" the="">  INTIF</setting></common>                      | 4.6.2.                                              |

| Setting for sending interrupt signal                   | Execute an appropriate setting to send the interrupt signal depending on the interrupt type. <setting external="" for="" from="" interrupt="" pin=""> Port  <setting for="" from="" function="" interrupt="" peripheral=""> Peripheral function (see the reference manual of each peripheral function for details)</setting></setting> | Preparation                                         |

| Interrupt generation  Interrupt which does not connect | An interrupt request is generated                                                                                                                                                                                                                                                                                                      |                                                     |

| INTIF detect interrupt                                 | It is connected to CPU via INTIF.                                                                                                                                                                                                                                                                                                      | 4.6.3.<br>Detection(INTIF)                          |

| CPU detects interrupt                                  | The CPU detects the interrupt.  If multiple interrupt requests occur simultaneously, the interrupt request with the highest priority is detected according to the priority order.                                                                                                                                                      | 4.6.4.<br>Detection(CPU)                            |

| CPU handles interrupt                                  | The CPU handles the interrupt  The CPU pushes register contents to the stack before entering the ISR.                                                                                                                                                                                                                                  | 4.6.5.<br>CPU Processing                            |

| ISR execution                                          | Program for the ISR<br>Clear the interrupt source if needed                                                                                                                                                                                                                                                                            | 4.6.6. Interrupt Service Routine (ISR) (Clearing an |

| Return to preceding program                            | Configure to return to the preceding program of the ISR                                                                                                                                                                                                                                                                                | interrupt Source)                                   |

# 4.6.2. Preparation

When preparing for an interrupt, you need to pay attention to the order of configuration to avoid any unexpected interrupt on the way.

Initiating an interrupt or changing its configuration must be implemented in the following order basically. First, disable the interrupt by the CPU. Then, configure from the farthest route from the CPU. Finally, enable the interrupt by the CPU.

To configure the INTIF, you must follow the order indicated here not to cause any unexpected interrupt. First, configure the precondition. Secondly, clear the data related to the interrupt in the INTIF and then enable the interrupt.

The following sections are listed in the order of interrupt handling and describe how to configure them.

- 1. Disabling interrupt by CPU

- 2. CPU registers setting

- 3. Preconfiguration (1) (Interrupt from external pin)

- 4. Preconfiguration (2) (Interrupt from peripheral function)

- 5. Preconfiguration (3) (Interrupt Set-Pending Register)

- 6. Configuring the INTIF

- 7. Enabling interrupt by CPU

### (1) Disabling Interrupt by CPU

To make the CPU for not accepting any interrupt, write "1" to the corresponding bit of the *[PRIMASK]* Register. All interrupts and exceptions other than non-maskable interrupts and hard faults can be masked.

Use "MSR" instruction to set this register.

| Interrupt Mask Register |              |                         |

|-------------------------|--------------|-------------------------|

| [PRIMASK]               | <del>(</del> | "1"(interrupt disabled) |

Note 1: [PRIMASK] Register cannot be modified in the user access level

Note 2: If a fault causes when "1" is set to the [PRIMASK] Register, it is treated as a hard fault.

#### (2) CPU Registers Setting

You can assign a priority level by writing to <PRI\_n> field in an Interrupt Priority Register in the NVIC. Each interrupt source is provided with eight bits for assigning a priority level from "0" to "255", but the number of bits actually used varies with each product. Priority level "0" is the highest priority level. If multiple sources have the same priority, the smallest-numbered interrupt source has the highest priority. You can assign grouping priority by using the <PRIGROUP> in the Application Interrupt and Reset Control Register.

| NVIC Register         |              |                                                     |  |  |

|-----------------------|--------------|-----------------------------------------------------|--|--|

| <pri_n></pri_n>       | <b>←</b>     | "Priority"                                          |  |  |

| <prigroup></prigroup> | <del>(</del> | "group priority" (This is configurable if required) |  |  |

Note: "n" indicates the number of the corresponding exceptions/interrupts.

This product uses four bits for assigning a priority level.

### (3) Preconfiguration (1) (Interrupt from external pin)

In order to use external interrupt pin, it is necessary to do proper setting to the port function register of the corresponding pin. Setting "1" to [PxIE]<PxmIE> allows the pin to be used as the function pin and the input port.

| Port Register          |              |     |

|------------------------|--------------|-----|

| [PxIE] <pxmie></pxmie> | <del>-</del> | "1" |

Note: x: port number, m: corresponding bit of function register number. Be careful not to enable interrupts that are not used when performing interrupt setting. Also be aware of the description of "4.3.5.Precautions When Using External Interrupt Pins

# (4) Preconfiguration (2) (Interrupt from peripheral function)

The setting varies depending on the peripheral function to be used. See the reference manual of each peripheral function for details

### (5) Preconfiguration (3) (Interrupt from Set-Pending Register)

To generate an interrupt by using the Interrupt Set-Pending Register, set "1" to the corresponding bit of this register.

| NVIC Register       |              |     |

|---------------------|--------------|-----|

| <setpend></setpend> | <del>(</del> | "1" |

Note: <SETPEND>: corresponding bit

#### (6) Configuring the INTIF

The interrupt by way of INTIF sets the interrupt detection enable in interrupt control registers.

The [IANIC00]/[IBNIC00]/[IBIMCxxx] registers are capable of configuring each interrupt source. Before enabling an interrupt detection, clear the interrupt request having active level in order to avoid unexpected interrupt.

For details of the interrupt control register, refer to the following.

| Interrupt Control Register                                                                   |              |                                                                                                           |  |  |

|----------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------|--|--|

| [IBIMCxxx] <intmode> ←</intmode>                                                             |              | Value corresponding to the interrupt to be used (Only for the interrupt having interrupt detection level) |  |  |

| [IANIC00] <intnclr> [IBNIC00]<intpclr> [IBIMCxxx]<intpclr>&lt;</intpclr></intpclr></intnclr> | <b>←</b>     | Interrupt request clear to use                                                                            |  |  |

| [IBIMCxxx] <inten></inten>                                                                   | <del>(</del> | "1" (Interrupt detection enabled)                                                                         |  |  |

Note: xxx: number specific to the interrupt request

### (7) Enabling Interrupt by CPU

Enable the interrupt by the CPU as shown below.

Clear the suspended interrupt in the Interrupt Clear-Pending Register. Enable the intended interrupt with the Interrupt Set-Enable Register. Each bit of the register is assigned to a single interrupt source.

Writing "1" to the corresponding bit of the Interrupt Clear-Pending Register clears the suspended interrupt. Writing "1" to the corresponding bit of the Interrupt Set-Enable Register enables the intended interrupt.

To generate interrupts in the Interrupt Set-Pending Register setting, factors to trigger interrupts are lost if pending interrupts are cleared. Thus, this operation is not necessary.

At the end, [PRIMASK] register is zero cleared.

| NVIC Register                  |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| <clrpend></clrpend>            |  |  |  |  |  |

| <setena> <b>←</b> "1"</setena> |  |  |  |  |  |

| Interrupt Mask Register        |  |  |  |  |  |

| [PRIMASK] ← "0"                |  |  |  |  |  |

Note 1: <CLRPEND>,<SETENA>: corresponding bit

Note 2: [PRIMASK] Register cannot be modified by the user access level;

# 4.6.3. Detection(INTIF)

When the INTIF detects an interrupt request, it sends the interrupt signal in "High" level to the CPU.

INTIF has the functions of the interrupt detection level selection logic, the functions of interrupt detection logic, and the function of the interrupt detection enable/disable. Each function of INTIF is set up the Interrupt Control Register A or B.

It keeps sending the interrupt signal in "High" level to the CPU until the <Detection flag> is cleared in the Interrupt Control Register. If the ISR is exited without clearing the flag, the same interrupt will be detected again when normal operation is resumed. Thus, be sure to clear each <Detection flag> in the ISR. At the same time, the corresponding interrupt monitor register is also cleared.

#### 4.6.4. Detection(CPU)

The CPU detects an interrupt request with the highest priority.

### 4.6.5. CPU Processing

On detecting an interrupt, the CPU pushes the contents of xPSR, PC, LR, r12, and r3–r0 to the stack then enter the ISR.

# 4.6.6. Interrupt Service Routine (ISR) (Clearing an interrupt Source)

An ISR requires specific programming according to the application to be used. This section describes what is recommended at the service routine programming and how the source is cleared.

### (1) Process in the Interrupt Service Routine

An ISR normally pushes register contents to the stack and handles an interrupt as required.

The Cortex-M4 processor with FPU automatically pushes the contents of xPSR, PC, LR, r12, and r3–r0 to the stack. No extra programming is required for them.

Push the contents of other registers if needed.

Interrupt requests with higher priority and exceptions such as NMI are accepted even when an ISR is being executed. We recommend you to push the contents of general-purpose registers that might be rewritten.

#### (2) Clearing an Interrupt Source

Some interrupt requests have to be cleared with the Interrupt Control Register.

If an interrupt detection level is set as level-sensitive, an interrupt request continues to exist until it is cleared at its source. Therefore, the interrupt source must be cleared. If a factor is withdrawn in level detection, the interrupt request signal from INTIF will be withdrawn automatically.

A factor is withdrawn by clearing the <Detection flag> of the Interrupt Control Register of INTIF in the case of edge detection. When an effective edge occurs again, it is anew recognized as a factor.

Note: After clearing the <Detection flag> of the Interrupt Control Register, please be sure to read the flag which was cleared.

# 5. Exception/Interrupt-Related Registers

# 5.1. Register List

Control Registers and their addresses are as follows;

**Interrupt Control Registers A**

| Peripheral function          |    | Channel/Unit | Base address |

|------------------------------|----|--------------|--------------|

| Interrupt control register A | IA | _            | 0x4003E000   |

| Register name                                | Address (+Base) |        |

|----------------------------------------------|-----------------|--------|

| Non-Maskable Interrupt A Control Register 00 | [IANIC00]       | 0x0000 |

Note: Byte access is needed for [IANIC00].

**Interrupt Control Registers B**

| Peripheral function          | )  | Channel/Unit | Base address |

|------------------------------|----|--------------|--------------|

| Interrupt control register B | IB | _            | 0x40083200   |

| Register name                                |            | Address (+Base)  |

|----------------------------------------------|------------|------------------|

| Non-Maskable Interrupt B Control Register 00 | [IBNIC00]  | 0x0010           |

| Interrupt B Mode Control Register 000        | [IBIMC000] | 0x0060           |

| Interrupt B Mode Control Register 001        | [IBIMC001] | 0x0061           |

| Interrupt B Mode Control Register 002        | [IBIMC002] | 0x0062           |

| Interrupt B Mode Control Register 003        | [IBIMC003] | 0x0063           |

| Interrupt B Mode Control Register 004        | [IBIMC004] | 0x0064           |

| Interrupt B Mode Control Register 005        | [IBIMC005] | 0x0065           |

| Interrupt B Mode Control Register 006        | [IBIMC006] | 0x0066           |

| Interrupt B Mode Control Register 007        | [IBIMC007] | 0x0067           |

| Interrupt B Mode Control Register 008        | [IBIMC008] | 0x0068           |

| Interrupt B Mode Control Register 009        | [IBIMC009] | 0x0069           |

| Interrupt B Mode Control Register 010        | [IBIMC010] | 0x006A           |

| Interrupt B Mode Control Register 011        | [IBIMC011] | 0x006B           |

| Interrupt B Mode Control Register 012        | [IBIMC012] | 0x006C           |

| Interrupt B Mode Control Register 013        | [IBIMC013] | 0x006D           |

| Interrupt B Mode Control Register 014        | [IBIMC014] | 0x006E           |

| Interrupt B Mode Control Register 015        | [IBIMC015] | 0x006F           |

| Interrupt B Mode Control Register 016        | [IBIMC016] | 0x0070           |

| Interrupt B Mode Control Register 017        | [IBIMC017] | 0x0071           |

| Interrupt B Mode Control Register 018        | [IBIMC018] | 0x0077           |

| Interrupt B Mode Control Register 019        | [IBIMC019] | 0x0072           |

| Interrupt B Mode Control Register 020        | [IBIMC020] | 0x0074           |

| Interrupt B Mode Control Register 020        | [IBIMC021] | 0x0075           |

| Interrupt B Mode Control Register 021        | [IBIMC021] | 0x0075           |

| Interrupt B Mode Control Register 022        | [IBIMC023] | 0x0070           |

| Interrupt B Mode Control Register 023        | [IBIMC024] | 0x0077           |

| Interrupt B Mode Control Register 024        | [IBIMC025] | 0x0078           |

|                                              |            | 0x0079<br>0x007A |

| Interrupt B Mode Control Register 026        | [IBIMC026] |                  |

| Interrupt B Mode Control Register 027        | [IBIMC027] | 0x007B           |

| Interrupt B Mode Control Register 028        | [IBIMC028] | 0x007C           |

| Interrupt B Mode Control Register 029        | [IBIMC029] | 0x007D           |

| Interrupt B Mode Control Register 030        | [IBIMC030] | 0x007E           |

| Interrupt B Mode Control Register 031        | [IBIMC031] | 0x007F           |

| Interrupt B Mode Control Register 032        | [IBIMC032] | 0x0080           |

| Interrupt B Mode Control Register 033        | [IBIMC033] | 0x0081           |

| Interrupt B Mode Control Register 034        | [IBIMC034] | 0x0082           |

| Interrupt B Mode Control Register 035        | [IBIMC035] | 0x0083           |

| Interrupt B Mode Control Register 036        | [IBIMC036] | 0x0084           |

| Interrupt B Mode Control Register 037        | [IBIMC037] | 0x0085           |

| Interrupt B Mode Control Register 038        | [IBIMC038] | 0x0086           |

| Interrupt B Mode Control Register 039        | [IBIMC039] | 0x0087           |

| Interrupt B Mode Control Register 040        | [IBIMC040] | 0x0088           |

| Interrupt B Mode Control Register 041        | [IBIMC041] | 0x0089           |