## 32-bit RISC Microcontroller

## **TXZ Family**

## Reference Manual Programmable Motor Control Circuit plus (PMD+-B)

**Revision 1.0**

2018-10

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

### Contents

| Ρ  | Preface                                               | 5  |

|----|-------------------------------------------------------|----|

|    | Related document                                      | 5  |

|    | Conventions                                           | 6  |

|    | Terms and Abbreviations                               | 8  |

| 1. | . Outlines                                            | 9  |

| 2. | Configuration                                         |    |

| 3. |                                                       |    |

|    | 3.1. Clock Supply                                     |    |

|    | 3.2. Pulse Width Modulation Circuit                   |    |

|    | 3.2.1. Setting the PWM period                         |    |

|    | 3.2.2. Compare function                               |    |

|    | 3.2.3. Waveform mode                                  |    |

|    | 3.2.4. Interrupt processing                           |    |

|    | 3.3. Conduction Control Circuit                       |    |

|    | 3.4. Protection Control Circuit                       |    |

|    | 3.4.1. EMG Protection Circuit                         |    |

|    | 3.4.2. OVV Protection Circuit                         |    |

|    | 3.4.3. Protection control when using the debug tool   | 24 |

|    | 3.5. Dead time Control Circuit                        |    |

|    | 3.6. Synchronous Trigger Generation Circuit           |    |

| 4. | . Registers                                           |    |

|    | 4.1. List of Registers                                |    |

|    | 4.2. Details of Registers                             |    |

|    | 4.2.1. [PMDxMDEN] (PMD Enable Register)               |    |

|    | 4.2.2. [PMDxPORTMD] (Port Output Mode Register)       |    |

|    | 4.2.3. [PMDxMODESEL] (Mode Selection Register)        |    |

|    | 4.2.4. [PMDxMDCR] (PMD Control Register)              |    |

|    | 4.2.5. [PMDxCNTSTA] (PWM Counter Status Register)     |    |

|    | 4.2.6. [PMDxMDCNT] (PWM Counter Register)             |    |

|    | 4.2.7. [PMDxMDPRD] (PWM Period Register)              |    |

|    | 4.2.8. [PMDxCMPU] (PWM Compare U Register)            |    |

|    | 4.2.9. [PMDxCMPV] (PWM Compare V Register)            | 36 |

|    | 4.2.10. [PMDxCMPW] (PWM Compare W Register)           | 37 |

|    | 4.2.11. [PMDxMDPOT] (PMD Output Setting Register)     |    |

|    | 4.2.12. [PMDxMDOUT] (PMD Conduction Control Register) | 39 |

|    | 4.2.13. [PMDxEMGREL] (EMG Release Register)           | 40 |

|    | 4.2.14. [PMDxEMGCR] (EMG Control Register)            | 41 |

|    | 4.2.15. [PMDxEMGSTA] (EMG Status Register)            | 42 |

|    | 4.2.16. [PMDxOVVCR] (OVV Control Register)            | 42 |

|    | 4.2.17. [PMDxOVVSTA] (OVV Status Register)            | 43 |

|    | 4.2.18. [PMDxDTR] (Dead time Register)                | 44 |

|    | 4.2.19. [PMDxTRGCMP0] (Trigger Compare 0 Register)              | 44   |

|----|-----------------------------------------------------------------|------|

|    | 4.2.20. [PMDxTRGCMP1] (Trigger Compare 1 Register)              | 45   |

|    | 4.2.21. [PMDxTRGCMP2] (Trigger Compare 2 Register)              | 46   |

|    | 4.2.22. [PMDxTRGCMP3] (Trigger Compare 3 Register)              | 46   |

|    | 4.2.23. [PMDxTRGCR] (Trigger Control Register)                  | 47   |

|    | 4.2.24. [PMDxTRGSYNCR] (Trigger Update Timing Setting Register) | 48   |

|    | 4.2.25. [PMDxTRGMD] (Trigger Output Mode Setting Register)      | 49   |

|    | 4.2.26. [PMDxTRGSEL] (Trigger Output Select Register)           | 50   |

| 5. | Precautions                                                     | .51  |

| 6. | Revision History                                                | .52  |

| RE | STRICTIONS ON PRODUCT USE                                       | . 53 |

## List of Figures

| Figure 1.1 | Functions related to PMD                                  |    |

|------------|-----------------------------------------------------------|----|

| Figure 2.1 | PMD Block diagram                                         |    |

| Figure 3.1 | Pulse Width Modulation Circuit                            | 14 |

| Figure 3.2 | PWM Waveforms                                             |    |

| Figure 3.3 | Waveforms of PWM triangular wave carrier using fixed edge |    |

| Figure 3.4 | Conduction Control Circuit                                |    |

| Figure 3.5 | Protection Control Circuit                                |    |

| Figure 3.6 | Dead time Control Circuit                                 |    |

| Figure 3.7 | Dead Time Circuit                                         |    |

| Figure 3.8 | Dead Time Correction                                      |    |

| Figure 3.9 | Synchronous Trigger Generation Circuit                    |    |

|            | Example of using the PMD trigger at 3-shunt               |    |

|            | Example of using the PMD trigger at 1-shunt               |    |

|            |                                                           |    |

### List of Tables

| Table 2.1 | List of signals                                                                                                 | 12   |

|-----------|-----------------------------------------------------------------------------------------------------------------|------|

|           | [PMDxMDOUT] / VExOUTCR buffer Update Timing                                                                     |      |

| Table 3.  | 2 Decode circuit outputs according to [PMDxMDOUT] / VExOUTCR                                                    | and  |

| [PMD      | xMDCR] <syntmd> setting</syntmd>                                                                                | . 20 |

| Table 4.1 | [PMDxMDPRD], [PMDxCMPU/V/W] buffer Update Timing                                                                | . 34 |

| Table 4.2 | Port Outputs according to <noc>, <npwm>, <polh>,<poll>and <syntmd> settings</syntmd></poll></polh></npwm></noc> | . 40 |

| Table 4.3 | [PMDxTRGCMPn] buffer Update Timing                                                                              | 45   |

| Table 4.4 | Trigger Output Patterns                                                                                         | 49   |

| Table 6.1 | Revision History                                                                                                | . 52 |

#### Preface

#### **Related document**

| Document name                         |  |  |  |  |

|---------------------------------------|--|--|--|--|

| Exception                             |  |  |  |  |

| Clock Control and Operation Mode      |  |  |  |  |

| Input/Output Ports                    |  |  |  |  |

| 12-bit Analog to Digital Converter    |  |  |  |  |

| Advanced Vector Engine                |  |  |  |  |

| 32-bit Advanced Encoder Input Circuit |  |  |  |  |

| Product Information                   |  |  |  |  |

#### Conventions

- Numeric formats follow the rules as shown below:

- Hexadecimal: 0xABC

Decimal: 123 or 0d123 – Only when it needs to be explicitly shown that they are decimal numbers. Binary: 0b111 – It is possible to omit the "0b" when the number of bit can be distinctly understood from a sentence.

- "\_N" is added to the end of signal names to indicate low active signals.

- It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

- When two or more signal names are referred, they are described like as [m: n]. Example: S[3: 0] shows four signal names S3, S2, S1 and S0 together.

- The characters surrounded by [] defines the register. Example: [ABCD]

- "n" substitutes suffix number of two or more same kind of registers, fields, and bit names. Example: [XYZ1], [XYZ2], [XYZ3] → [XYZn]

- "x" substitutes suffix number or character of units and channels in the Register List. In case of unit, "x" means A, B, and C ... Example: [ADACR0], [ADBCR0], [ADCCR0] → [ADxCR0] In case of channel, "x" means 0, 1, and 2 ... Example: [T32A0RUNA], [T32A1RUNA], [T32A2RUNA] → [T32AxRUNA]

- The bit range of a register is written like as [m: n]. Example: Bit[3: 0] expresses the range of bit 3 to 0.

- The configuration value of a register is expressed by either the hexadecimal number or the binary number. Example: [ABCD]<EFG>=0x01 (hexadecimal), [XYZn]<VW>=1 (binary)

- Word and Byte represent the following bit length.

| Byte:        | 8 bits  |

|--------------|---------|

| Half word:   | 16 bits |

| Word:        | 32 bits |

| Double word: | 64 bits |

• Properties of each bit in a register are expressed as follows:

| 1    | U 1                    |       |

|------|------------------------|-------|

| R:   | Read only              |       |

| W:   | Write only             |       |

| R/W: | Read and Write are pos | sible |

- Unless otherwise specified, register access supports only word access.

- The register defined as reserved must not be rewritten. Moreover, do not use the read value.

- The value read from the bit having default value of "—" is unknown.

- When a register containing both of writable bits and read-only bits is written, read-only bits should be written with their default value, In the cases that default is "—", follow the definition of each register.

- Reserved bits of the Write-only register should be written with their default value. In the cases that default is "—", follow the definition of each register.

- Do not use read-modified-write processing to the register of a definition which is different by writing and read out.

Arm, Cortex and Thumb are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

# arm

The Flash memory uses the Super Flash® technology under license from Silicon Storage Technology, Inc. Super Flash® is registered trademark of Silicon Storage Technology, Inc.

All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

#### **Terms and Abbreviations**

Some of abbreviations used in this document are as follows:

| ADC     | Analog to Digital Converter             |

|---------|-----------------------------------------|

| A-ENC32 | Advanced Encoder Input Circuit (32bit)  |

| A-VE    | Advanced Vector Engine                  |

| PMD     | Programmable Motor Control Circuit Plus |

| PWM     | Pulse Width Modulation                  |

## 1. Outlines

The programmable motor control circuit plus (PMD) can operate as a motor control circuit of 1 channel per unit. The following is a list of functions. The following is a list of functions.

| Function<br>Classification | Function                                | Operation                                                                                                                                                                                                                                                                               |

|----------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            | Resolution                              | The count resolution of PWM carrier: 1/fsys or 4/fsys.<br>Resolution of PWM period and Duty<br>Saw-tooth wave carrier: 1/fsys or 4/fsys<br>Triangular wave carrier: 2/fsys or 8/fsys                                                                                                    |

| Output waveform generation | PWM generation                          | PWM carrier waveform: Saw-tooth wave or Triangular wave<br>3-phase PWM can be generated with three comparators.<br>3-phase mode: 3-phase common duty or 3-phase independent duty                                                                                                        |

|                            | Output waveform<br>(Conduction control) | Each of the U/X, V/Y and W/Z phases can be selected PWM or High/Low output.<br>Upper-phase output or lower-phase output respectively can be set to low-active or high-active.<br>This function has the common PWM carrier waveform and generates independent 3-phase complementary PWM. |

|                            |                                         | It generates a synchronous sampling signal that starts AD conversion at an arbitrary timing synchronized with the PWM carrier.                                                                                                                                                          |

| Buffer function            | _                                       | PWM period, Duty, Synchronous trigger timing, and 6 port output setting<br>are double-buffered. These setting can be changed during operation.<br>Update timing can be selected by Asynchronous, Carrier bottom,<br>Carrier peak and Carrier peak/bottom.                               |

| Protection                 | Protection control                      | <ul><li>This function stop output by protection signal input (OFF output or output disabled)</li><li>Two types of protection function: EMG and OVV.</li><li>OVV can be selected monitor function of ADC for protection input.</li></ul>                                                 |

|                            | Dead time control                       | The dead time control inserts the dead time for preventing short-circuit at switching between the upper-phase and lower-phase (U/X, V/Y, W/Z). The complementary PWM is output.                                                                                                         |

| Interrupt request          | PWM interrupt                           | <ul> <li>PWM interrupt request is generated at a synchronous timing with the PWM period.</li> <li>Interrupt timing: PWM carrier bottom or PWM carrier peak</li> <li>Interrupt frequency: Half PWM period, one PWM period, two PWM period, or four PWM period.</li> </ul>                |

|                            | EMG interrupt                           | This interrupt request is generated by the EMG protection of EMGx_N input                                                                                                                                                                                                               |

|                            | OVV interrupt                           | This interrupt request is generated by the OVV protection of OVV input                                                                                                                                                                                                                  |

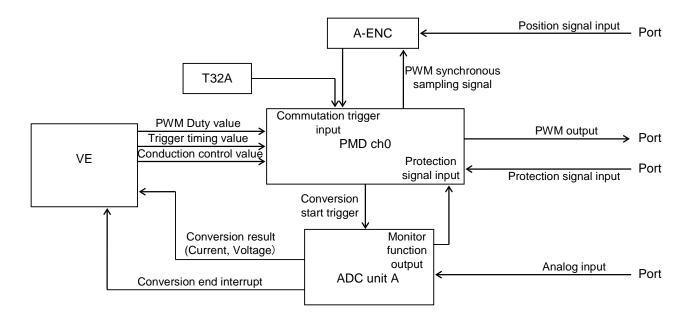

The PMD realizes 3-phase motor control including Vector control when it cooperates with an advanced vector engine (hereafter, abbreviated as VE), an analog to digital converter (hereafter, abbreviated as ADC), and an advanced encoder input circuit (32-bit) (hereafter, abbreviated as A-ENC).

The pulse width modulation circuit, the conduction control circuit, and the synchronous trigger generation circuit can be controlled by the VE. The synchronous trigger generation circuit can start operating ADC. The conduction control circuit can perform commutation control by trigger input signal from the A-ENC.

Figure 1.1 Functions related to PMD

## 2. Configuration

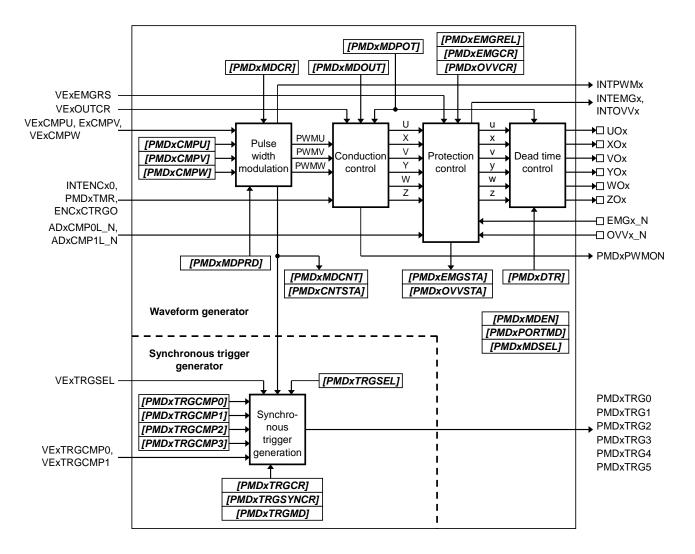

Figure 2.1 PMD Block diagram

| No | Signal name                     |                                                                   | I/O    | Related Reference manual       |

|----|---------------------------------|-------------------------------------------------------------------|--------|--------------------------------|

| 1  | UOx                             | U-phase output pin                                                | Output | Product Information            |

| 2  | XOx                             | X-phase output pin                                                | Output | Product Information            |

| 3  | VOx                             | V-phase output pin                                                | Output | Product Information            |

| 4  | YOx                             | Y-phase output pin                                                | Output | Product Information            |

| 5  | WOx                             | W-phase output pin                                                | Output | Product Information            |

| 6  | ZOx                             | Z-phase output pin                                                | Output | Product Information            |

| 7  | EMGx_N                          | EMG detection input pin                                           | Input  | Product Information            |

| 8  | OVVx_N                          | OVV detection input pin                                           | Input  | Product Information            |

| 9  | PMDxPWMON                       | PWM signal for the encoder input                                  | Output | Product Information            |

| 10 | INTENCx0                        | Commutation trigger<br>(A-ENC position detection synchronization) | Input  | Product Information            |

| 11 | PMDxTMR                         | Commutation trigger<br>(General-purpose timer synchronization)    | Input  | Product Information            |

| 12 | ENCxCTRGO                       | Commutation trigger<br>(A-ENC MCMP completion synchronization)    | Input  | Product Information            |

| 13 | ADxCMP0L_N                      | OVV state signal<br>(AD monitor function 0)                       | Input  | Product Information            |

| 14 | ADxCMP1L_N                      | OVV state signal<br>(AD monitor function 1)                       | Input  | Product Information            |

| 15 | PMDxTRG0                        | ADC synchronous sampling output 0                                 | Output | Product Information            |

| 16 | PMDxTRG1                        | ADC synchronous sampling output 1                                 | Output | Product Information            |

| 17 | PMDxTRG2                        | ADC synchronous sampling output 2                                 | Output | Product Information            |

| 18 | PMDxTRG3                        | ADC synchronous sampling output 3                                 | Output | Product Information            |

| 19 | PMDxTRG4                        | ADC synchronous sampling output 4                                 | Output | Product Information            |

| 20 | PMDxTRG5                        | ADC synchronous sampling output 5                                 | Output | Product Information            |

| 21 | INTPWMx                         | PWM interrupt                                                     | Output | Exception, Product Information |

| 22 | INTEMGx                         | EMG interrupt                                                     | Output | Exception                      |

| 23 | INTOVVx                         | OVV interrupt                                                     | Output | Exception                      |

| 24 | VExCMPU                         | VE U-phase PWM duty                                               | Input  | Product Information            |

| 25 | 5 VExCMPV VE V-phase PWM duty   |                                                                   | Input  | Product Information            |

| 26 | VExCMPW VE W-phase PWM duty     |                                                                   | Input  | Product Information            |

| 27 | VExTRGCMP0 VE Trigger compare 0 |                                                                   | Input  | Product Information            |

| 28 | VExTRGCMP1                      | VE Trigger compare 1                                              | Input  | Product Information            |

| 29 | VExTRGSEL                       | VE Synchronous trigger output selection                           | Input  | Product Information            |

| 30 | VExOUTCR                        | VE Conduction control / output control                            | Input  | Product Information            |

| 31 | VExEMGRS VE EMG return          |                                                                   | Input  | Product Information            |

#### Table 2.1 List of signals

## 3. Function and Operation

The PMD circuit consists of two blocks of a wave generation circuit and a synchronous trigger generation circuit. The wave generation circuit includes a pulse width modulation circuit, a conduction control circuit, a protection control circuit, and a dead time control circuit.

- The pulse width modulation circuit has the common PWM carrier waveform and generates independent 3-phase PWM waveforms.

- The conduction control circuit determines the output pattern for each of the upper and lower sides of the U-, V-, and W-phases.

- The protection control circuit controls emergency output stop by EMG input and OVV input.

- The dead time control circuit prevents a short circuit which may occur when the upper side and lower side are switched.

- The synchronous trigger generation circuit generates synchronous trigger signals to the ADC for starting AD conversion.

## 3.1. Clock Supply

When using PMD, set an applicable clock enable bit to "1" (clock supply) in Clock supply and stop register A for fsys (*[CGFSYSENA]*, *[CGFSYSMENA]*), Clock supply and stop register B for fsys (*[CGFSYSENB]*, *[CGFSYSMENB]*), and Clock supply and stop register for fc (*[CGFCEN]*). An applicable register and the bit position vary according to a product. Therefore, the register may not exist with the product. Please refer to "Clock Control and Operation Mode" of the reference manual for the details.

## 3.2. Pulse Width Modulation Circuit

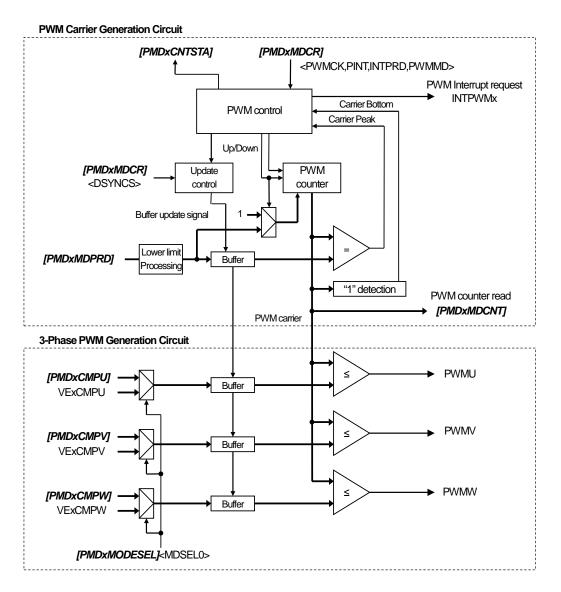

Figure 3.1 Pulse Width Modulation Circuit

The pulse width modulation circuit has a 16-bit PWM up/down-counter and generates PWM carrier waveforms with a resolution of 1/fsys. The PWM period extension mode (*[PMDxMDCR]*<PWMCK>=1) is also available. When this mode is selected, the PWM counter generates PWM carrier waveforms with a resolution of 4/fsys.

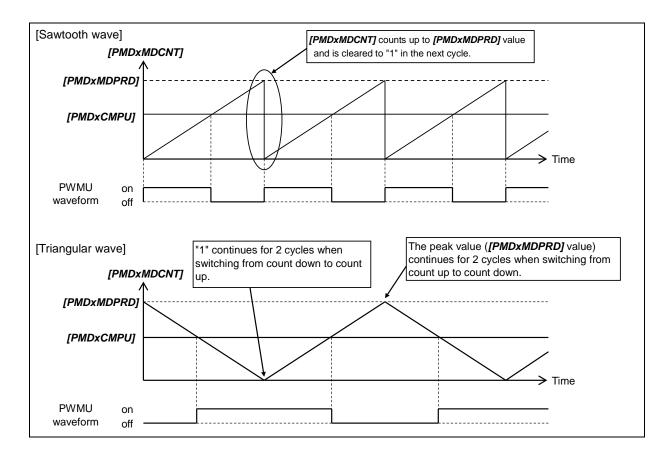

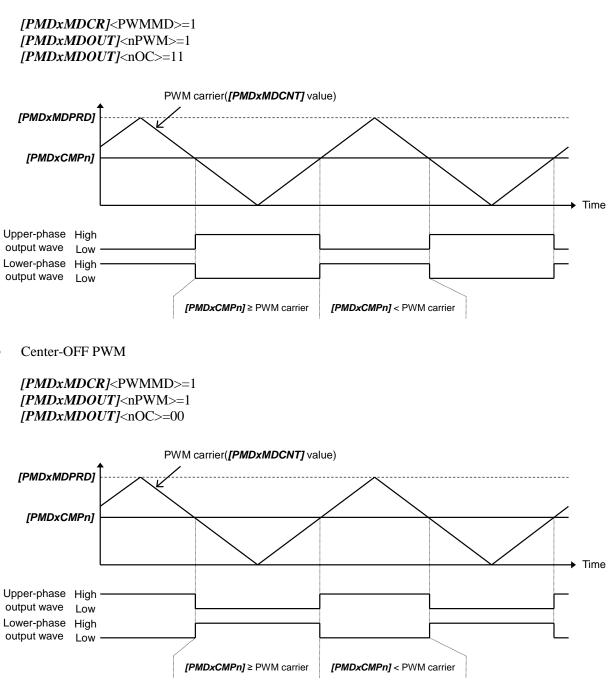

The PWM carrier waveform mode can be selected from mode 0 (edge-aligned PWM, saw-tooth waveform) and mode 1 (center-aligned PWM, triangular waveform). (Refer to "Figure 3.2 PWM Waveforms".)

#### 3.2.1. Setting the PWM period

The PWM period is determined by the *[PMDxMDPRD]* register. This register is double-buffered. The subsequent stage buffer is updated at every PWM period. It is also possible to update at every half PWM period. (Refer to "Table 4.1 *[PMDxMDPRD]*, *[PMDxCMPU/V/W]* buffer Update Timing".)

| Sawtooth wave PWM :     |                       | System clock fsys [Hz] |

|-------------------------|-----------------------|------------------------|

| Sawloolin wave PVVIVI . | [PMDxMDPRD] value = - | PWM frequency [Hz]     |

| Triangular wave PWM :   | [PMDxMDPRD] value =   | System clock fsys [Hz] |

| mangular wave rivivi .  |                       | PWM frequency [Hz] ×2  |

#### 3.2.2. Compare function

The pulse width modulation circuit generates PWM waveforms of the desired duty by comparing the magnitude of the 3 phase PWM compare registers (*[PMDxCMPU]*, *[PMDxCMPV]*, *[PMDxCMPW]*) and the PWM carrier which is generated by the PWM counter (*[PMDxMDCNT]*).

The PWM compare register of each phase has a double-buffered register. The PWM compare register value is loaded into the subsequent stage buffer at every PWM period. It is also possible to update at every half a PWM period. (Refer to "Table 4.1 *[PMDxMDPRD]*, *[PMDxCMPU/V/W]* buffer Update Timing".)

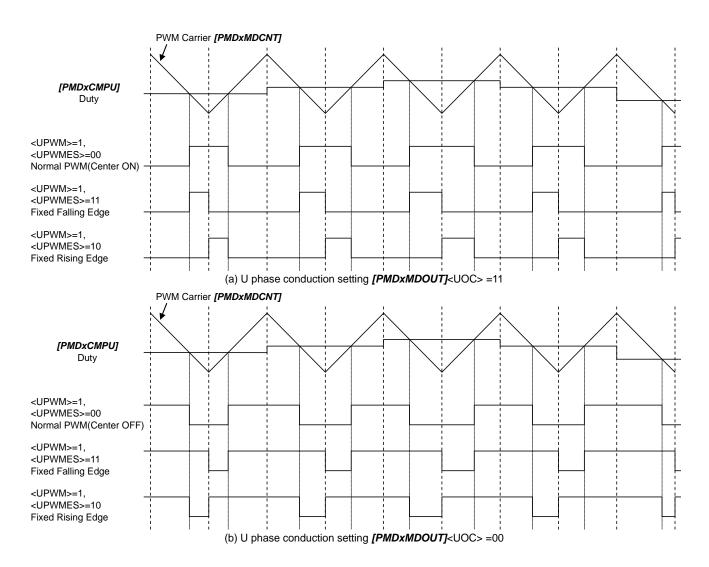

Figure 3.2 PWM Waveforms

When triangular wave carrier, the PWM waveform of each phase is selected from the center-aligned PWM, the falling edge fixed PWM and the rising edge fixed PWM by *[PMDxMDCR]*<nPWMES>(n = U,V,W) setting. (Refer to "Figure 3.3 Waveforms of PWM triangular wave carrier using fixed edge").

Figure 3.3 Waveforms of PWM triangular wave carrier using fixed edge

Also, PWM output of each phase of 3 phase PWM, can be switched between the center-on PWM and the center-off PWM with combination of *[PMDxMDOUT]*<nOC>, <nPWM>(n=U, V, W), and *[PMDxMDCR]*<SYNTMD> (Refer to "3.3 Conduction Control Circuit").

#### 3.2.3. Waveform mode

3-phase PWM waveforms can be generated in the following two modes by [PMDxMDCR]<DTYMD> setting:

• 3-phase independent mode:

Each of the PWM compare registers for the three phases is set independently to generate independent PWM waveforms for each phase. This mode is used to generate drive waveforms such as sinusoidal waves.

• 3-phase common mode:

Only the U-phase PWM compare register is set to generate identical PWM waveforms for all the three phases. This mode is used for rectangular wave drive of brushless DC motors.

#### 3.2.4. Interrupt processing

The pulse width modulation circuit generates PWM interrupt requests in synchronization with PWM waveforms. Interrupt request timing can be selected either at PWM carrier peak or at PWM carrier bottom.

The frequency of PWM interrupts can be set to half a PWM period, one PWM period, two PWM periods or four PWM periods.

## **3.3. Conduction Control Circuit**

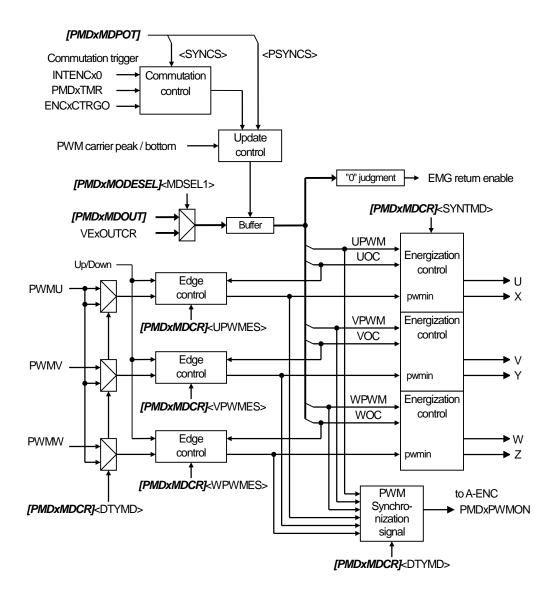

Figure 3.4 Conduction Control Circuit

The conduction control circuit performs the six phase outputs (U/X, V/Y, W/Z) control according to the settings made in the output control register *[PMDxMDOUT]* / VExOUTCR and the output setting register *[PMDxMDOUT]* / VExOUTCR register is double-buffered and update timing can be select as synchronous or asynchronous to PWM. Update timing synchronizing with trigger input from another peripheral function can also be selected. (For details of update timing, refer to "Table 3.1 *[PMDxMDOUT]* / VExOUTCR buffer Update Timing".)

<UPWM>, <VPWM>, <WPWM> of the *[PMDxMDOUT]* register selects PWM or High/Low output for each of the U/X, V/Y and W/Z phases. When PWM output is selected, PWM waveforms are output. When High/Low output is selected, output is fixed to either a High level or Low level. Each output is set to "High" or "Low" by <UOC>, <VOC>, <WOC> of the register *[PMDxMDOUT]* / VEXOUTCR.

Refer to "Table 3.2 Decode circuit outputs according to *[PMDxMDOUT]* / VExOUTCR and [PMDxMDCR]<SYNTMD> setting" for six phase outputs control with the output control setting (*[PMDxMDOUT]* / VExOUTCR and *[PMDxMDPOT]*), and the port output setting (*[PMDxMDCR]*<SYNTMD>).

In addition, using *[PMDxMDPOT]*<POLH>,<POLL>, six output ports can be set to low-active or high-active on upper-phase outputs (UOx,VOx,WOx) or lower-phase outputs (XOx,YOx,ZOx) respectively.

The conduction control circuit outputs a PWM signal (PWMON) to the encoder input circuit (A-ENC). The external input signal in the A-ENC is sampled synchronously with the PWMON.

|                                            |    | [PMDxMDPOT] <psyncs> setting</psyncs>                                    |                                                                                       |                                                                                     |                                                                                                                           |

|--------------------------------------------|----|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                                            |    | 00                                                                       | 01                                                                                    | 10                                                                                  | 11                                                                                                                        |

|                                            | 00 | Constant update                                                          | PWM carrier bottom                                                                    | PWM carrier peak                                                                    | PWM carrier peak and<br>PWM carrier bottom                                                                                |

|                                            | 01 | When INTENCx0<br>(Note2)<br>is arisen                                    | The first PWM carrier<br>bottom every time<br>when INTENCx0<br>(Note2)<br>is arisen.  | The first PWM carrier<br>peak every time<br>when INTENCx0<br>(Note2)<br>is arisen.  | Either the first PWM<br>carrier peak or the first<br>carrier bottom every time<br>when INTENCx0(Note2)<br>is arisen.      |

| [PMDxMDPOT]<br><syncs><br/>setting</syncs> | 10 | When PMDxTMR<br>(Note2)<br>is arisen.                                    | The first PWM carrier<br>bottom every time<br>when PMDxTMR<br>(Note2)<br>is arisen.   | The first PWM carrier<br>peak every time<br>when PMDxTMR<br>(Note2)<br>is arisen.   | Either the first PWM<br>carrier peak or the first<br>carrier bottom every time<br>when PMDxTMR(Note2)<br>is arisen.       |

|                                            | 11 | When ENCxCTRGO<br>(Note2)<br>(MCMP compare<br>established)<br>is arisen. | The first PWM carrier<br>bottom every time<br>when ENCxCTRGO<br>(Note2)<br>is arisen. | The first PWM carrier<br>peak every time<br>when ENCxCTRGO<br>(Note2)<br>is arisen. | Either the first PWM<br>carrier peak or the first<br>carrier bottom every time<br>when ENCxCTRGO<br>(Note2)<br>is arisen. |

#### Table 3.1 [PMDxMDOUT] / VExOUTCR buffer Update Timing

Note1: If PMD is disabled ([PMDxMDEN]<PWMEN>=0), the retained trigger condition is cleared.

Note2: The connection destination depend on the product. For details, refer to "Product Information" of the reference manual.

#### Table 3.2 Decode circuit outputs according to [PMDxMDOUT] / VExOUTCR and [PMDxMDCR]<SYNTMD> setting

| [PMDxMDCR] <syntmd>=0</syntmd> |  |

|--------------------------------|--|

|--------------------------------|--|

|                            |    | PWM output setting<br>[PMDxMDOUT] <npwm></npwm> |             |               |             |  |  |  |

|----------------------------|----|-------------------------------------------------|-------------|---------------|-------------|--|--|--|

|                            |    | 0: H/L                                          | output      | 1: PWM output |             |  |  |  |

|                            |    | Upper-phase                                     | Lower-phase | Upper-phase   | Lower-phase |  |  |  |

| Conduction setting         | 00 | Low                                             | Low         | PWM_N         | PWM         |  |  |  |

| [PMDxMDOUT]<br><noc></noc> | 01 | Low                                             | High        | Low           | PWM         |  |  |  |

|                            | 10 | High                                            | Low         | PWM           | Low         |  |  |  |

|                            | 11 | High                                            | High        | PWM           | PWM_N       |  |  |  |

[PMDxMDCR]<SYNTMD>=1

|                            | PWM output setting<br>[PMDxMDOUT] <npwm></npwm> |             |             |               |             |  |  |

|----------------------------|-------------------------------------------------|-------------|-------------|---------------|-------------|--|--|

|                            |                                                 | 0: H/L      | output      | 1: PWM output |             |  |  |

|                            |                                                 | Upper-phase | Lower-phase | Upper-phase   | Lower-phase |  |  |

| Conduction setting         | 00                                              | Low         | Low         | PWM_N         | PWM         |  |  |

| [PMDxMDOUT]<br><noc></noc> | 01                                              | Low         | High        | Low           | PWM_N       |  |  |

|                            | 10                                              | High        | Low         | PWM           | Low         |  |  |

|                            | 11                                              | High        | High        | PWM           | PWM_N       |  |  |

Note: n = U, V, W

• Center-ON PWM

## **3.4. Protection Control Circuit**

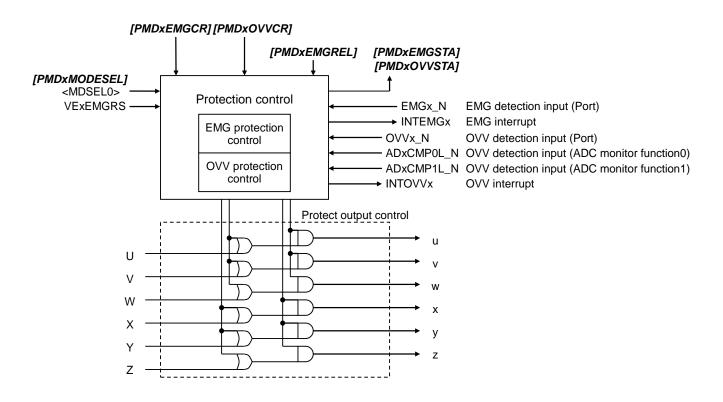

The protection control circuit consists of a protection control unit and a protect output control unit. The protection control unit consists of the EMG protection control circuit and the OVV protection control circuit.

Figure 3.5 Protection Control Circuit

#### 3.4.1. EMG Protection Circuit

The EMG protection circuit is an emergency stop protection circuit and operates when the EMGx\_N input goes "Low ". EMG protection is set through the EMG Control Register (*[PMDxEMGCR]*).

Note: After reset, the EMG protection circuit is enabled.

• EMG input

The noise filter is inserted in the EMGx\_N input. The noise detection time is selected with the EMG input detection time setting (*[PMDxEMGCR]*<EMGCNT>).

• EMG protection operation

The EMG protection circuit offers an emergency stop mechanism: when the EMGx\_N input is asserted  $(H\rightarrow L)$ , all six port outputs are immediately disabled (depending on the *[PMDxEMGCR]*<EMGMD> setting) and an EMG interrupt (INTEMGx) is generated. *[PMDxEMGCR]* <EMGMD> can be set to output a control signal that sets external output ports to High-impedance in case of an emergency. A read value of "1" in *[PMDxEMGSTA]*<EMGST> indicates that the EMG protection circuit is active.

• Return from the EMG protection

In the EMG protection state, it can be released by setting all the port output lines inactive (Set "0" to <UPWM>,<VPWM>,<UOC>,<VOC>,<WOC> of *[PMDxMDOUT]* / VExOUTCR.) (Note1) and then setting either <EMGRS> of *[PMDxEMGCR]* / VExEMGRS to "1". While the EMGx\_N input is "Low", any attempt to return from the EMG protection state is ignored. The EMG protection state can return after that confirming the status flag of *[PMDxEMGSTA]*<EMGI> is "1".

- Note1: The data of *[PMDxMDOUT]* / VExOUTCR is necessary to be reflected in the subsequent stage buffer.

- Note2: EMG return procedure after the reset deassertion.

After reset, the EMG function is enabled but EMGx\_N pin is configured as a normal port. Therefore, as the EMG protection might be valid, release the EMG protection by the following procedure at the initial sequence.

- (1) Selects EMG function by the Port function register([*PxFRn*]).

- (2) Reads [PMDxEMGSTA]<EMGI> to confirm it as "1".

- (3) Sets <UPWM>,<VPWM>,<WPWM>,<UOC>,<VOC>,<WOC> of [*PMDxMDOUT*] / VExOUTCR to "0" to make all ports in-active.

- (4) Return EMG protection by setting <EMGRS> of [PMDxEMGCR] / VExEMGRS to "1".

- Disable of the EMG protection function

To disable the EMG protection function, write "0x5A" and "0xA5" in this order to the EMG release register *[PMDxEMGREL]* and then clear *[PMDxEMGCR]*<EMGEN> to "0". These 3 instructions must be executed consecutively to prevent the EMG protection function from being inadvertently disabled.

#### 3.4.2. OVV Protection Circuit

The OVV protection circuit is activated when the OVV input becomes "Low". This protection control is set by OVV control register (*[PMDxOVVCR]*).

• OVV input

The OVV input can be selected from the OVVx\_N pin and the OVV status signal (ADxCMP0L\_N, ADxCMP1L\_N) of the AD monitor function by *[PMDxOVVCR]* <OVVISEL>, <ADIN0EN>, and <ADIN1EN>.

The noise filter is inserted in the OVV input. The noise detection time is selected with the OVV input detection time setting (*[PMDxOVVCR]*<OVVCNT>).

• OVV protection operation

OVV protection circuit fixes 6 port outputs in the port output disable unit to High level or Low level, when OVV signal input is active continuously for a predetermined interval time (set by <OVVCNT>). And OVV interrupt (INTOVVx) is generated. *[PMDxOVVCR]*<OVVMD> setting selects from among Lower-phases OFF/Upper-phases ON, Upper-phases OFF/Lower-phases ON, and all phases OFF.

A read value of "1" in *[PMDxOVVSTA]*<OVVST> indicates that the OVV protection circuit is active.

• Return from the OVV protection

The return from the OVV protection state is enabled by setting *[PMDxOVVCR]*<OVVRS> to "1". And after the OVV input becomes inactive, the OVV protection is automatically returned at a predetermined timing. (While the OVV protection input is "Low", any attempt to return from the OVV protection state is ignored. The state of the port can be checked by reading *[PMDxOVVSTA]*<OVVI>)

The OVV protection state is returned in synchronization with the PWM period (at the timing when PWM count (*[PMDxMDCNT]*) matches *[PMDxMDPRD]*. However if an interrupt on a half period of PWM is set, the protection state is returned when PWM count is "0x0001" or matches *[PMDxMDPRD]*.).

• Disable of the OVV protection function

In order to disable OVV function, EMG release register *[PMDxEMGREL]* should be set to "0x5A" and next, "0xA5". Then *[PMDxOVVCR]*<OVVEN> should be set to "0". These 3 instructions should be executed continuously to prevent the OVV protection function from being inadvertently disabled.

#### 3.4.3. Protection control when using the debug tool

When using the debug tool, PMD output ports can be disabled when PMD is stopped by the debug halt. In the debug halt, whether the port output becomes High-impedance or PMD output is selected by *[PMDxPORTMD]*<PORTMD> setting.

## 3.5. Dead time Control Circuit

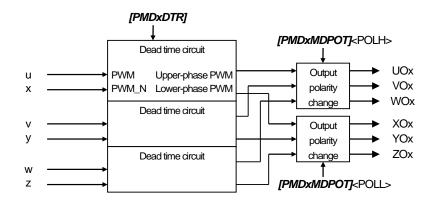

Figure 3.6 Dead time Control Circuit

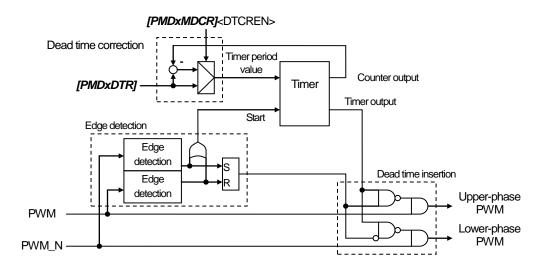

Figure 3.7 Dead Time Circuit

The dead time control circuit consists of a dead time unit and an output polarity switching unit. The dead time unit consists of the edge detection block, timer block, dead time insert block, and dead time correction block. (Refer to "Figure 3.7 Dead Time Circuit")

For each of the U-, V-, and W-phases, the dead -time units delay the ON-timing of each phase when the upper-phase and lower-phase are switched to prevent a short circuit. The dead time is set to the Dead Time Register (*[PMDxDTR]* <DTR[7:0]>) as an 8-bit value with a resolution of 8/fsys can be set.

The output polarity switching circuit allows the polarity (active high or active low) of the upper-output (UOx, VOx, WOx) and lower-output (XOx, YOx, ZOx) phases to be independently set through PMD output setting register *[PMDxMDPOT]*<POLH> and <POLL>.

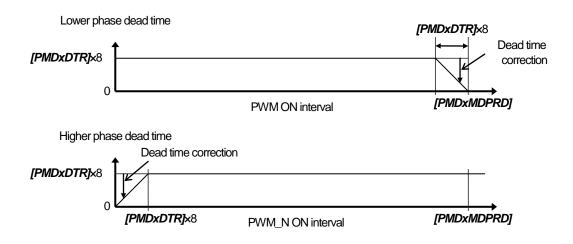

In the dead time correction block, when one of the on-period of the upper PWM or the lower PWM is 0 width, if *[PMDxMDCR]*<DTCREN> is set to "1", the other PWM delay time is corrected to be shortened. If the PWM signal is OFF during the dead time period, the delay time of the counter phase is shortened in the rest of dead time (dead time register setting time - ON time). When the upper PWM becomes OFF during the dead time period, the delay time of the lower PWM becomes OFF during the dead time period, the delay time of the lower PWM should be corrected to be shortened. When the lower PWM becomes OFF during the dead time period, the delay time of the upper PWM should be corrected to be shortened. Figure 3.8 shows dead time correction. A delay time is corrected in the vicinity of duty of 100% of the upper PWM and it also is corrected in the vicinity of duty of 0%.

Figure 3.8 Dead Time Correction

### 3.6. Synchronous Trigger Generation Circuit

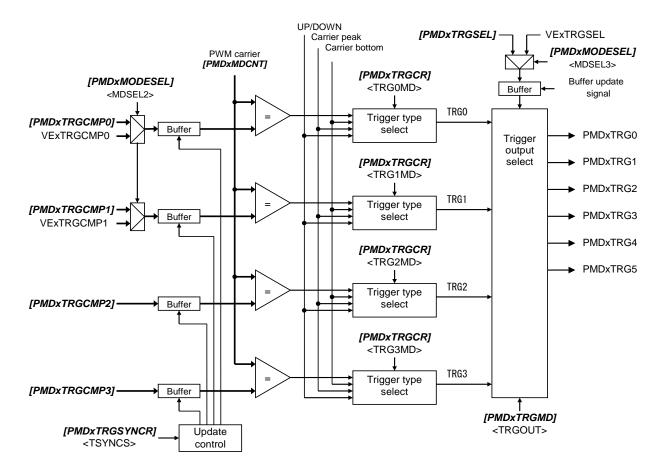

Figure 3.9 Synchronous Trigger Generation Circuit

The synchronous trigger generation circuit generates four trigger signals (TRG0 to TRG3) for starting ADC sampling in synchronization with PWM. When VE mode is selected in *[PMDxMODESEL]*<MDSEL2>, *[PMDxTRGCMP0]* and *[PMDxTRGCMP1]* are switched to VExTRGCMP0 and VExTRGCMP1 in the VE register output.

The trigger timing can be selected following 6 types.

- (1) At up count operation compare-match (Note1)(Note2)

- (2) At down count operation compare-match (Note1)(Note3)

- (3) At up/down count operation compare-match (Note1)(Note3)(Note4)

- (4) PWM carrier peak

- (5) PWM carrier bottom(Note3)

- (6) PWM carrier peak and PWM carrier bottom(Note3)

- Note1: The compare-match is between PWM counter ([PMDxMDCNT]) and ([PMDxTRGCMPn](n=0 to 3))

- Note2: If PWM is started while [*PMDxTRGCMPn*](n=0 to 3) is set to "0x0001" with saw-tooth wave carrier(<PWMMD>=0), there is no trigger output in the first PWM cycle.

- Note3: When saw-tooth wave carrier(<PWMMD>=0) is selected, it cannot be selected.

- Note4: When trigger output at up/down-count match, [PMDxTRGCMPn](n=0 to 3)=0x0001 and triangular wave (<PWMMD>=1),one trigger output is made per period.

During in trigger select output mode: [*PMDxTRGMD*]<TRGOUT>=1. The TRG0 signal is output from ADC synchronous trigger ([*PMDxTRG0*] to [*PMDxTRG5*]) selected by the trigger output select register [*PMDxTRGSEL*] / VExTRGSEL. The TRG0 setting is set by [*PMDxTRGCMP0*] / VExTRGCMP0 and [*PMDxTRGCR*]<TRG0MD>. (Refer to "Table 4.4 Trigger Output Patterns".)

When *[PMDxTRGMD]*<EMGTGE>=1, this circuit outputs trigger signals in EMG protection state.

An example of using the synchronization trigger generation circuit is shown below.

• In the case of 3-shunt

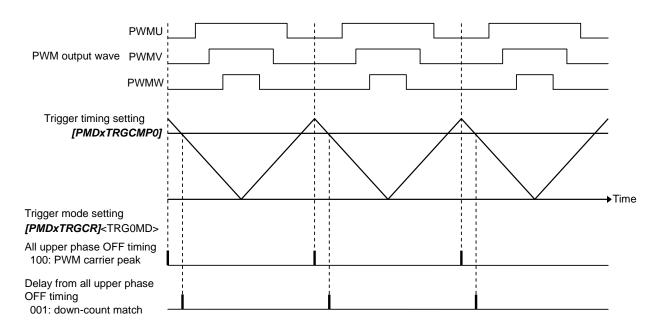

Figure 3.10 Example of using the PMD trigger at 3-shunt

Trigger output mode setting ([PMDxTRGMD]<TRGOUT>) is set to "1"(Trigger selection output).

Trigger mode setting 0 (*[PMDxTRGCR]*<TRG0MD>) is set to "100"(Trigger output at PWM carrier peak), when trigger is generated at the timing of all upper-phases OFF. Trigger mode setting 1 (*[PMDxTRGCR]*<TRG1MD>) is set to "001"(Trigger output at down-count match) and *[PMDxTRGCMP0]* is set to delay timing, when delayed trigger is generated at the timing of all upper-phases OFF.

By setting trigger output select (*[PMDxTRGSEL]*<TRGSEL>) according to the position (sector) of the motor, it is possible to generate six kinds of triggers for each sector.

• In the case of 1-shunt

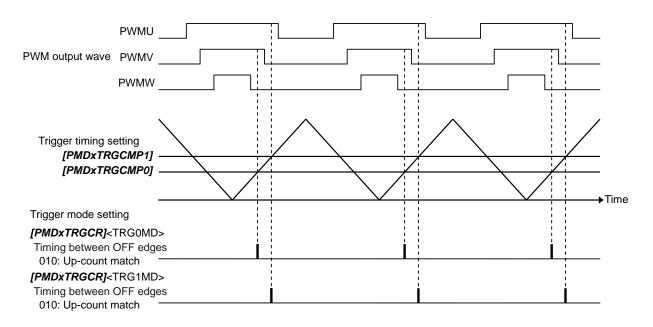

Figure 3.11 Example of using the PMD trigger at 1-shunt

Trigger output mode setting (*[PMDxTRGMD]*<TRGOUT>) is set to "0"(Fixed trigger output). Trigger mode setting 0 and 1(*[PMDxTRGCR]*<TRG0MD>,<TRG1MD>) is set to "010"(Trigger output at up-count match), when trigger is generated at the timing between OFF edges. Or trigger mode setting 0 and 1(<TRG0MD>, <TRG1MD>) is set to "001"(Trigger output at down-count match), when trigger is generated at the timing between OFF edges.

The previous trigger is set to [PMDxTRGCMP0], and the subsequent trigger is set to [PMDxTRGCMP1].

## 4. Registers

## 4.1. List of Registers

The following table lists the control registers and their addresses:

| Designation News                        | Channal/Ulnit | Base Address |            |            |            |

|-----------------------------------------|---------------|--------------|------------|------------|------------|

| Peripheral Function Name                |               | Channel/Unit | TYPE1      | TYPE2      | TYPE3      |

| Programmable Motor Control Circuit Plus | PMD+          | ch0          | 0x400F6000 | 0x400E9000 | 0x40089000 |

|                                         |               | ch1          | 0x400F6100 | 0x400E9400 | 0x40089400 |

|                                         |               | ch2          | 0x400F6200 | 0x400E9800 | 0x40089800 |

|                                         |               | ch3          | —          | 0x400E9C00 | 0x40089C00 |

Note: The Channel/Unit and Base address type are different by products. Please refer to "Product Information" of the reference manual for the details.

| Register Name                          | Address(Base+) |        |

|----------------------------------------|----------------|--------|

| PMD Enable Register                    | [PMDxMDEN]     | 0x0000 |

| Port Output Mode Register              | [PMDxPORTMD]   | 0x0004 |

| PMD Control Register                   | [PMDxMDCR]     | 0x0008 |

| PWM Counter Status Register            | [PMDxCNTSTA]   | 0x000C |

| PWM Counter Register                   | [PMDxMDCNT]    | 0x0010 |

| PWM Period Register                    | [PMDxMDPRD]    | 0x0014 |

| PMD Compare U Register                 | [PMDxCMPU]     | 0x0018 |

| PMD Compare V Register                 | [PMDxCMPV]     | 0x001C |

| PMD Compare W Register                 | [PMDxCMPW]     | 0x0020 |

| Mode Selection Register                | [PMDxMODESEL]  | 0x0024 |

| PMD Conduction Control Register        | [PMDxMDOUT]    | 0x0028 |

| PMD Output Setting Register            | [PMDxMDPOT]    | 0x002C |

| EMG Release Register                   | [PMDxEMGREL]   | 0x0030 |

| EMG Control Register                   | [PMDxEMGCR]    | 0x0034 |

| EMG Status Register                    | [PMDxEMGSTA]   | 0x0038 |

| OVV Control Register                   | [PMDxOVVCR]    | 0x003C |

| OVV Status Register                    | [PMDxOVVSTA]   | 0x0040 |

| Dead time Register                     | [PMDxDTR]      | 0x0044 |

| Trigger Compare 0 Register             | [PMDxTRGCMP0]  | 0x0048 |

| Trigger Compare 1 Register             | [PMDxTRGCMP1]  | 0x004C |

| Trigger Compare 2 Register             | [PMDxTRGCMP2]  | 0x0050 |

| Trigger Compare 3 Register             | [PMDxTRGCMP3]  | 0x0054 |

| Trigger Control Register               | [PMDxTRGCR]    | 0x0058 |

| Trigger Output Mode Setting Register   | [PMDxTRGMD]    | 0x005C |

| Trigger Output Select Register         | [PMDxTRGSEL]   | 0x0060 |

| Trigger Update Timing Setting Register | [PMDxTRGSYNCR] | 0x0064 |

## 4.2. Details of Registers

#### 4.2.1. [PMDxMDEN] (PMD Enable Register)

| Bit  | Bit Symbol | After reset | Туре | Function                                                                           |

|------|------------|-------------|------|------------------------------------------------------------------------------------|

| 31:1 | —          | 0           | R    | Read as "0".                                                                       |

| 0    | PWMEN      | 0           | R/W  | Enables or disables waveform synthesis.(Note1), (Note2)<br>0: Disable<br>1: Enable |

Note1: When the port is set to a function output (PMD output), the port disables output (High-impedance) by setting <PWMEN>=0. For details of a port setting, refer to "Input/Output Ports" of the reference manual.

Note2: <PWMEN>=1 should be set after initial settings other than <PWMEN> like an output polarity are set.

#### 4.2.2. [PMDxPORTMD] (Port Output Mode Register)

| Bit  | Bit Symbol  | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|-------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:2 | —           | 0           | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1:0  | PORTMD[1:0] | 00          | R/W  | Port control setting when a debug halt occurs<br>(Note1)(Note2)(Note3)<br>00: Upper-phases High-impedance / lower-phases<br>High-impedance<br>01: Upper-phases High-impedance / lower-phases PMD output<br>10: Upper-phases PMD output / lower-phases High-impedance<br>11: Upper-phases PMD output / lower-phases PMD output<br>Sets the port output for both upper-phases (UOx/VOx/WOx) and<br>the lower-phases (XOx/YOx/ZOx) when a debug halt occurs in<br>the use of ports for function output (PMD output).<br>When a debug halt occurs while High-impedance is selected, the<br>ports are disabled to output (High-impedance).<br>In other cases, external port outputs depend on PMD outputs. |

Note1: When *[PMDxMDEN]*<PWMEN>=0, output ports are disabled to output (High-impedance) regardless of the <PORTMD[1:0]> setting.

Note2: Depending on the setting of *[PMDxEMGCR]*<EMGMD[1: 0]>, port output control is also performed during EMG protection.

Note3: For details of a port setting, refer to "Input/Output Ports" of the reference manual.

#### 4.2.3. [PMDxMODESEL] (Mode Selection Register)

| Bit  | Bit Symbol | After<br>Reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 |            | 0              | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7    | DCMPEN     | 0              | R/W  | Enables auto switching between VE register and PMD register (Note1)<br>0: Two register switching disable<br>(only uses <mdsel0> setting register)<br/>1: Two register switching enabled<br/>(switches between the first half and last half of PWM period)<br/>This bit is enabled in case of <mdsel0>=1.<br/>This bit is enabled when a triangular wave carrier is selected<br/>([PMDxMDCR]<pwmmd>=1).</pwmmd></mdsel0></mdsel0> |

| 6:4  |            | 0              | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3    | MDSEL3     | 0              | R/W  | Mode selection 3<br>0: Bus mode (uses PMD register: <i>[PMDxTRGSEL]</i> )<br>1: VE mode (uses VE register: <i>[VExTRGSEL]</i> )<br><i>[PMDxTRGSEL]</i> / VExTRGSEL register selection                                                                                                                                                                                                                                            |

| 2    | MDSEL2     | 0              | R/W  | Mode selection 2<br>0: Bus mode<br>(uses PMD register: [PMDxTRGCMP0] and [PMDxTRGCMP1])<br>1: VE mode<br>(uses VE registers: [VExTRGCMP0] and [VExTRGCMP1])<br>[PMDxTRGCMP0] / VExTRGCMP0 and [PMDxTRGCMP1] /<br>VExTRGCMP1 registers selection                                                                                                                                                                                  |

| 1    | MDSEL1     | 0              | R/W  | Mode selection 1<br>0: Bus mode (uses PMD register: <i>[PMDxMDOUT]</i> )<br>1:VE mode (uses VE register: <i>[VExOUTCR]</i> )<br><i>[PMDxMDOUT]</i> / VExOUTCR register selection                                                                                                                                                                                                                                                 |

| 0    | MDSEL0     | 0              | R/W  | Mode selection 0<br>0: Bus mode<br>(uses PMD registers: [PMDxCMPU]/[PMDxCMPV] and<br>[PMDxCMPW])<br>1: VE mode<br>(uses VE registers: [VExCMPU] / [VExCMPV] / [VExCMPW]<br>registers selection and [VExEMGRS] register enable setting)                                                                                                                                                                                           |

Note1: When auto switching to VE register is enabled, set "1" to [VExEN] and [VExREPTIME], to use VE register ([VExCMPU], [VExCMPV], and [VExCMPV]).

Note2: For details of VE, refer to the reference manual, "Advanced Vector Engine".

#### 4.2.4. [PMDxMDCR] (PMD Control Register)

| Bit   | Bit Symbol  | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | _           | 0           | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15:14 | WPWMES[1:0] | 00          | R/W  | W-phase edge setting (Note1)<br>00: Edge unfixed (center-aligned PWM)<br>01: Reserved<br>10: PWM rising-edge fixed (to the PWM carrier bottom)<br>11: PWM falling-edge fixed (to the PWM carrier bottom)                                                                                                                                                                                                                                                                                   |

| 13:12 | VPWMES[1:0] | 00          | R/W  | V-phase edge setting (Note1)<br>00: Edge unfixed (center-aligned PWM)<br>01: Reserved<br>10: PWM rising-edge fixed (to the PWM carrier bottom)<br>11: PWM falling-edge fixed (to the PWM carrier bottom)                                                                                                                                                                                                                                                                                   |

| 11:10 | UPWMES[1:0] | 00          | R/W  | U-phase edge setting (Note1)<br>00: Edge unfixed (center-aligned PWM)<br>01: Reserved<br>10: PWM rising-edge fixed (to the PWM carrier bottom)<br>11: PWM falling-edge fixed (to the PWM carrier bottom)                                                                                                                                                                                                                                                                                   |

| 9:8   | DSYNCS[1:0] | 00          | R/W  | <ul> <li>Double-buffer update timing for the PWM compare register and PWM period register. (Note2)(Note3)</li> <li>00: Depends on interrupt period setting (refer to the Table 4.1) Updates at the carrier peak and carrier bottom when 0.5 PWM period is selected (<intprd>=00). Otherwise, updates at the carrier peak.</intprd></li> <li>01: Updates at PWM carrier bottom</li> <li>10: Updates at PWM carrier peak</li> <li>11: Updates at both PWM carrier peak and bottom</li> </ul> |

| 7     | DTCREN      | 0           | R/W  | Set a dead time correction.<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6     | PWMCK       | 0           | R/W  | PWM period extension mode<br>0: Normal period<br>1: 4 × period<br>Sets the counting period of the PWM counter.<br>Normal period setting:<br>Saw-tooth wave 1/fsys / Triangular wave 2/fsys<br>4 × period setting:<br>Saw-tooth wave 4/fsys / Triangular wave 8/fsys                                                                                                                                                                                                                        |

| 5     | SYNTMD      | 0           | R/W  | Port output mode setting<br>Port outputs are controlled by a combination of <b>[PMDxMDOUT]</b><br><noc>,<npwm>, <b>[PMDxMDPOT]</b><polh>, <poll> and<br/><syntmd> (refer to Table 4.2).</syntmd></poll></polh></npwm></noc>                                                                                                                                                                                                                                                                |

| 4     | DTYMD       | 0           | R/W  | Duty mode selection<br>0: 3-phase common mode<br>1: 3-phase independent mode<br>Select whether to set the duty setting independently for each<br>phase of <i>[PMDxCMPU/V/W]</i> , or to use the <i>[PMDxCMPU]</i> register<br>as common 3 phases.                                                                                                                                                                                                                                          |

| 3     | PINT        | 0           | R/W  | <ul> <li>PWM interrupt request timing selection (Note4)(Note5)</li> <li>0: Interrupt request occurs at PWM carrier bottom (<i>[PMDxMDCNT]</i> =0x0001).</li> <li>1: Interrupt request occurs at PWM carrier peak (<i>[PMDxMDCNT]</i> = <i>[PMDxMDPRD]</i>).</li> </ul>                                                                                                                                                                                                                     |

| Bit | Bit Symbol  | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:1 | INTPRD[1:0] | 00          | R/W  | PWM interrupt request period selection<br>00: Interrupt request at every 0.5 PWM period (Note6)(Note7)<br>01: Interrupt request at every PWM period<br>10: Interrupt request at every two PWM periods<br>11: Interrupt request at every four PWM periods<br>This field selects the PWM interrupt request period from 0.5 PWM<br>period, one PWM period, two PWM periods and four PWM<br>periods. |

| 0   | PWMMD       | 0           | R/W  | PWM carrier waveform selection<br>0: PWM mode 0 (edge-aligned PWM and saw-tooth wave)<br>1: PWM mode 1(center-aligned PWM and triangular wave)                                                                                                                                                                                                                                                   |

Note1: Valid when triangular carrier PWM is selected (<PWMMD>=1).

- Note2: Updates at carrier peak when saw-tooth wave carrier is selected (<PWMMD>=0) regardless of the setting.

- Note3: When [*PMDxMDEN*]<PWMEN>=0, updates asynchronously regardless of setting.

- Note4: Interrupt request occurs at carrier peak when the PWM carrier is saw-tooth wave (<PWMMD>=0).

- Note5: Interrupt request occurs both at carrier peak and carrier bottom when the interrupt period is 0.5 period (<INTPRD>=00).

- Note6: PWM interrupt request period can be configured only when the PWM carrier is triangular wave (<PWMMD>=1)

- Note7: The subsequent stage of the double-buffer of the compare registers (*[PMDxCMPU/V/W]*) and the period register (*[PMDxMDPRD]*) are updated by peak and bottom of the PWM carrier.

| Table 4.1 | [PMDxMDPRD], [PMDxCMPU/V/W] buffer Update Timing |

|-----------|--------------------------------------------------|

|-----------|--------------------------------------------------|

| Settings          |                   | Undoto Timing                                      |

|-------------------|-------------------|----------------------------------------------------|

| <dsyncs></dsyncs> | <intprd></intprd> | - Update Timing                                    |

|                   | 1x                | Updates at PWM carrier peak                        |

| 00                | x1                | Updates at PWM carrier peak                        |

|                   | 00                | Updates at PWM carrier peak and PWM carrier bottom |

| 01                | xx                | Updates at PWM carrier bottom                      |

| 10                | хх                | Updates at PWM carrier peak                        |

| 11                | хх                | Updates at PWM carrier peak and PWM carrier bottom |

Note: x: Don't care

#### 4.2.5. [PMDxCNTSTA] (PWM Counter Status Register)

| Bit  | Bit Symbol | After reset | Туре | Function                                                                                                                                        |

|------|------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:1 | —          | 0           | R    | Read as "0".                                                                                                                                    |

| 0    | UPDWN      | 0           | R    | PWM counter flag (Note)<br>0: Up-counting<br>1: Down-counting<br>This bit indicates whether the PWM counter is up-counting or<br>down-counting. |

Note: The PWM carrier is a saw-tooth wave ([PMDxMDCR]<PWMMD>=0), a zero is always read.

#### 4.2.6. [PMDxMDCNT] (PWM Counter Register)

| Bit   | Bit Symbol                                                                                       | After reset | Туре | Function                                                                                                                                                                                                                                                         |

|-------|--------------------------------------------------------------------------------------------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | —                                                                                                | 0           | R    | Read as "0".                                                                                                                                                                                                                                                     |

| 15:0  | MDCNT[15:0]                                                                                      | 0x0000      | R    | PWM counter(Note)<br>A value can be read from the up-down counter generating a PWM<br>carrier wave.<br>Counter resolution: 1/fsys<br>When a 4 × period mode is selected<br>( <i>[PMDxMDCR]</i> <pwmck>=1), time resolution of the counter is<br/>4/fsys.</pwmck> |

| Note: | Depending on the setting of the PWM carrier ([PMDxMDCR] <pwmmd>), the PWM counter values</pwmmd> |             |      |                                                                                                                                                                                                                                                                  |

Note: Depending on the setting of the PWM carrier ([PMDxMDCR]<PWMMD>), the PWM counter values when PMD is disabled ([PMDxMDEN]<PWMEN>=0) are as follows: In case of [PMDxMDCR]<PWMMD>=0: 0x0001 In case of [PMDxMDCR]<PWMMD>=1: the value of [PMDxMDPRD]

#### 4.2.7. [PMDxMDPRD] (PWM Period Register)

| Bit   | Bit Symbol  | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | —           | 0           | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15:0  | MDPRD[15:0] | 0x0000      | R/W  | PWM period<br>[PMDxMDPRD] ≥ 0x0010 (Note1)<br>By the combination of the PWM period extension mode<br>([PMDxMDCR] <pwmck>) and the PWM carrier waveform<br/>[PMDxMDCR]<pwmmd>, the PWM period can be calculated as<br/>follows:<br/>When <pwmck>=0, <pwmmd>=0: [PMDxMDPRD] × 1/fsys<br/><pwmmd>=1: [PMDxMDPRD] × 2/fsys<br/>When <pwmck>=1, <pwmmd>=0: [PMDxMDPRD] × 4/fsys<br/><pwmmd>=1: [PMDxMDPRD] × 8/fsys</pwmmd></pwmmd></pwmck></pwmmd></pwmmd></pwmck></pwmmd></pwmck> |

Note1: If *[PMDxMDPRD]* is set to a value less than "0x0010", it is automatically assumed to be "0x0010". (The register retains the actual value that is written.)

Note2: Do not write to this register in byte unit. If the upper 8 bits [15:8] and the lower 8 bits [7:0] are written separately, operation cannot be guaranteed.

Note3: Since the *[PMDxMDPRD]* register is double-buffered, the PWM period can be changed during the operation of the PWM counter.

Note4: For detailed update timing of the subsequent stage buffer, refer to the "Table 4.1 *[PMDxMDPRD]*, *[PMDxCMPU/V/W*] buffer Update Timing".

Note5: Read value is the first buffer value (the latest data set via a bus).

#### 4.2.8. [PMDxCMPU] (PWM Compare U Register)

| Bit   | Bit Symbol | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | —          | 0           | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15:0  | CMPU[15:0] | 0x0000      | R/W  | PWM pulse width of U Phase (Note1)<br>0x0000 through 0xFFF<br><cmpu> are compare registers for determining the output pulse<br/>width of the U-phase. These registers are double-buffered. Pulse<br/>width is determined by comparing the subsequent stage buffer<br/>and the PWM counter to evaluate which is small or large.<br/>By the combination of the PWM period extension mode<br/>(<i>[PMDxMDCR]</i><pwmck>) and the PWM carrier waveform<br/>(<i>[PMDxMDCR]</i><pwmmd>), the pulse width can be calculated as<br/>follows:<br/>When <pwmck>=0, <pwmmd>=0: <i>[PMDxCMPU]</i> × 1/fsys<br/><pwmmd>=1: <i>[PMDxCMPU]</i> × 4/fsys<br/><pwmmd>=1: <i>[PMDxCMPU]</i> × 8/fsys</pwmmd></pwmmd></pwmmd></pwmck></pwmmd></pwmck></cmpu> |

Note1: When [PMDxCMPU] > [PMDxMDPRD], the duty is 100%.

Note2: When the compare register updated by the bus is loaded to the subsequent stage buffer, set the bus mode (default) by writing "0" to *[PMDxMODESEL]*<MDSEL0>.

Note3: Do not write to this register in byte unit. If the upper 8 bits [15:8] and the lower 8 bits [7:0] are written separately, operation cannot be guaranteed.

Note4: Since the *[PMDxCMPU]* register is double-buffered, the PWM pulse width can be changed during the operation of the PWM counter.

- Note5: For detailed update timing of the subsequent stage buffer, refer to the "Table 4.1 *[PMDxMDPRD]*, *[PMDxCMPU/V/W]* buffer Update Timing".

- Note6: Read value is the first buffer value (the latest data set via a bus).

#### 4.2.9. [PMDxCMPV] (PWM Compare V Register)

| Bit   | Bit Symbol | After reset | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | —          | 0           | R    | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |