#### **Dear Cutomers**,

# Datasheet Correction: I2C function of TX/TXZ Family

This informs you that we found the following corrections should be made to the datasheets as shown below. If you have any questions or require any further information, please contact your local Toshiba representatives.

# 1. Products

# M3H Group(1)

|            | TMPM3H0FS<br>TMPM3H1FP<br>TMPM3H3FU<br>TMPM3H5FW<br>TMPM3H6FS | TMPM3H0FM<br>TMPM3H2FW<br>TMPM3H3FS<br>TMPM3H5FU | TMPM3H1FW<br>TMPM3H2FU<br>TMPM3H4FW<br>TMPM3H5FS | TMPM3H1FU<br>TMPM3H2FS<br>TMPM3H4FU<br>TMPM3H6FW | TMPM3H1FS<br>TMPM3H3FW<br>TMPM3H4FS<br>TMPM3H6FU |

|------------|---------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| <u>M3H</u> | Group(2)                                                      |                                                  |                                                  |                                                  |                                                  |

|            | TMPM3HLFY<br>TMPM3HMFD<br>TMPM3HPFZ                           | TMPM3HLFZ<br>TMPM3HNFY<br>TMPM3HPFD              | TMPM3HLFD<br>TMPM3HNFZ<br>TMPM3HQFY              | TMPM3HMFY<br>TMPM3HNFD<br>TMPM3HQFZ              | TMPM3HMFZ<br>TMPM3HPFY<br>TMPM3HQFD              |

| <u>M4G</u> | Group(1)                                                      |                                                  |                                                  |                                                  |                                                  |

|            | TMPM4G9F15<br>TMPM4G8F10<br>TMPM4G7FD                         | TMPM4G9F10<br>TMPM4G8FE<br>TMPM4G6F10            | TMPM4G9FE<br>TMPM4G8FD<br>TMPM4G6FE              | TMPM4G9FD<br>TMPM4G7F10<br>TMPM4G6FD             | TMPM4G8F15<br>TMPM4G7FE                          |

| <u>M06</u> | ) Group                                                       |                                                  |                                                  |                                                  |                                                  |

|            | TMPM066FW                                                     | TMPM067FW                                        | TMPM068FW                                        |                                                  |                                                  |

# 2. Corrections

The function of I<sup>2</sup>C use are changed as following.

Note : This information explains the correction using the M3H Group(1) product.

#### <Correction 1: Analog Noise Filter>

## **Register descriptions**

[Old]

# 4.2.9. [I2CxOP] (Expanded function setting register)

| Bit  | Bit Symbol | After<br>reset | Туре | Function                                                                                                                                       |

|------|------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | -          | 0              | R    | Read as "0".                                                                                                                                   |

| 7    | DISAL      | 0              | R/W  | Control the Arbitration Lost detected function<br>0: Enable Arbitration Lost detect function<br>1: Disable Arbitration Lost detect function    |

| 6    | SA2ST      | 0              | R    | Discriminates the received slave address. (Updated when <aas>=1.)<br/>0: Not match <sa2><br/>1: Matches <sa2></sa2></sa2></aas>                |

| 5    | SAST       | 0              | R    | Discriminates the received slave address. (Updated when <aas>=1.)<br/>0: Not match <sa><br/>1: Matches <sa></sa></sa></aas>                    |

| 4    | NFSEL      | 0              | R/W  | Select Noise cancellation ( it also Changed the communication speed )<br>0: Digital<br>1: Analog                                               |

| 3    | RSTA       | 0              | R    | Detects a Repeated START flag<br>0: Not detected<br>1: Detected                                                                                |

|      |            |                | W    | 0: Clear<br>1: Invalid                                                                                                                         |

| 2    | GCDI       | 0              | R/W  | Sets general-call detection. (Valid only when <noack>=0)<br/>0: Detection is ON.<br/>1: Detection is OFF.</noack>                              |

| 1    | SREN       | 0              | R    | Sets the repeated START output. (Valid only when the MCU in master mode.)<br>0: Repeated START has completed.<br>1: Repeated START is ongoing. |

|      |            |                | W    | 0: Invalid<br>1: Repeted start requeset                                                                                                        |

| 0    | MFACK      | 0              | R/W  | Selects an ACK Output.<br>0: ACK Output<br>1: NACK Output<br>Be careful, It cannot be used in a free data format.                              |

#### [New]

## 4.2.9. [I2CxOP] (Expanded function setting register)

| Bit  | Bit Symbol | After<br>reset | Туре | Function                                                                                                                                       |

|------|------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | -          | 0              | R    | Read as "0".                                                                                                                                   |

| 7    | DISAL      | 0              | R/W  | Control the Arbitration Lost detected function<br>0: Enable Arbitration Lost detect function<br>1: Disable Arbitration Lost detect function    |

| 6    | SA2ST      | 0              | R    | Discriminates the received slave address.<br>0: Not match <sa2><br/>1: Matches <sa2></sa2></sa2>                                               |

| 5    | SAST       | 0              | R    | Discriminates the received slave address.<br>0: Not match <sa><br/>1: Matches <sa></sa></sa>                                                   |

| 4    | NFSEL      | 0              | R/W  | Select Noise cancellation<br>0: Digital<br>1: Can not be set, Only Write as "0".                                                               |

| 3    | RSTA       | 0              | R    | Detects a Repeated START flag<br>0: Not detected<br>1: Detected                                                                                |

|      |            |                | w    | 0: Clear (Note1)<br>1: Invalid                                                                                                                 |

| 2    | GCDI       | 0              | R/W  | Sets general-call detection. (Valid only when <noack>=0)<br/>0: Detection is ON.<br/>1: Detection is OFF.</noack>                              |

| 1    | SREN       | 0              | R    | Sets the repeated START output. (Valid only when the MCU in master mode.)<br>0: Repeated START has completed.<br>1: Repeated START is ongoing. |

|      |            |                | W    | 0: Invalid<br>1: Repeted start requeset                                                                                                        |

| 0    | MFACK      | 0              | R/W  | Selects an ACK Output.<br>0: ACK Output<br>1: NACK Output<br>Be careful, It cannot be used in a free data format.                              |

\* For more other items, deleted the contents about the Analog Noise Filter.

<Correction 2: Repeated Start detection Flag>

Functional Description [Old]

#### 3.3.12. Repeated start detection

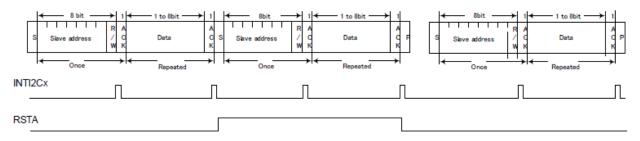

When a repeated START is detected on the bus line, *[I2CxOP]* <RSTA> is set to "1". A repeated start is used for a master device to change the direction of transmission without terminating data transfer to a slave device.

The <RSTA> is initialized by a reset and stop condition.

[New]

#### 3.3.12. Repeated start detection

In slave mode, when a repeated START is detected on the bus line, *[I2CxOP]* <RSTA> is set to "1". A repeated start is used for a master device to change the direction of transmission without terminating data transfer to a slave device.

Since <RSTA> is only initialized by a reset, clear the flag(<RSTA>=0) when stop condition occurs, bus free,.etc. (refer to Figure 3.14)

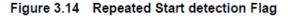

In case [I2CxPRS]<PRSCK>  $\neq$  1 in Master mode, <RSTA> is set to "1" after the first start condition after reset. Perform clear processing at the first INTI2Cx interrupt service routine, etc. (refer to Figure 3.15)

Figure 3.15 Repeated Start detection Flag (Master mode:<PRSCK>≠1)

<Correction 3: Hold time and Setup time>

Functional Description [Old]

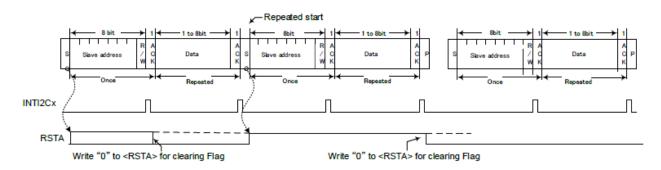

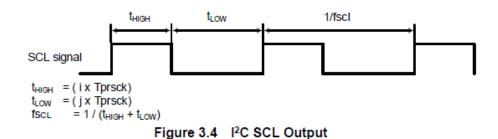

Note: The t<sub>HIGH</sub> period may differ from the specified value if the rising edge becomes blunt depending on the combination of bus load capacitance and pull-up register. If the clock synchronization function for synchronizing clocks from multiple clocks is used, the actual clock period may differ from the specified setting.

In master mode, the hold time when start conditions generated and the setup time when a stop condition is generated are defined as  $t_{HIGH}[s]$

[New]

Note: The t<sub>HIGH</sub> period may differ from the specified value if the rising edge becomes blunt depending on the combination of bus load capacitance and pull-up register. If the clock synchronization function for synchronizing clocks from multiple clocks is used, the actual clock period may differ from the specified setting.

In master mode, the hold time when start conditions generated and the setup time when a stop condition is generated are defined as the following.

Hold time:

```

[I2CxOP]<SREN>=0: t<sub>HIGH</sub> [S]

```

[I2CxOP]<SREN>=1: 8Tprsck [S]

Setup time:

[I2CxPRS]<PRSCK>=1: t<sub>HIGH</sub> [S]

[I2CxPRS]<PRSCK>#1: tHIGH - Tprsck [S]

# TOSHIBA

<Correction 4: I2CxCR registger>

Registers Descriptions [Old]

# 4.2.4. [I2CxCR2] (I<sup>2</sup>C control register 2)

| 2   | -          | 0  | R | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SWRES[1:0] | 00 | W | Software reset generation<br>Write "10" followed by "01" to generate a reset.<br>Writing "10" followed by "01" into this 2bits generates a software reset.(reset<br>width is 1 clock as fsys)<br>A software reset release the SCL and SDA lines (High state) if the device is<br>data transfer and break the communication.<br>The I <sup>2</sup> C bus interface is initialized except <i>[I2CxCR2]</i> <i2cm> and <i>[I2CxDBR]</i><br/>register<br/>When software reset is performed, make sure to write "0" to <i>[I2CxCR2]</i>[7:4]</i2cm> |

Note: the [I2CxCR2]<MST>,<TRX>,<BB>,<PIN> bits are given independent functions, they are used in

typical combinations, as shown below, according to the [I2CxSR] setting.

When writing to these bits, make sure that notice.

#### [New]

# 4.2.4. [I2CxCR2] (I<sup>2</sup>C control register 2)

| 2   | -          | 0  | R | Read as "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|------------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | SWRES[1:0] | 00 | W | Software reset generation<br>Write "10" followed by "01" to generate a reset.<br>Writing "10" followed by "01" into this 2bits generates a software reset.(reset<br>width is 1 clock as fsys)<br>A software reset release the SCL and SDA lines (HIGH state) if the device is<br>data transfer and break the communication.<br>The I <sup>2</sup> C bus interface is initialized except <i>[I2CxCR2]</i> <i2cm> and <i>[I2CxDBR]</i><br/>register<br/>When software reset is performed, make sure to write "0" to <i>[I2CxCR2]</i>[7:4]</i2cm> |

Note: the *[I2CxCR2]*<MST>,<TRX>,<BB>,<PIN> bits are given independent functions, they are used in typical combinations, as shown below, according to the *[I2CxSR]* setting. When writing to these bits, make sure that notice.

Note: Don't change the contents of the registers, except *[I2CxCR2]*<SWRST[1:0]>, when the start condition is generated, the stop condition is generated or the data transfer is in progress. Write data to the registers before the start condition is generated or during the period from when an interrupt request is generated for stopping the data transfer until it is released.