# LDO の発振原理と発振耐性向上について

## 概要

本資料は ロードロップアウトレギュレータ (LDO) やオペアンプを使用した負帰還回路がなぜ発振するのか? どのように発振を抑制 (位相補償) しているのか について解説します。

また、出力を決定できる可変電圧タイプ LDO の位相補償容量 ( CFB ) の発振耐性改善効果についても説明 し、セット設計で LDO を安定動作させつつ、その性能を最大限に引き出すことを可能にするための有益な情報を提供 致します。

# LDO の発振原理と発振耐性向上について Application Note

# 目次

| 1. はじめに                                                      | 3  |

|--------------------------------------------------------------|----|

| 2. LDO の発振とその影響                                              | 4  |

| 3. 負帰還の原理                                                    | 5  |

| 3.1 負帰還とは? 〜負帰還のメリット                                         | 5  |

| 3.2 負帰還のクローズドループゲインとループゲイン                                   | 7  |

| 4. LDO(負帰還システム)が発振するメカニズム                                    | 8  |

| 4.1 LDO の発振メカニズム                                             | 8  |

| 4.2 位相余裕とゲイン余裕                                               | 10 |

| 5. LDO の位相補償 ~発振させないために                                      | 11 |

| 5.1 LDO 内部の位相補償の方法                                           | 11 |

| 5.1.1 ミラー補償                                                  | 11 |

| 5.1.2 不安定な零(RHP Zero)とそれによる発振を回避する Lag-Lead 形式の位相補           | 甫償 |

|                                                              | 12 |

| 5.1.3 LDO 外部に大きい出力コンデンサがある場合の位相補償 ~零の追加                      | 13 |

| 5.2 LDO 外部の位相補償の方法                                           | 15 |

| 5.2.1 出力コンデンサの直列等価抵抗:ESR(R <sub>ESR</sub> )を利用して零:fz を追加する方法 | 15 |

| 6. 可変電圧タイプ LDO における外付け位相補償容量:C <sub>FB</sub> の効果             | 16 |

| 7. まとめ                                                       | 19 |

| 8. 関連リンク                                                     | 20 |

| 9. 製品取り扱い上のお願い                                               | 21 |

# LDO の発振原理と発振耐性向上について Application Note

#### 1. はじめに

ますます高性能化されるモバイル機器やその他の電子機器には、その高性能/高機能を実現するためにさまざまな半導体部品(電子デバイス)が使用されています。それら昨今の半導体部品は、高性能を実現すべく非常に速い動作速度を持っていますが、それを実現する方法として一般的に IC 内部の増幅器のゲインを高め、周波数特性を高周波領域まで伸ばすなどの設計手法が取られています。しかしこれら高性能半導体部品が負帰還を掛けた回路を持っている場合、出力端子に正規の出力信号とは違った意図しない周期的な交流(AC)電圧が出力されることがあり、電子機器の動作を破綻させてしまうことがあります。このような現象を発振と呼び、例えば、LDO が制御不能な AC 電圧を出力するなどの現象を引き起こします。

LDO やオペアンプは基本的にこの発振現象が起こらないように設計されていますが、一部の可変電圧タイプの LDO の発振耐性を強化する場合や内部で位相補償がなされていないオペアンプなどではセット設計で位相補償を施す必要が生じる場合があります。

また、位相補償が内部でなされている LDO やオペアンプでも電源や GND などの共通インピーダンスやプリント基板の配線容量の影響で発振することがあるため、注意が必要です。そこで本資料は、セット設計で LDO を安定動作させつつ、その性能を最大限に引き出すことを可能にするための一助として、発振がどのように発生するかのメカニズムやどのように防いでいるのかの手法を解説し、発振に対する理解を深めることを目的とします。

## 2. LDO の発振とその影響

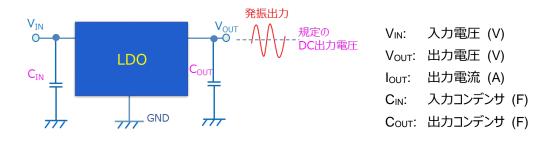

図 2.1.1 に LDO の発振のイメージ図を示します。

図 2.1.1 LDO の発振イメージ

図 2.1.1 は LDO が発振した場合の出力端子 Vout の様子をイメージした図です。

LDO は、その出力に安定した直流(DC)電圧を供給するデバイスですが、発振現象が起こった場合は図 2.1.1 のように 出力に意図しない交流(AC)電圧が発生してしまいます。 弊社の LDO は既定の使用条件では発振しないように設計されていますが、例えば出力コンデンサ Cout を推奨値より小さい値にした場合などでは発振してしまう可能性があります。 本来であれば LDO は安定した DC 電圧を出力しますが、図 2.1.1 に示すように出力に発振現象が起こった場合は、LDO の出力電圧を電源として動作している半導体デバイスなどが誤動作を起こしてしまいます。 また、AC 的な発振出力が高い周波数の場合は放出する電磁波(EMI)の影響で、周辺の電子デバイス、ひいては電子機器全体にノイズや、ノイズに起因する誤動作を誘発してしまいます。 このように、LDO の発振は、いかなる状況でも絶対に避けなければいけない現象です。

3 章では LDO やオペアンを構成する負帰還について説明し、4 章ではなぜ LDO が発振するのかを説明します。

## 3. 負帰還の原理

#### 3.1 負帰還とは? ~負帰還のメリット

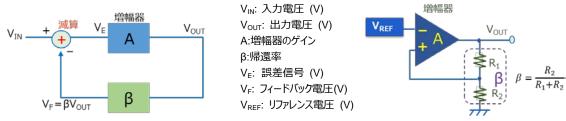

図 3.1.1 に負帰還の概念図と、負帰還の実例の 1 つである LDO の簡易回路を示します。

図 3.1.1 負帰還の概念図と LDO の簡易回路図

負帰還とは、図 3.1.1 に示すように、出力  $V_{OUT}$ を $\beta$ という帰還率で入力に戻し、それを入力  $V_{IN}$ から減算する回路システムです。この場合、増幅器に入力される信号(誤差信号) $V_E$ は下式のように元の  $V_{IN}$ から減少してしまいます。

$$V_E = V_{IN} - V_F = V_{IN} - \beta V_{OUT}$$

この場合、出力電圧  $V_{OUT}$  は負帰還を掛けない場合の A  $V_{IN}$  から下式のように減少してしまいます。

$$V_{OUT} = AV_E = A(V_{IN} - \beta V_{OUT}) \cdot \cdots (1)$$

ではなぜ、このようにせっかくの大きい出力を小さくするのでしょうか?実は負帰還には、出力が小さくなるデメリットより大きいメリットがあるのです。そのメリットを以下にまとめます。

- ・ゲインの安定化

- ・歪みが減少する

- ・周波数特性の増大

- ・外来ノイズの圧縮が可能

- ・入出力インピーダンスの変調が可能

#### また、負帰還には

- ・電圧-電圧帰還(直列並列帰還)

- •電流-電圧帰還(直列直列帰還)

- •雷圧-雷流帰環(並列並列帰環)

- •電流-電流帰還(並列直列帰還)

の四つの形式があり、それぞれ特徴があります(下表参照)。

#### 表 3.1.1 四つの負帰還形式

|  | 形式                                                        | 帰還内容                                         | 入出カインピーダンス<br>の変調                                  | 安定化される<br>特性                          |                    |

|--|-----------------------------------------------------------|----------------------------------------------|----------------------------------------------------|---------------------------------------|--------------------|

|  | 電圧 – 電圧帰還 出力電圧を<br>(直列 – 並列帰還) 電圧として入力に戻す                 | 入力インピーダンス<br>無帰還時のA <mark>β倍</mark>          | 出力電圧<br>(V <sub>OUT</sub> /V <sub>IN</sub> )       | LDO (‡                                |                    |

|  |                                                           | 出力インピーダンス<br>無帰還時の1/Aβ倍                      |                                                    | 電圧-電圧帰還                               |                    |

|  | 電流 - 電圧帰還 出力電流を<br>(直列 - 直列帰還) 電圧として入力に戻す                 | 入力インピーダンス<br>無帰還時のA <mark>β倍</mark>          | ・・・田方電流・・・<br>(I <sub>OUT</sub> /V <sub>IN</sub> ) |                                       |                    |

|  |                                                           | 出力インピーダンス<br>無帰還時のA <mark>β倍</mark>          |                                                    | (1 <sub>OUT</sub> ) v <sub>IN</sub> ) |                    |

|  | 電圧 - 電流帰還 <b>出力電圧</b> を<br>(並列 - 並列帰還) <b>電流</b> として入力に戻す | 入力インピーダンス<br>無帰還時の1/A <b>β</b> 倍 <b>出力電圧</b> | 出力電圧                                               |                                       |                    |

|  |                                                           | (並列 – 並列帰還)                                  | 出力インピーダンス<br>無帰還時の1/Aβ倍                            | $(V_{OUT}/I_{IN})$                    |                    |

|  | 電流 - 電流帰還<br>(並列 - 直列帰還) 出力電流を<br>電流として入力に戻す              | 入力インピーダンス<br>無帰還時の1/Aβ倍                      | 出力電流                                               |                                       |                    |

|  |                                                           | (並列 – 直列帰還)                                  | 电加2000人力に戻り                                        | 出力インピーダンス<br>無帰還時の <mark>Aβ倍</mark>   | $(I_{OUT}/I_{IN})$ |

LDO は、内部のレギュレーション回路を負帰還増幅器として見たとき、入力電圧となる基準電圧(VREF)から安定化された出力電圧を生成する増幅システムであり、電圧-電圧帰還が最適な形式となります。この電圧-電圧帰還のメリットの1つは、LDO レギュレーション回路の出力インピーダンスを無帰還時に対して1/Aβに低下できるため、負荷変動に対して安定した出力電圧を保つシステムが構築できることです。さらに、入力インピーダンスが無帰還時のAβ倍となるため、基準電圧(VREF)を生成する内部基準電圧回路はその負荷となるレギュレーション回路の入力部である差動増幅器に対して高い電流駆動能力を必要とせず、消費電流を低く設計することができます。このように、LDO については電圧-電圧帰還が最適な負帰還方式となります。

次章より、電圧-電圧帰還に基づいた発振の原理を説明していきます。

#### 3.2 負帰還のクローズドループゲインとループゲイン

以下より負帰還の基礎概念を説明します。

3.1の(1) 式を変形していきます。

$$V_{OUT} = A(V_{IN} - \beta V_{OUT})$$

$$= AV_{IN} - A\beta V_{OUT}$$

$$V_{OUT} + A\beta V_{OUT} = AV_{IN}$$

$$(1 + A\beta)V_{OUT} = AV_{IN}$$

これより、負帰還をかけた場合のシステムとしてのゲイン:クローズドループゲイン A<sub>CL</sub> = V<sub>OUT</sub> /V<sub>IN</sub> は下式となります。 この式の中の"AB"というファクターはループゲインと呼ばれ、発振の解析では非常に重要です。

$$A_{CL} = \frac{V_{OUT}}{V_{IN}} = \frac{A}{1 + A\beta} = \frac{1}{\frac{1}{A} + \beta}$$

ここで図 3.1.1 に示している増幅器のゲイン A が大きいと仮定すると、負帰還を掛けた場合の、すなわちクローズドループゲイン Aci は下式のようになります。

$$A_{CL} = \frac{1}{\frac{1}{A} + \beta} \cong \frac{1}{\beta}$$

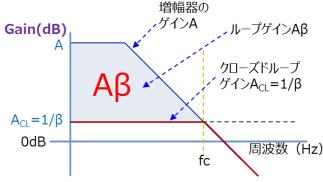

この式は、増幅器のゲイン A を大きくすれば、クローズドループゲイン A<sub>CL</sub> は、内部の増幅器とは無関係に帰還率βの要素だけで決まることを意味しています。図 3.1.1 の場合、帰還率βは受動素子である抵抗の比のみで決まり、クローズドループゲイン A<sub>CL</sub> もその抵抗比のみで決まります。この場合、増幅器のゲイン A の変動が影響しなくなるので、ゲインの安定化が可能となります。しかし、負帰還システム内の増幅器のゲイン A は通常周波数特性を持っており、例えばそれが 1 次特性の場合は図 3.1.2 のような周波数特性になります(図中の 1/βは負帰還を掛けた場合のクローズドループゲイン A<sub>CL</sub>)。この場合、上記の安定したクローズドループゲイン A<sub>CL</sub>は、図 3.1.2 に示すように増幅器のゲイン A がその周波数特性に従って小さくなるため、その安定度も周波数の増加とともに悪化します。そして、図中の周波数 fc では、クローズドループゲイン A<sub>CL</sub> は増幅器のゲインの周波数特性と一致します。

図 3.1.2 負帰還システム内の増幅器のゲイン A とクローズドループゲイン Ac の関係

図 3.1.2 から分かるようにループゲイン A $\beta$ は増幅器のゲイン A $\beta$ からクローズドループゲイン A $\beta$ し引いた領域の面積となります(増幅器のゲイン A $\beta$ 0 とクローズドループゲイン 1 $\beta$ 0 囲まれた領域)。

## 4. LDO (負帰還システム) が発振するメカニズム

#### 4.1 LDO の発振メカニズム

なぜ LDO などの負帰還システムは発振するのでしょうか? 下に再度一般的なクローズドループゲインの式を書きます。

$$A_{CL} = \frac{A}{1 + A\beta} \cong \frac{1}{\beta}$$

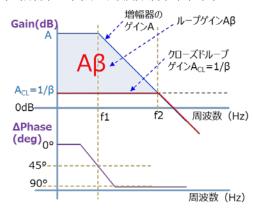

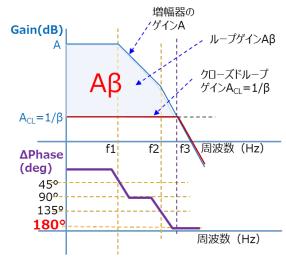

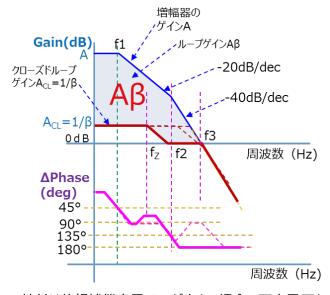

この式の分母でループゲイン  $A\beta$ が" -1"になった場合、分母はゼロになります。この時、クローズドループゲイン  $A_{CL}$  は無限大になることが分かります。クローズドループゲイン  $A_{CL}$  が無限大ということは入力がなくても出力が出てしまうことを意味しており、これがいわゆる発振状態ということになります。では、このようにループゲイン  $A\beta$ が" -1"になることはあるのでしょうか? 図 3.1.2 では負帰還システム内の増幅器がループゲイン  $A\beta$  OdB(1 倍)の周波数領域で 1 次特性を持っていると仮定していました。その場合の位相特性も含んだ周波数特性図を図 4.1.1 に示します。

図 4.1.1 1 次特性の増幅器を持つ負帰環システムの周波数特性

図 4.1.1 のような 1 次特性の増幅器を持つ負帰還システムの場合、ループゲイン A $\beta$ の位相は、一般に極と呼ばれるゲインが 3dB 落ちる周波数 f1 で 45°回り、最終的に 90°まで回ります。また、極 f1 以上の周波数ではループゲイン A $\beta$ は -20dB/dec の下降率で下降します。さらにループゲイン A $\beta$ は周波数 f2 で 0dB(=1 倍)になります。このように、増幅器が 1 次特性の場合はループゲイン A $\beta$ が 0dB(1 倍)になってもその位相が 90°までしか回らないため、発振には至りません(ループゲイン A $\beta$ が反転しません)。これに対して増幅器がループゲイン A $\beta$ > 0dB(1 倍)の周波数領域で 2 次特性を持つ場合は下の図 4.1.2 のようになります

図 4.1.2 2 次特性の増幅器を持つ負帰還システムの周波数特性

図 4.1.2 から分かるように、ループゲイン A $\beta$ > OdB(1 倍)の周波数領域で増幅器が 2 次特性を示す場合は、ループゲイン A $\beta$ の位相がその周波数領域で最終的に 180°回る、つまり反転してしまう可能性があります。この反転は A $\beta$ に" - 1"を乗ずることと等価で、周波数:f3 でループゲイン A $\beta$ は OdB、つまり 1 になります。このように、ループゲイン A $\beta$ > OdB (1 倍)の周波数領域で増幅器が 2 次(以上の)特性を持つ場合は、前述した A $\beta$ = - 1 という状況が生じてしまいます。この場合、下式のようにクローズドループゲイン A $_{CL}$ が無限大になってしまい、この負帰還システムは発振状態になってしまいます。

$$A_{CL} = \frac{A}{1 + A\beta} = \frac{A}{1 - 1} = \infty$$

また図 4.1.2 に示した第2の極: f2 より高い周波数における増幅器のゲインは-40dB/decで下降します。

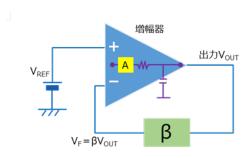

上記のように、ループゲイン Aβの位相は 1 つの極で 45°位相が回り、最終的には 90°まで回りますが、この極は回路内の抵抗成分と容量成分が存在するノードで必ず発生します。負帰還システム内部の増幅器がループゲイン Aβ> 0dB(1倍)の周波数領域で 1 次特性を示す場合、図 4.1.3 のように増幅度を持つ増幅器が 1 段構成になっているのと等価です。発振の観点では増幅器が 1 次特性(1 段構成)で、極が 1 つであることが望ましいのですが、例えば LDO の場合は良好な DC 特性、AC 特性を実現するために、前述のとおり、LDO 内部の増幅器のゲインを高くし、また周波数特性を伸ばさなければいけません。この場合、図 4.1.4 のように増幅器の構成を 2 段(以上の)構成にし、かつ消費電流の増加などの対策を行う必要があります。ループゲイン Aβ> 0dB(1 倍)の周波数領域で増幅器を 2 段構成にした場合は少なくとも極が 2 つ発生しますので、負帰還システムは図 4.1.2 のような周波数特性にならざるを得ず、発振の危険性が生じます。この状況では、何らかの方法で発振を回避する必要があります。5.より、発振を回避する方法、つまり位相補償について解説します。

図 4.1.3 1 次特性の LDO

図 4.1.4 2 次特件の LDO

#### 4.2 位相余裕とゲイン余裕

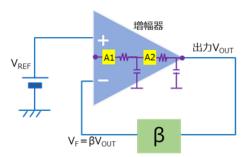

以上より、負帰還システムは、ループゲイン Aβ> 0dB(1 倍)の周波数領域で増幅器が 2 次(以上の)特性を持つ場合、ループゲイン Aβが - 1 になる状況が発生することで発振してしまうことが分かりました。また、前述のとおり、増幅器が 1 次特性の場合は、ループゲイン Aβが 0dB(1 倍)になってもその位相が 90°までしか回らないため、発振には至りません。このような発振に対するシステムの安定度を判断する基準に位相余裕とゲイン余裕があります。 位相余裕、ゲイン余裕は下記のように定義されます。

・位相余裕: ループゲイン Aβが OdB となる周波数で、その位相が 180°回るまで何°の余裕があるか

・ゲイン余裕:ループゲイン ABの位相が 180°回った周波数で、そのゲインが OdB に対してどれだけ低いか

発振しない安定したシステムと判断できるのは、一般的に

・位相余裕: 60° (以上) ・ゲイン余裕: 6dB (以上)

が望ましいと言われています。

図 4.2 に位相余裕、ゲイン余裕の概念図を示します。

図 4.2 位相余裕とゲイン余裕の概念図

## 5. LDO の位相補償 ~発振させないために

#### 5.1 LDO 内部の位相補償の方法

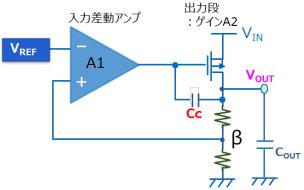

#### 5.1.1 ミラー補償

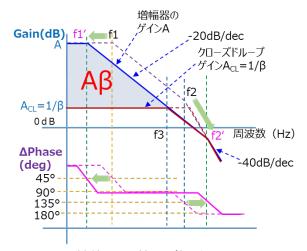

例えば4.での議論のように、負帰環システムが発振してLDOの動作が破綻してしまう場合、LDOだけでなく、LDOの 出力電圧を電源として動作している電子デバイス、ひいては LDO を搭載している電子機器自体の動作が破綻してしまい ます。そのため、如何なる状況でも LDO を発振させてはいけません。しかし、4.で述べたように LDO の特性を良好に保つた めには LDO 内の増幅器の段数を増やす必要があり、この場合は発振の危険性が生じてしまいます。そこで、LDO を発振 させないための施策、つまり位相補償について解説します。位相補償とは、図 4.1.2 に示した発振の可能性が高い状況 を、回路を工夫することによって発振しない状況にする、つまりループゲイン Aβが OdB の時にその位相が 180°回らない (反転しない) ようにすることを意味します。この位相補償のもっともポピュラーな方法にミラー補償という回路技術がありま す。これは、図 5.1.2 に示すように 2 段構成の LDO の場合、LDO 内の出力段(反転アンプ)の入出力間に位相補償 コンデンサ  $C_C$ を接続することで、入力差動アンプの出力に  $A2 \cdot C_C$ (位相補償コンデンサ  $C_C$ を出力段のゲイン倍した容量 値)という大きい容量値をつけて、増幅器の周波数特性をあえて悪化させる方法です。この方法によって、図 5.1.3 のよう に、もともとループゲイン ABが OdB(1 倍)以上の周波数領域に極が2つ存在する(f1、f2)状態を極が1つしか存 在しない状態(f1'のみ)にすることが出来ます。この状態は増幅器が 1 次特性と等価であるため、ループゲイン Aβが OdB(1 倍)になる周波数 f3 で ABの位相が 90°までしか回らず発振を回避することができます。また、図 5.1.3 から分 かるように、もともとの極である f1、f2 が f1'と f2'のように互いに周波数的に離れた位置に移動します。これを極分離 (Pole Splitting) と言い、位相が 180°回る周波数をより高い周波数に持っていくことで、安定度をより高めることに寄 与しています。

図 5.1.2 一般的なミラー補償の方法

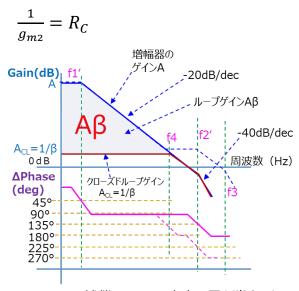

図 5.1.3 ミラー補償による効果 (極分離: Pole Splitting)

また図 5.1.3 から言えることは、ループゲイン Aβが OdB になるまでにゲインの下降率が – 40dB/dec になる領域が存在する場合は発振の可能性が高く、 – 20dB/dec の領域のみの場合は発振しないということです。この考え方は後述する可変出力電圧タイプ LDO の CFB による位相補償などでも必要な考え方になります。ここで注意が必要です。上記のミラー補償は極分離によって発振を回避できますが、設計によっては新たに不安定な零(RHP Zero: Right Half Plane Zero: S 平面の右半面に発生する負帰還システムを不安定にする零)が発生し、その零が低い周波数領域に存在する場合は発振の可能性が生じます。これを回避する方法は以下の 5.1.2 で説明します。

#### 5.1.2 不安定な零(RHP Zero)とそれによる発振を回避する Lag-Lead 形式の位相補償

ミラー補償は負帰還システムを安定化する有効な手段ですが、前述のように設計によっては不安定な零(RHP Zero)が低い周波数領域に発生し、それによって負帰還システムが発振する可能性が生じます。例えば図 5.1.4 に示すように不安定な零が周波数 fz に発生した場合、ループゲイン Aβが fz より高い周波数で低下せず、かつ位相が 180°に向けて回り続けるという現象が起きます。この状況では、ミラー補償による極分離によって位相補償をしても、ループゲイン Aβが OdBになる周波数 f4 ですでに位相が反転してしまっており、発振してしまいます。

図 5.1.4 ミラー補償によって不安定な零(RHP Zero)が発生した場合の周波数特性

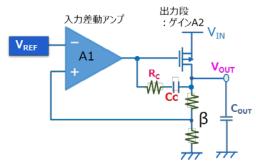

そこで、この問題を解決するために、図 5.1.5 に示すように、ミラー補償コンデンサ  $C_C$ と直列に抵抗  $R_C$ を接続する位相補償の方法があります。このコンデンサと抵抗の直列接続による位相補償を Lag-Lead 補償といい、この形式にすることで前述の不安定な零を事実上無効化することが出来ます。

図 5.1.5 Lag-Lead 補償を持つ LDO

理論計算によると、この直列抵抗 R<sub>C</sub>によって、零が下式のようになります(g<sub>m2</sub>は出力段 PMOS の相互コンダクタンスとし

ます)。

$$f_Z = \frac{1}{2\pi C_C \times \left(\frac{1}{g_{m2}} - R_C\right)}$$

上記の零で、下のように直列抵抗  $R_C$ の値を設定すれば、ミラー補償の場合に発生する RHP Zero(Right Half Plane Zero)が無限大の周波数となり(実質的に消去)、その結果、図 5.1.6 のように LDO が 1 次特性と等価の状態になる ことでシステムを安定化することができます。

図 5.1.6 Lag-Lead 補償によって不安定な零を消去した LDO の周波数特性

#### 5.1.3 LDO 外部に大きい出力コンデンサがある場合の位相補償 ~零の追加

前述のとおり、ミラー補償や Lag-Lead 補償という位相補償の方法によって LDO 内部では発振耐性を大きく改善することが出来ます。しかし、LDO に関しては負荷過渡応答など、出力電圧の安定化のために大きな出力コンデンサ Cout が必要です。この場合、ミラー補償によって Aβが OdB になるまでの周波数領域に極を 1 つにしたとしても、大きな出力コンデンサ Cout を付けることによって、図 5.1.7 に示すように極が低い周波数(f0)に移動し 2 次特性になってしまいます。この状態では再び発振の可能性が高まります。

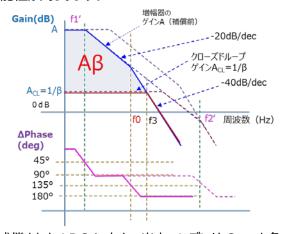

図 5.1.7 ミラー補償された LDO に大きい出力コンデンサ Cout を負荷した場合のループゲイン Aβの位相変化

この状態ではループゲイン Aβが OdB になる周波数 f3 でその位相が 180°回り、発振してしまいます。この発振を回避するために何らかの位相補償によって再びループゲイン Aβが OdB になるまでの領域に極を 1 つだけにする、またはループゲイン Aβの下降率を - 20dB/dec にすることが必要です。そこで一般的に行われる、ループゲイン Aβを - 20dB/dec にする方法によって補償された LDO の周波数/位相特性を図 5.1.8 に示します。

図 5.1.8 大きい出力コンデンサ Cout による極 f0 の発生に対する位相補償結果

図 5.1.8 に示されるように、零が  $fZ(\mathcal{N}-\mathcal{I})$ の下降率は 90°に位相シフトをもたらし、それで-40dB/dec から-20dB/dec に変わる)で追加されます。この結果、 $\mathcal{N}-\mathcal{I}$  の付か 0dB になるまでに位相が 180°回ることが回避され、その結果、発振を防ぐことが出来ます。このように零: $f_Z$  を追加する方法は前述の図 5.1.5 に示した Lag-Lead 形式によって実現することが可能です。

Lag-Lead 形式としたときに発生する零の式を再度記します。

$$f_Z = \frac{1}{2\pi C_C \times \left(\frac{1}{g_{m2}} - R_C\right)}$$

この零の式で

$$\frac{1}{g_{m2}} < R_C$$

と設定すれば、5.1.2 でお話ししたミラー補償で発生する不安定な零(RHP Zero:Right Half Plane Zero)を安定な零(LHP Zero:Left Half Plane Zero)に変化させつつ、零: $f_Z$  を追加することができます。この場合、図 5.1.7 に示した発振の可能性が高い状態から図 5.1.8 の安定した状態にすることができます。以上が不安定な負帰還システムを安定化するために LDO 内部で行われる位相補償(ミラー補償、Lag-Lead 補償)です。以下より、LDO の外部で行う位相補償の説明をします。

#### 5.2 LDO 外部の位相補償の方法

#### 5.2.1 出力コンデンサの直列等価抵抗: ESR(R<sub>FSR</sub>)を利用して零: fz を追加する方法

図 5.2.1 に出力コンデンサ Cour の等価直列抵抗 ESR がある場合の LDO の簡易回路図を示します。

図 5.2.1 出力コンデンサ Cout に等価直列抵抗: ESR (Resp.) がある場合の LDO 簡易回路図

前述のとおり、大きな出力コンデンサ C<sub>OUT</sub> を接続した場合は何らかの方法で零を追加し、LDO を発振しないよう位相補償する必要があります。 5.1 では LDO の内部におけるミラー補償、Lag-Lead 補償を説明しましたが、図 5.2.1 に示すように、出力コンデンサ C<sub>OUT</sub> 自身が持っている等価直列抵抗を:ESR(R<sub>ESR</sub>)利用して零を追加する方法があります。

この場合、等価直列抵抗: ESR (R<sub>ESR</sub>) によって下記の周波数に零が発生します。

$$f_Z = \frac{1}{2\pi C_{OUT} \times R_{ESR}}$$

出力コンデンサ  $C_{OUT}$  の等価直列抵抗 ESR( $R_{ESR}$ )の大きさを選択することによってループゲイン  $A\beta>0$ dB(1 倍)の周波数領域の所望の周波数に零(fz)を追加することができます。この零の追加により、図 5.1.7 に示した発振の可能性が高い状態から図 5.1.8 の安定した状態にすることが可能です。しかしここで注意が必要です。出力コンデンサ  $C_{OUT}$  の等価直列抵抗 ESR( $R_{ESR}$ )を大きくすると、負荷過渡応答などの AC 特性が悪化する可能性が生じます。したがって、出力コンデンサ  $C_{OUT}$  の等価直列抵抗 ESR( $R_{ESR}$ )を利用した零の追加を行う場合は AC 特性とのバランスを慎重にとる必要があります。

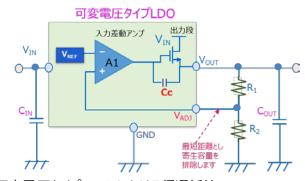

# 6. 可変電圧タイプ LDO における外付け位相補償容量: CFB の効果

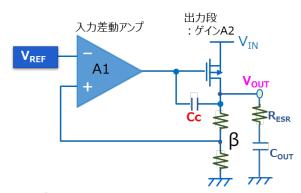

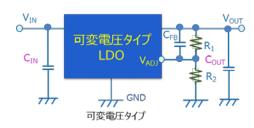

LDO には出力電圧 Voutを外付け抵抗で決定する可変電圧タイプがあります(図 6.1.1)

図 6.1.1 可変電圧タイプ LDO

弊社の可変電圧タイプ LDO は、図 6.1.1 の外付け抵抗  $R_1$ と並列に接続されている位相補償容量  $C_{FB}$  がなくても安定動作するように設計されていますが、発振予防のため、または負荷過渡特性改善のために位相補償容量  $C_{FB}$  を接続しても構いません。例えば、プリント基板の配線容量によって可変電圧タイプ LDO のフィードバック端子(図 6.1.1 における  $A_{ADJ}$ )に寄生容量が発生してしまった場合の発振対策に位相補償容量  $C_{FB}$  は効果的です。そこで、一般的な位相補償容量  $C_{FB}$  の位相補償効果の説明をしておきます。

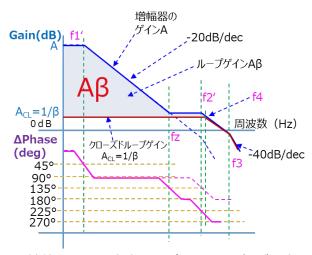

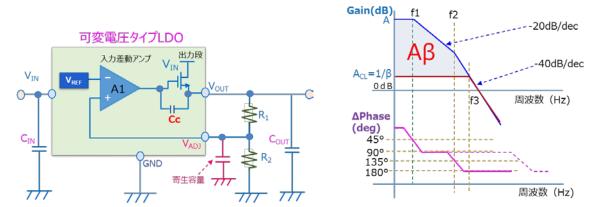

例えば図 6.1.2 に示すように、可変電圧タイプ LDO のフィードバック端子  $V_{ADJ}$  に寄生容量がついてしまった場合はループ ゲイン  $A\beta>0$  dB(1 倍)の周波数領域で 2 次特性となってしまう可能性があります。

図 6.1.2 可変電圧タイプ LDO のフィードバック端子 AADI に寄生容量がついてしまった場合の LDO 周波数特性

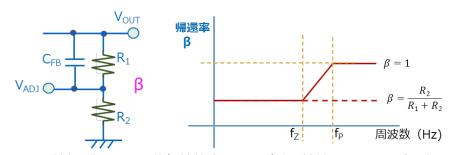

図 6.1.2 ではループゲイン Aβが OdB(1 倍)になる周波数 f3 でその位相が 180°回っていますので LDO は発振して しまいます。そこで図 6.1.1 のように外付け抵抗  $R_1$  に位相補償容量  $C_{FB}$  を並列接続すると、帰還率βは、元々、抵抗だけで構成されており、周波数に対して一定ですが、 $C_{FB}$  の効果により図 6.1.3 のように周波数特性を持つようになります。

図 6.1.3 外付け抵抗 R1 に位相補償容量 CFB が並列接続されている場合の帰還率β

位相補償容量  $C_{FB}$  がない場合の帰還率 $\beta$ は周波数に対して一定の  $R_2/(R_1 + R_2)$  ですが、位相補償容量  $C_{FB}$  がある場合は、図 6.1.3 のように周波数  $f_Z$ 、 $f_P$ で帰還率 $g_Z$ が変化します。図中  $g_Z$ 、 $g_Z$ 、 $g_Z$  は下式で決まります。

$$f_Z = \frac{1}{2\pi C_{FB} \times R_1}$$

$$f_P = \frac{1}{2\pi C_{FB} \times (R_1//R_2)}$$

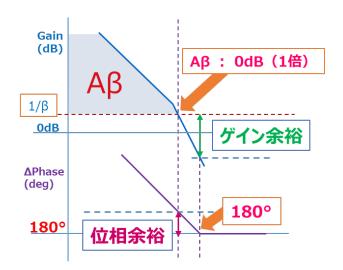

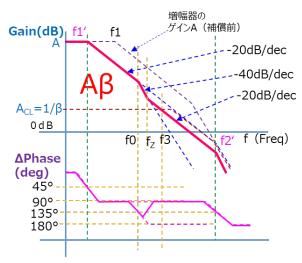

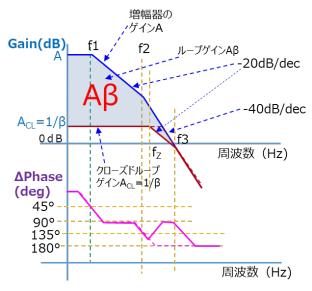

帰還率 $\beta$ が図 6.1.3 のような周波数特性を持つ場合、帰還率の逆数  $1/\beta$ であるDローズドループゲイン  $A_{CL}$ 、さらにループゲイン  $A\beta$ とその位相特性は図 6.1.4 のようになります。

図 6.1.4 位相補償容量 CFB がある場合のクローズドループゲイン ACI の周波数特性、ループゲイン ABとその位相特性

図 6.1.4 を見ると、LDO 内部の増幅器のゲイン A は 2 つの極:f1、f2 を持っています。そして、クローズドループゲイン  $A_{CL}=1/\beta$ も周波数  $f_Z$  を極としてその周波数からゲインが -20 dB/dec で下降しています。この場合、LDO 内部増幅器 のゲイン A とクローズドループゲイン  $A_{CL}$  の特性に囲まれた領域(A と  $A_{CL}=1/\beta$ の差分)であるループゲイン  $A_{CL}$  の付している周波数 f3 までに極が f4 つの付け、f4 の存在しますが、クローズドループゲイン f4 の極 f4 のを f4 の下降率が以下に示すように -40 dB/dec から -20 dB/dec に緩和されることが分かります。

クローズドループゲイン  $A_{CL}=1/\beta$ の極  $f_Z$ より高い周波数におけるループゲイン  $A\beta$ の下降率  $: ループゲイン Aβの下降率 = 増幅器のゲイン A の下降率 - クローズドループゲイン<math>A_{CL}$ の下降率 = (-40dB/dec) - (-20dB/dec) = -20dB/dec

前述のようにループゲイン A $\beta$ の位相が 180°回る条件でループゲイン A $\beta$ が – 40dB/dec の下降率を持つことを思い出す と、-20dB/dec の領域ではループゲイン A $\beta$ の位相は 90°までしか回らないことになります。この場合、ループゲイン A $\beta$ の 位相特性は図 6.1.4 に示すように、周波数  $f_Z \sim f_3$ (ループゲイン A $\beta$  = 0dB となる周波数)間で 90°に向かって回復 し、180°まで回らないことになります。言い換えると、周波数  $f_Z \sim f_3$  間でループゲイン A $\beta$ は 1 次特性になっていると等価と

言えます。このように、位相補償容量 C<sub>FB</sub> は、帰還率βに周波数特性を持たせることによって位相変動を抑制し、ループゲイン Aβの位相が反転しないようにし、発振を回避しています。

しかし、外付け位相補償容量 C<sub>FB</sub>を必要以上に大きくすると図 6.1.5 のようにクローズドループゲインの周波数特性が悪化しますので、注意が必要です。また、第 2 の極 f2 より低い周波数に零を設定しますと、同じく図 6.1.5 に示すように、零によって位相を戻す効果が低い周波数で消滅してしまい、ループゲイン Aβの位相が 180°回ってしまいます。図 6.1.5 の場合は LDO 内の増幅器のゲイン特性が持つ極 f2 より低い周波数ですでに外付け位相補償容量 C<sub>FB</sub>の効果がなくなり、クローズドループゲイン Aβが OdB になっています。この状況では周波数 f2 より高い周波数でループゲイン Aβの下降率が - 40dB/dec となってしまうため、ループゲイン Aβが OdB 以上の周波数領域でその位相が 180°回り、発振してしまいます。したがって、外付け位相補償容量 C<sub>FB</sub>の容量値は発振耐性と LDO の AC 特性のバランスを考慮して必要最低限に決定する必要があります。

図 6.1.5 外付け位相補償容量 CFB が大きい場合の可変電圧タイプ LDO 周波数特性

以上のように、発振耐性の向上に外付け位相補償容量  $C_{FB}$ は効果的ですが、図 6.1.6 に示すように、基本的にはプリント基板のパターンレイアウトで帰還抵抗  $R_1$ 、 $R_2$ の接続点からフィードバック端子  $A_{ADJ}$ までの距離を短くするなど、寄生容量をできるだけ排除することをお勧め致します。

図 6.1.6 可変電圧タイプ LDO における帰還抵抗 R1、R2~フィードバック端子 AADJまでの距離

# **LDO の発振原理と発振耐性向上について Application Note**

### 7. まとめ

負帰還を持つシステムは、そのループゲイン Aβが OdB(以上)である周波数で位相が 180°回った場合に発振してしまいます。ループゲイン Aβが 2 次特性(以上)であればその位相が 180°回りますので、位相補償による発振の回避が必須となります。 LDO はその内部回路でミラー補償、零を追加することによる位相補償で発振を回避しています。 また、出カコンデンサ Cout の等価直列抵抗 ESR による零の追加も効果的です。 さらに、外付け抵抗による可変電圧タイプの LDO は、出力端子 Vout に接続されている側の帰還抵抗に位相補償容量 CFB を並列接続することでより発振耐性を強化することが出来ます。 また、パターンレイアウトで帰還抵抗の接続点からフィードバック端子 VADJ までの距離を短くするなど、寄生容量をできるだけ小さくすることも発振耐性を強化できます。

弊社 LDO は上記の位相補償の手法やその他の回路技術で発振を回避しながら LDO の AC 特性を改善する回路を用いることによって安全性と性能の両立を実現しています。

#### 弊社の代表的な LDO 製品

300mA LDO(固定タイプ) :TCR3DMのデータシートダウンロードはこちらから → Click Here

500mA LDO(固定タイプ) : TCR5BMのデータシートダウンロードはこちらから → Click Here

800mA LDO(固定タイプ): TCR8BMのデータシートダウンロードはこちらから → Click Here

#### CFB が追加可能な可変電圧 LDO 製品

1.3A LDO (可変タイプ): TCR13AGADJ のデータシートダウンロードはこちらから → Click Here

1.5A LDO (固定・可変タイプ): TCR15AG のデータシートダウンロードはこちらから → Click Here

この他 LDO の使用方法については、"ロードロップアウト(LDO)レギュレーターIC アプリケーションノート"をご覧ください。 ロードロップアウト(LDO)レギュレーターIC アプリケーションノートはこちらから Click Here

19

# 8. 関連リンク

- ■製品のラインアップ(カタログ)

- ■製品のラインアップ(詳細)

- ■製品のラインアップ(パラメトリックサーチ)

- ■オンラインディストリビュータご購入、在庫検索

- ■ロードロップアウト レギュレーター ICの FAQ

- ■アプリケーションノート

Click

Click

Buy

Online

Click

20

# LDO の発振原理と発振耐性向上について Application Note

#### 9. 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。 本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- ◆ 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾を得て本 資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器(ヘルスケア除く)、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォームからお問い合わせください。

- ◆ 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- ◆ 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、あるいは その他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国貿易法」、「米国輸 出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。

# 東芝デバイス&ストレージ株式会社

https://toshiba.semicon-storage.com/jp/