# <u>アイソレーションアンプ</u> TLP7820/7920/7830/7930 アプリケーションノート

### 概要

本資料では、アイソレーションアンプ TLP7820/7920、 デルタシグマ・モジュレーター TLP7830/7930 の機能 概要および応用設計事項を説明致します。

### 目次

| はじめに                                      | 2  |

|-------------------------------------------|----|

| 1.光結合型アイソレーションアンプ TLP7820/7920 製品機能概要     |    |

| 2.光結合型デルタ-シグマ・モジュレーター TLP7830/7930 製品機能概要 | 4  |

| 3. アイソレーションアンプの応用設計(電流検出用途)               | 5  |

| 3-1. 1 次・2 次側 電源ライン設計                     | 5  |

| 3-2. 1 次側入力ライン設計                          | 5  |

| 3-3. 電流検出抵抗(シャント抵抗)設計                     | 6  |

| 3-4. 出力ライン設計                              | 7  |

| 3-5. 他の設計上注意事項                            | 10 |

| 4. アイソレーションアンプの応用設計(電圧検出用途)               | 11 |

| 4-1. 電圧検出抵抗設計                             | 11 |

| 5. データシート掲載項目以外の特性データ                     | 12 |

| 5-1. アイソレーションアンプ TLP7820/7920 の出力雑音特性     | 12 |

| 5-2. アイソレーションアンプ TLP7820/7920 の SN 特性     | 13 |

| 5-3. アイソレーションアンプ TLP7820/7920 の PSRR 特性   | 14 |

| 6. TLP7820/7920/7830/7930 の特長             | 15 |

| 6-1. 1 次側消費電流削減設計                         | 15 |

| 6-2. 新規 SO8L 薄型パッケージの採用                   |    |

| 7.アプリケーション                                |    |

| 製品取り扱い上のお願い                               | 18 |

### はじめに

FA 市場での AC サーボや汎用インバーター、太陽光・風力発電市場のパワーコンディショナーのインバーターなどでは、高精度・高効率動作/制御のための電流/電圧検出が必須であり、それらの特性精度/安定性・入出力絶縁性能が設計のポイントとなります。

#### 東芝の

アイソレーションアンプ (アナログ出力) : TLP7820/7920デルタシグマ・モジュレーター (デジタル出力) : TLP7830/7930

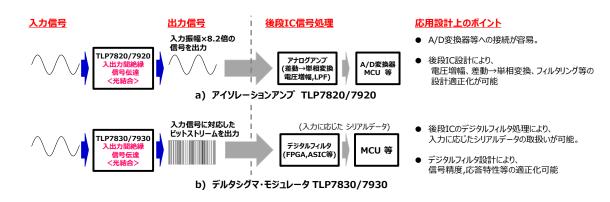

は、デルターシグマ A/D 変換器/入出力間 絶縁機能(光結合型)を備え、高精度 入出力ゲイン・リニアリティー、高絶縁性能を実現、良好な電流/電圧検出が可能です。 また、上記 2 種の出力形態ラインアップより、アプリケーションのシステム設計(後段 IC 信号処理など)に応じた製品選択が可能です。

図 1. TLP7820/7920/7830/7930 を用いた信号処理例

さらに、パッケージラインアップとして SO8L,DIP8 2 種類のパッケージをラインアップしており、設計スペースなどに応じた製品選択が可能です。

| お面空間距離 | 8mm | 7 or 8mm | 1 o

表 1. TLP7820/7920/7830/7930 出力形式・パッケージ対応表

#### TLP7820/7920ゲイン精度ランク指定

| 分類名称           | 製品表示<br>ランク記号 | (最小) | ゲイン<br>(標準) | (最大) | 単位  |

|----------------|---------------|------|-------------|------|-----|

| 無 (±3 %)       | 無印, A, B      | 7.95 | 8.2         | 8.44 | V/V |

| Aランク品 (±1 %)   | A, B          | 8.12 | 8.2         | 8.28 |     |

| Bランク品 (±0.5 %) | В             | 8.16 | 8.2         | 8.24 |     |

本資料では、アイソレーションアンプ TLP7820/7920、 デルタシグマ・モジュレーター TLP7830/7930 の機能概要および応用設計事項を説明致します。

# 1.光結合型アイソレーションアンプ TLP7820/7920 製品機能概要

TLP7820/7920 は、入力:アナログ信号、出力:アナログ信号の 光結合型アイソレーションアンプです。 本項では、TLP7820/7920の製品機能概要 について述べます。

本製品は、1-2 次間信号伝送に LED-フォトダイオード光伝送を適用することにより絶縁機能を備え、かつその光伝送信号をデジタルコードとすることで、高精度信号伝送を実現しております。

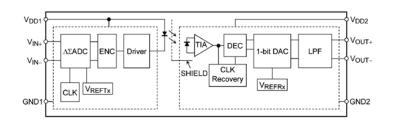

図 2 に TLP7820/7920 の機能ブロック図を示します。入力アナログ信号は、 1 次側デルタ-シグマ A/D 変換器でエンコーダー回路により 符号化デジタルコードデータへ変換し、LED で出力側へ光伝送します。 2 次側回路では、前記信号をフォトダイオードで受信、トランスインピーダンスアンプ、デコーダー回路により復調し、DA 変換回路,LPF を介して最終的なアナログ出力信号が得られます。

図 3 に TLP7820/7920 の入出力特性イメージ図を示します。 $V_{IN+}$ - $V_{IN-}$ 端子間の差動電圧入力に対して、8.2 倍 (typ.)の出力を  $V_{OUT+}$ 、 $V_{OUT-}$ 端子間差動電圧で得ることができます。

図 2. TLP7820/7920 機能ブロック図

図 3. TLP7820/7920 入出力特性

詳細は製品ページ(TLP7820 TLP7920) および アイソレーションアンプ用語説明資料 を参照ください。

# 2. 光結合型デルタ-シグマ・モジュレーター TLP7830/7930 製品機能概要

TLP7830/7930 は、入力:アナログ信号、出力:デジタル信号の 光結合型デルタ-シグマ・モジュレーターです。本項では、TLP7830/7930 の製品機能概要 について述べます。

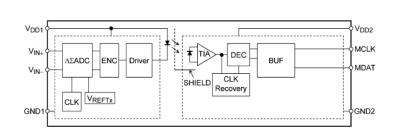

図 4 に TLP7830/7930 の機能ブロック図を示します。TLP7830/7930 は、TLP7820/7920 に対して DA 変換器以降の処理を省き、デコーダー復調後のビットストリーム信号およびクロック信号を出力します。本出力を用い、後段 IC でデジタルフィルター処理を行うことで、入力アナログ情報に対応したシリアルデータを得ることができます。

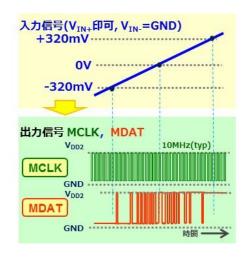

図 5 に TLP7830/7930 の入出力特性イメージ図を示します。本製品では MCLK 端子からは 10MHz (typ.)の クロック信号、MDAT 端子からは V<sub>IN+</sub>-V<sub>IN-</sub>端子間差動入力電圧に応じたクロック周期のビットストリームデータが出力されます。

図 4. TLP7830/7930 機能ブロック図

図 5. TLP7830/7930 入出力特性

詳細は製品ページ(TLP7830 TLP7930) および アイソレーションアンプ用語説明資料 を参照ください。

# 3. アイソレーションアンプの応用設計(電流検出用途)

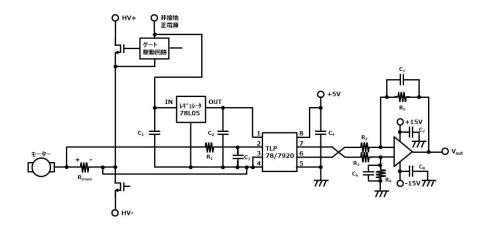

本項では、図 6 のモーター電流検出の応用回路を代表に、アイソレーションアンプの電流検出応用設計について述べます。

### 3-1. 1次・2次側 電源ライン設計

- a)  $V_{DD1}$ , $V_{DD2}$ 電源端子には、できるだけ直近(10mm 以内推奨)に  $0.1\mu$ F 以上のバイパスコンデンサーを接続してください(図 6  $C_{2,4}$ )。 このバイパスコンデンサーは、製品内部回路の高速安定動作に必要です。

- b) 本製品の1次側電源印加にあたり、パワートランジスターゲート駆動回路用電源などの高電圧と共通化される際は、レギュレーター・DC-DCコンバーター・ツェナーダイオードなどで本製品仕様範囲へ降圧し、使用をお願いします。

#### 3-2. 1 次側入力ライン設計

- a) A/D 変換器入力部には、クロック動作のスイッチトキャパシターを採用しております。 動作追従・特性精度確保のため、入力端子に 0.01μF のバイパスコンデンサー付加を推奨します (図 6 C₃)。

- b) A/D 変換器のエイリアス雑音による影響を防ぐため、入力端子部にアンチエイリアスローパスフィルターの形成を 推奨します。これは、3-2a)項の入力端子バイパスコンデンサーに加え、直列抵抗(図 6 R<sub>1</sub>)を追加することで形成 できます。アンチエイリアスフィルターの設計値は、信号帯域幅以上かつナイキスト周波数以下となりますので、 400kHz~1MHz 程度の設計値を推奨します。

#### 設計例) アンチエイリアスフィルター定数 R<sub>1</sub>の設計値

エイリアスフィルター設計周波数 400kHz、入力端子バイパスコンデンサー  $0.01\mu F$  の場合  $R_1=1/(2\times\pi\times0.01\mu F\times400kHz)=39\Omega$

図 6. TLP7820/7920 を用いたモーター電流検出 応用回路

### 3-3. 電流検出抵抗(シャント抵抗)設計

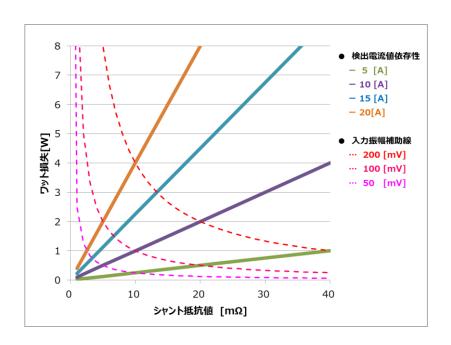

a) シャント抵抗値の設計では、ワット損失と検出精度の両者を考えた勘案した設計が必要となります。

これは、ワット損失の観点ではシャント抵抗値小ほど望ましい一方で、リニアリティー、SNR に代表される検出精度の 観点では、アイソレーションアンプの推奨入力電圧範囲(±200mV) 近傍が望ましいためです。

図 7 に、シャント抵抗値とワット損失 の関係を示します。図中実線(シャント抵抗値とワット損失の関係)と点線 (入力振幅補助線)の交差点が設計代表値となります。アイソレーションアンプの電流検出精度は入力電圧振幅 ±200mV を推奨しますので、本条件、検出電流からワット損失を満たすかご確認されることを推奨します。

図 7. シャント抵抗値とワット損失の関係

設計例) 検出電流 20A 時の入力振幅 Vin , シャント抵抗 Rshunt , ワット損失 Pshunt 設計値

- ① 検出精度(入力振幅)重視し、入力振幅 Vin=200mV とした場合

- シャント抵抗値 R<sub>shunt</sub> = 200mV/20A = 10mΩ

- ワット損失 P<sub>shunt</sub> = I<sup>2</sup>×R= (20A)<sup>2</sup>×10mΩ= 4W

- ② ワット損失重視し、P<sub>shunt</sub>=1W とした場合

- 検出電流 20A とした場合、R<sub>shunt</sub> = 1W/(20A)<sup>2</sup> = 2.5mΩ

- 入力振幅 V<sub>in</sub>= 20A×2.5mΩ = 50mV

#### 3-4. 出力ライン設計

- a) 後段 IC への接続配線は、配線カップリング・基板容量などの観点から、できる限り短い配線接続を推奨します。

- b) アナログ出力品では、後段にオペアンプを使用することにより、アイソレーションアンプの出力信号の差動→ 単相変換、振幅調整、ノイズフィルター機能追加設計が可能です。 この時、アイソレーションアンプ 出力特性 (オフセット・ゲイン・応答特性およびそれらの温度依存性)が損なわれない精度の製品をご使用ください。また、 V<sub>OUT+</sub>,V<sub>OUT-</sub>端子いずれかを単相出力で使用する際は、他方の端子処理はオープンとしてください。

- c) デジタル出力品では、後段 IC に FPGA,ASIC などを用い、SINC フィルターなどのデジタルフィルター処理を 行うことにより、ビットストリーム出力からビットコード出力への変換、高域ノイズ成分の低減が可能です。

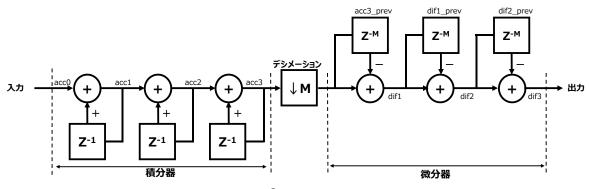

#### ●デジタルフィルター次数設計

TLP7830/7930 では、2 次デルターシグマ A/D 変換器を用いていますので、帯域外ノイズ低減の観点から、3 次デジタルフィルターを推奨します。

#### ●デシメーションレート設計

表 2 に、SINC<sup>3</sup> フィルターにおけるデシメーションレートと各設計パラメーターの関係を示します。 フィルター応答性(応答時間・フィルター帯域)と SN 特性にトレードオフを考慮した設計とする必要があります。

| デシメーション | 出力データサイズ | 応答時間 | 出力データレート | 周波数帯域 | ナイキスト周波数 | 理論SNR値 | 理論ENOB |

|---------|----------|------|----------|-------|----------|--------|--------|

| レート     | [bits]   | [µs] | [kSPS]   | [kHz] | [kHz]    | [dB]   | [bits] |

| 4       | 6        | 1.2  | 2500.0   | 655.0 | 1250.0   | 14.0   | 2.0    |

| 8       | 9        | 2.4  | 1250.0   | 327.5 | 625.0    | 30.8   | 4.8    |

| 16      | 12       | 4.8  | 625.0    | 163.8 | 312.5    | 45.7   | 7.3    |

| 32      | 15       | 9.6  | 312.5    | 81.9  | 156.3    | 59.7   | 9.6    |

| 64      | 18       | 19.2 | 156.3    | 40.9  | 78.1     | 68.2   | 11.0   |

| 128     | 21       | 38.4 | 78.1     | 20.5  | 39.1     | 71.9   | 11.7   |

| 256     | 24       | 76.8 | 39.1     | 10.2  | 19.5     | 74.9   | 12.1   |

表 2. SINC<sup>3</sup>フィルター デシメーションレートと各設計パラメーターの関係

TLP7830/7930 では、SINC<sup>3</sup> フィルター デシメーションレート 256 使用、16bit 分解能で特性保証しております。 図 8 に代表的な SINC<sup>3</sup> フィルター 構成例を、リスト 1 にプログラム例をそれぞれ示します。

図 8. SINC<sup>3</sup>フィルター構成例

#### リスト1. SINC<sup>3</sup>フィルター プログラム例

```

/* ---- Toshiba Electronic Devices & Storage Corporation ---- */

/* SINC3 Digital filter example with VerilogHDL for TLP7830/7930 */

module SINC3_VerilogHDL

input MCLK, MDAT,

/* Output of TLP7830/7930 */

input RST,

/* Filter reset signal */

/* Decimation Rate */

input [15:0] DEC,

output reg [15:0] SNCOUT, /* SINC3 filter output with 16bit */

/* SNCOUT Enable signal */

output reg ENBL

reg [24:0] acc0,acc1,acc2,acc3,acc3_prev;

reg [24:0] dif1,dif2,dif3,dif1_prev,dif2_prev;

/* Registor for Accumlation and Differentiation */

reg [15:0] mclkcnt; /* MCLK Counter */

reg decclk; /* CLK by decimation rating based

/* ----- 3 times Accumulation ----- */

always @ (MDAT)

if(MDAT==0)

acc0 <= 25'd0;

else

acc0 <= 25'd1;

always @ (negedge MCLK, posedge RST)

if (RST)

begin /* Initialization */

acc1 <= 25'd0;

acc2 <= 25'd0;

acc3 <= 25'd0;

end

else

begin /* Accumulation */

acc1 \le acc1 + acc0;

acc2 \le acc2 + acc1;

acc3 \le acc3 + acc2;

end

end

/* ----- Decimation clock gen ----- */

always @ (posedge MCLK, posedge RST)

begin

if (RST)

mclkcnt <= 16'd0;

else

begin

if ( mclkcnt == DEC - 1 )

mclkcnt <= 16'd0;

else

mclkcnt <= mclkcnt +16'b1;

end

end

always @ ( posedge MCLK, posedge RST )

begin

if (RST)

decclk <= 1'b0;

else

begin

if ( mclkcnt == DEC/2 - 1 )

decclk <= 1'b1;

else if ( mclkcnt == DEC - 1 )

decclk \le 1'b0;

end

end

```

```

/* ----- 3 times Differntiation ----- */

always @ (posedge decclk, posedge RST)

begin

if(RST)

begin /* Initialization */

acc3_prev <= 25'd0;

dif1_prev <= 25'd0;

dif2_prev <= 25'd0;

dif1 <= 25'd0;

dif2 <= 25'd0;

dif3 <= 25'd0;

end

else

begin /* Differentiation */

dif1 <= acc3 - acc3_prev;

dif2 <= dif1 - dif1_prev;

dif3 <= dif2 - dif2_prev;

acc3_prev <= acc3;

dif1_prev <= dif1;

dif2 prev <= dif2;

end

end

/* ----- Output bit number will be set to 16bits ----- */

always @ ( posedge decclk )

begin

case ( DEC )

16'd64:begin

SNCOUT \le (dif3[18:2] = 17'h10000) ? 16'hFFFF : dif3[17:2];

end

16'd128:begin

SNCOUT <= (dif3[21:5] == 17'h10000) ? 16'hFFFF : dif3[20:5];

end

16'd256:begin

SNCOUT <= (dif3[24:8] == 17'h10000) ? 16'hFFFF : dif3[23:8];

end

default:begin

SNCOUT \le (dif3[24:8] == 17'h10000) ? 16'hFFFF : dif3[23:8];

end

endcase

end

/* ----- Making Enable signal ----- */

always@ ( posedge MCLK, posedge RST )

begin

if (RST)

begin /* Initialization */

ENBL <= 1'b0;

end

else

begin /* Making Enable signal */

if ( mclkcnt == DEC/2 - 1)

begin

ENBL <= 1'b1;

end

else

ENBL <= 1'b0;

end

end

endmodule

```

**Application Note**

### 3-5. 他の設計上注意事項

- a)  $V_{IN+}$ および  $V_{IN-}$ 端子が  $V_{DD1}$ -2V(例: $V_{DD1}$ が 5V の場合 5V-2V=3V)以上になりますとテストモード $^*$ が動作しますのでこのような設定では使用しないでください。

- ※ 補足説明: TLP7820/7920/7830/7930 テストモード

TLP7820/7920/7830/7930 では、クロック、エンコーダー,デコーダー回路、LED チップ動作確認のためのテストモード機能を付加しております。これにより、製品出荷検査時に仕様特性項目のみならず、内部信号の動作マージンが十分であることを確認し、品質向上に努めております。

# 4. アイソレーションアンプの応用設計(電圧検出用途)

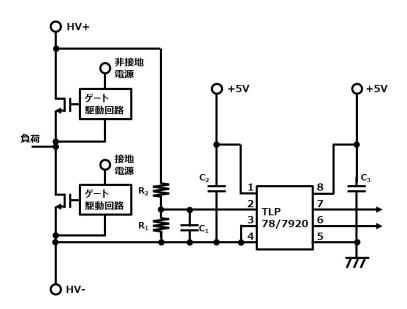

本項目では、図 9 のインバーター母線電圧検出の応用回路を代表例に、アイソレーションアンプの電圧検出応用設計時の注意事項 について述べます。

### 4-1. 電圧検出抵抗設計

- a) 母線電圧はアイソレーションアンプの入力電圧範囲に比較して十分大きいですが、抵抗分圧器で分圧することで、 電圧検出が可能となります。

- b) 分圧抵抗  $R_1, R_2$ と入力ラインバイパスコンデンサー  $C_1$ で形成されるローパスフィルターの設計定数により、応答性 (帯域幅)が変化します。 応答性は、分圧抵抗・バイパスコンデンサーの設計値変更(小化)により向上できますが、 分圧部電流・特性精度などとのトレードオフとなります。 使用用途に合わせ、調整頂くことを推奨します。

図 9. TLP7820/7920 を用いたインバーター母線電圧検出 応用回路

設計例) 抵抗分圧部の設計 (検出誤差を 0.5%以内としたい場合)

TLP7820 の入力抵抗 R<sub>i</sub>: 80kΩ

$R_1: R_1//R_i = R_1:(R_1 \times 80 k\Omega) / (R_1 + 80 k\Omega) = 1:0.995$

$0.995 = 80k\Omega / (R_1 + 80k\Omega)$

$0.995 \times R_1 + 0.995 \times 80 \text{k}\Omega = 80 \text{k}\Omega$

$R_1 = 402\Omega$

印加電圧を 400V、検出電圧を 200mV とした場合、

$400V: 200mV = (R_2 + 402\Omega): 402\Omega$

$200 \text{mV} \times \text{R}_2 + 200 \text{mV} \times 402 \Omega = 400 \text{V} \times 402 \Omega$

$R_2 = 804k\Omega$

### 5. データシート掲載項目以外の特性データ

本項では、当社アイソレーションアンプのデータシート掲載項目以外で応用上重要である特性について述べます。

### 5-1. アイソレーションアンプ TLP7820/7920 の出力雑音特性

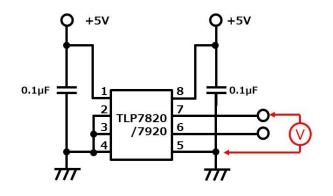

アイソレーションアンプ内部に搭載されている半導体 IC 内の熱雑音などの影響により、アイソレーションアンプ出力にはホワイトノイズ(出力電圧の経時ランダム変動)が見られます。 これを出力雑音特性と定義し、図 10 に示す測定回路図で、TLP7820/7920 の V<sub>OUT+</sub>端子出力の評価結果(V<sub>DD1</sub>=V<sub>DD2</sub>=5V, T<sub>a</sub>=25℃)を図 11 に示します。 本評価で、V<sub>OUT+</sub>単相出力の出力雑音は約 4 mV<sub>rms</sub>であることが確認されました。

図 10. V<sub>OUT+</sub>端子出力雑音評価回路

図 11. V<sub>OUT+</sub>端子出力雑音評価結果

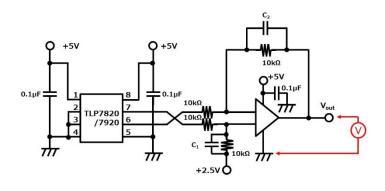

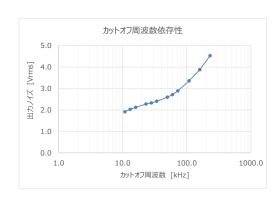

前記結果に対して、図 12 に示す後段ポストアンプを含む構成で、ポストアンプのカットオフ周波数をコンデンサー $C_{1}$ , $C_{2}$ により変化させ、出力雑音抑制効果を確認した結果( $T_{a}$ =25℃)を図 13 に示します。 ポストアンプのカットオフ周波数を低域化することにより、高域のホワイトノイズ成分が抑えられ、出力雑音特性は改善します。 一方で、信号周波数以上にカットオフ周波数を低域化した場合、ゲインの低下などを生じますので、使用条件に応じて適正化することが重要となります。

図 12. 出力ノイズ抑制検討評価回路

図 13.出力ノイズ抑制検討評価結果

### 5-2. アイソレーションアンプ TLP7820/7920 の SN 特性

オペアンプ・AD コンバーターの信号精度を示す指標として、電力スペクトルにおける信号と雑音の比率、信号の歪の程度を示す SN(Signal to noise)特性があります。 代表的な特性として、本項目では表 3 の内容で定義される SNR, SNDR, THD について述べます。

| 用語           | 記号                                             | 説明                     | 特性説明図                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 信号対雑音比       | SNR<br>Signal-to-noise ratio                   | 信号成分とノイズ成分(高調波は除く)の比率。 | 基本波(入力信号周波数) → 高調波成分 (基本波の                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 信号対(雑音+ひずみ)比 | SNDR<br>Signal-to-(noise and distortion) ratio | 信号成分とノイズ成分(高調波を含む)の比率。 | (#H / Bp) -40 (#A / K) / (#A / |

| 全高調波ひずみ      | THD Total harmonic distortion                  | 基本波と高調波の比率。            | -140<br>1 10 100 1000 10000 100000<br>周波教 (Hz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

表 3. SN 特性項目の定義

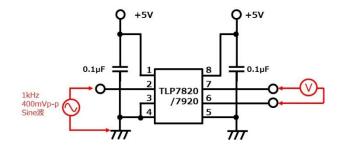

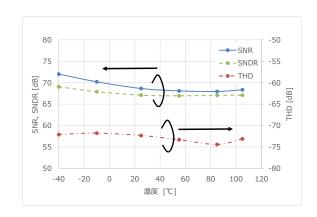

図 14 に示す測定回路図で、TLP7820/7920 の  $V_{OUT+}$ -  $V_{OUT-}$ 差動出力端子における SNR, SNDR, THD 温度依存性評価結果を図 15 に示します(入力周波数 1kHz, 入力振幅 400m $V_{p-p}$ ,  $V_{DD1}=V_{DD2}=5V$ , BW=22kHz)。 本評価で、 $T_a$ =25 $^{\circ}$ で SNR=69[dB], SNDR=67[dB], THD=-72[dB]の特性が確認されました。 なお、より SN 特性を高めるには、前記出力雑音同様にアイソレーションアンプ後段に信号のゲイン・歪を損なわない範囲で適正な雑音フィルターを挿入し、雑音を可能な限り抑えることが有効です。

図 14. V<sub>OUT+</sub>-V<sub>OUT-</sub>差動出力 SN 特性評価回路

図 15. SN 特性 温度依存性評価結果

### 5-3. アイソレーションアンプ TLP7820/7920 の PSRR 特性

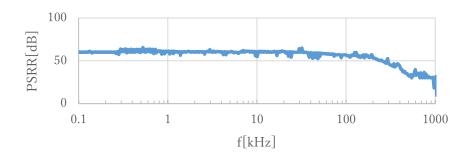

オペアンプ・AD コンバーターの電源に重畳するリップルの影響を受けずに、どれだけ安定した出力を得られるかを示す指標として、電源電圧変動除去比(PSRR: Power Supply Rejection Ratio) があります。PSRR は下式で定義され、値が高いほどリップルノイズの影響を受けにくく、安定した出力を得られることを示します。

TLP7820/7920 は、1 次側に $\Delta\Sigma$ ADC を備えるため、1 次側電源へのリップルが AD 変換値に影響を及ぼす可能性があります。

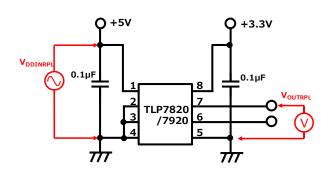

図 16 の測定回路図にて、TLP7820/7920 の PSRR を評価した結果を図 17 に示します。

$PSRR = 20log \frac{V_{DDINRPL}}{V_{OUTRPL}} [dB]$

$V_{DDINRPL}$ : アイソレーションアンプ電源( $V_{DD}$ )の

リップル成分

V<sub>OUTRPL</sub>: アイソレーションアンプ出力電圧 (V<sub>OUT</sub>) の

リップル成分

図 16. PSRR 測定回路

図 16 に示す測定回路図で、入力側電源(1pin)に 1Vp-p のリップルノイズを周波数 100Hz から 1000kHz の条件で重畳した時の出力電圧  $V_{OUT+}$  (7pin)をモニターした際の PSRR 評価結果を図 17 に示します。

(グラフの横軸(X軸)は周波数帯域、縦軸(Y軸)は PSRR を示します。)

図 17. PSRR 評価結果

リップルノイズの周波数帯域は、100kHz まで 60dB で維持され、200kHz 付近から悪化します。

この評価結果より、入力側電源に供給される直流電圧に、100kHZ以上の高い周波数帯域のリップルが重畳すると PSRR が低下する事が分かります。本機の動作や性能に影響がある場合は、PSRR に優れた LDO を介して電源供給を するまたは、バイパスコンデンサを追加することで、広帯域のリップルに対するフィルタとしての効果が期待できます。

# 6. TLP7820/7920/7830/7930 の特長

TLP7820/7920/7830/7930 では、他社相当品と基本特性で同等以上の特性を達成するとともに、本項で示す特長によりアプリケーション設計に貢献致します。

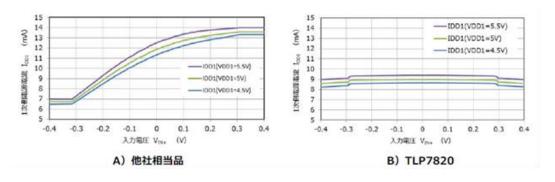

### 6-1. 1次側消費電流削減設計

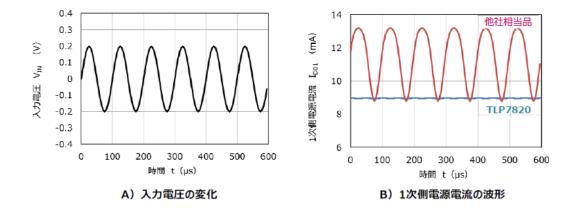

図 18 にアイソレーションアンプの入力電圧と 1 次側電源電流の関係を示します。 他社相当品は、入力電圧の変化に伴って 1 次側電源電流が変動します。 TLP7820 では、独自のデジタル変復調技術の導入により、入力電圧の振れ(推奨動作範囲:  $-0.2 \sim +0.2 \lor$ ) にかかわらず 1 次側電源電流は 9mA(標準)とほぼ一定に安定しています。 これにより最大回路電流も低く抑えられ、1 次側電源設計に貢献します。

図 19 に入力電圧をある周波数で変動させた場合の一次側電源電流の変化を示します。 他社相当品では入力電圧の変化に伴って1次側電源電流が9~13mA の範囲で変動しています。これに対して TLP7820 の場合は入力電圧が変化しても1次側電源電流はほぼ9mA を保ち安定しています。例えば、システム内ではアイソレーションアンプの1次側電源はブートストラップなどのフローティング電源が用いられますが、この電源に使われるコンデンサーは小容量(小型)のものを使用することができ、回路の小型化を図ることができます。この特性は、電源消費電力の削減や回路の小型化に寄与しますが、システムの高速動作が進んでいる背景下では電源の揺らぎによって発生するノイズ(EMI)による影響の抑制にも寄与します。

図 18. アイソレーションアンプの入力電圧と1 次側電源電流の関係

図 19. 入力電圧が変化した場合の 1 次側電源電流

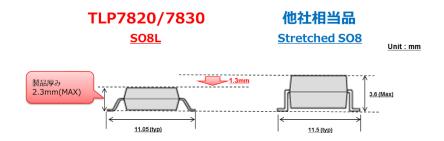

### 6-2. 新規 SO8L 薄型パッケージの採用

図 18 に、TLP7820/7830 および他社相当品のパッケージ側面図を示します。 TLP7820/7830 は、高さ 2.3mm の新薄型パッケージ SO8L 採用により、既存他社相当品以上の薄型化を実現しており、アプリケーションでの実装スペース 削減に貢献致します。

図 20. パッケージ側面図 TLP7820 vs 他社相当品

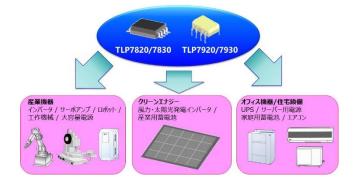

## 7.アプリケーション

TLP7820/7920/7830/7930 はインバーター回路を必要とする汎用インバーター・太陽光発電パワーコンディショナーなどの産業機器を中心に、UPS や家庭用蓄電池などの住宅設備機器まで幅広くご使用いただけます。

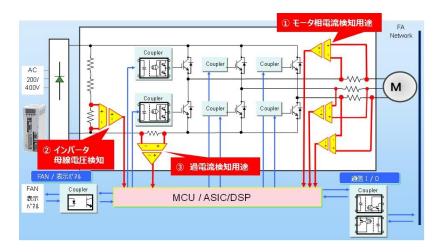

# 応用例) インバーター

図 21 にインバーター回路での応用例を示します。 下記①~③用途での信号検出での応用が可能です。

- ① モーター相電流検知用途

- ② インバーター母線電圧検知

- ③ 過電流検知用途

### 図 21. アイソレーションアンプのインバーター回路への応用例

# 変更履歴

| バージョン情報  | 日付         | 対応ページ数      | 変更内容                                                                                             |

|----------|------------|-------------|--------------------------------------------------------------------------------------------------|

| Rev. 1.0 | 2015/8/18  | -           | 初版                                                                                               |

| Rev. 2.0 | 2019/9/3   | 全ページ        | フォーマット刷新に伴う改版                                                                                    |

| Rev. 3.0 | 2019/11/6  | P7<br>P9,10 | <ul><li>・"3-4. 出力ライン設計 b)"へ<br/>単相出力使用時のコメント追加</li><li>・"5.データシート掲載項目以外の特性データ"を<br/>追加</li></ul> |

| Rev. 4.0 | 2020/8/17  | P7-9        | デジタルフィルタープログラム・構成例記載追加                                                                           |

| ReV. 5.0 | 2021/12/15 | P14         | "5-3 アイソレーションアンプ TLP7820/7920 の<br>PSRR 特性"を追加                                                   |

### 製品取り扱い上のお願い

株式会社東芝およびその子会社ならびに関係会社を以下「当社」といいます。

本資料に掲載されているハードウエア、ソフトウエアおよびシステムを以下「本製品」といいます。

- 本製品に関する情報等、本資料の掲載内容は、技術の進歩などにより予告なしに変更されることがあります。

- 文書による当社の事前の承諾なしに本資料の転載複製を禁じます。また、文書による当社の事前の承諾 を得て本資料を転載複製する場合でも、記載内容に一切変更を加えたり、削除したりしないでください。

- 当社は品質、信頼性の向上に努めていますが、半導体・ストレージ製品は一般に誤作動または故障する場合があります。本製品をご使用頂く場合は、本製品の誤作動や故障により生命・身体・財産が侵害されることのないように、お客様の責任において、お客様のハードウエア・ソフトウエア・システムに必要な安全設計を行うことをお願いします。なお、設計および使用に際しては、本製品に関する最新の情報(本資料、仕様書、データシート、アプリケーションノート、半導体信頼性ハンドブックなど)および本製品が使用される機器の取扱説明書、操作説明書などをご確認の上、これに従ってください。また、上記資料などに記載の製品データ、図、表などに示す技術的な内容、プログラム、アルゴリズムその他応用回路例などの情報を使用する場合は、お客様の製品単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。

- 本製品は、特別に高い品質・信頼性が要求され、またはその故障や誤作動が生命・身体に危害を及ぼす恐れ、膨大な財産損害を引き起こす恐れ、もしくは社会に深刻な影響を及ぼす恐れのある機器(以下"特定用途"という)に使用されることは意図されていませんし、保証もされていません。特定用途には原子力関連機器、航空・宇宙機器、医療機器(ヘルスケア除く)、車載・輸送機器、列車・船舶機器、交通信号機器、燃焼・爆発制御機器、各種安全関連機器、昇降機器、発電関連機器などが含まれますが、本資料に個別に記載する用途は除きます。特定用途に使用された場合には、当社は一切の責任を負いません。なお、詳細は当社営業窓口まで、または当社 Web サイトのお問い合わせフォームからお問い合わせください。

- 本製品を分解、解析、リバースエンジニアリング、改造、改変、翻案、複製等しないでください。

- ◆ 本製品を、国内外の法令、規則及び命令により、製造、使用、販売を禁止されている製品に使用することはできません。

- 本資料に掲載してある技術情報は、製品の代表的動作・応用を説明するためのもので、その使用に際して当社及び第三者の知的財産権その他の権利に対する保証または実施権の許諾を行うものではありません。

- 別途、書面による契約またはお客様と当社が合意した仕様書がない限り、当社は、本製品および技術情報に関して、明示的にも黙示的にも一切の保証(機能動作の保証、商品性の保証、特定目的への合致の保証、情報の正確性の保証、第三者の権利の非侵害保証を含むがこれに限らない。)をしておりません。

- 本製品、または本資料に掲載されている技術情報を、大量破壊兵器の開発等の目的、軍事利用の目的、 あるいはその他軍事用途の目的で使用しないでください。また、輸出に際しては、「外国為替及び外国 貿易法」、「米国輸出管理規則」等、適用ある輸出関連法令を遵守し、それらの定めるところにより必要 な手続を行ってください。

- 本製品の RoHS 適合性など、詳細につきましては製品個別に必ず当社営業窓口までお問い合わせください。本製品のご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用ある環境関連法令を十分調査の上、かかる法令に適合するようご使用ください。お客様がかかる法令を遵守しないことにより生じた損害に関して、当社は一切の責任を負いかねます。

# 東芝デバイス&ストレージ株式会社

https://toshiba.semicon-storage.com/jp/