# Electrical Characteristics of Bias Resistor Built-In Transistors (BRTs)

# **Outline:**

This document describes the absolute maximum rating, electrical characteristics, and product numbering methods in the datasheet of a built-in-resistor transistor (BRT, also called as a digital transistor) used as a semiconductor switches.

# **Table of Contents**

| 1. Introduction                                                                                           |

|-----------------------------------------------------------------------------------------------------------|

| 2. Part naming conventions                                                                                |

| 2.1. Part numbers beginning with RN5                                                                      |

| 2.2. Part numbers beginning with TDT7                                                                     |

| 3. Absolute maximum ratings                                                                               |

| 3.1. Definition of maximum ratings8                                                                       |

| 3.2. Collector-base voltage (V <sub>CBO</sub> )8                                                          |

| 3.3. Collector-emitter voltage (V <sub>CEO</sub> )8                                                       |

| 3.4. Emitter-base voltage (V <sub>EBO</sub> )9                                                            |

| 3.5. Collector current ( $I_c$ ), output current ( $I_o$ )                                                |

| 3.6. Collector power dissipation ( $P_c$ ), power dissipation ( $P_D$ )10                                 |

| 3.7. Junction temperature (T <sub>j</sub> )10                                                             |

| 3.8. Storage temperature (T <sub>stg</sub> )10                                                            |

| 4. Electrical characteristics of BRTs11                                                                   |

| 4.1. Collector cut-off current (I <sub>CBO</sub> , I <sub>CEO</sub> )11                                   |

| 4.1.1. Collector cut-off current (I <sub>CBO</sub> )                                                      |

| 4.1.2. Collector cut-off current (I <sub>CEO</sub> )11                                                    |

| 4.2. Emitter cut-off current (I <sub>EBO</sub> )13                                                        |

| 4.3. DC forward current gain $(h_{FE})$ 13                                                                |

| 4.4. Collector-emitter saturation voltage (V <sub>CE(sat)</sub> ), output voltage (V <sub>O(on)</sub> )14 |

| 4.5. Input voltage (ON) (V <sub>I(ON)</sub> , V <sub>I(on)</sub> )14                                      |

| 4.6. Input voltage (OFF) (V <sub>I(OFF)</sub> , V <sub>I(off)</sub> )15                                   |

| 4.7. Collector output capacitance (C <sub>ob</sub> )15                                                    |

| 4.8. Internal resistors16                                                                                 |

| 4.9. Series base resistor (R <sub>1</sub> )16                                                             |

| 4.10. Resistor ratio $(R_1/R_2)$ 17                                                                       |

| 4.11. Transition frequency ( $f_T$ )17                                                                    |

| 5. Related Links                                                                                          |

| 6. RESTRICTIONS ON PRODUCT USE                                                                            |

# List of Figures

| Figure 1-1 On and off states of a switch and a switch circuit using a BRT4                    |

|-----------------------------------------------------------------------------------------------|

| Figure 2-1 BRTs with different configurations5                                                |

| Figure 3-1 Collector-base voltage8                                                            |

| Figure 3-2 Collector-emitter voltage (NPN BRT)9                                               |

| Figure 3-3 Emitter-base voltage (NPN BRT)9                                                    |

| Figure 3-4 Collector power dissipation (P <sub>c</sub> ) (NPN BRT)10                          |

| Figure 4-1 I <sub>CBO</sub>                                                                   |

| Figure 4-2 I <sub>CEO</sub>                                                                   |

| Figure 4-3 I <sub>EBO</sub>                                                                   |

| Figure 4-4 h <sub>FE</sub>                                                                    |

| Figure 4-5 Relationships between $h_{FE}$ and $R_2$                                           |

| Figure 4-6 V <sub>CE(sat)</sub>                                                               |

| Figure 4-7 $V_{I(\text{ON})}14$                                                               |

| <b>Figure 4-8 V</b> <sub>I(OFF)</sub> 15                                                      |

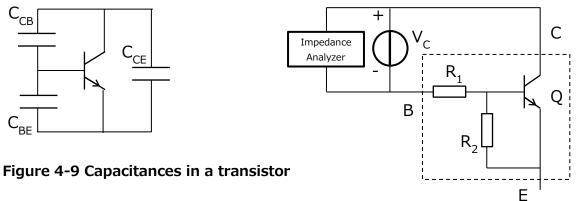

| Figure 4-9 Capacitances in a transistor16                                                     |

| Figure 4-10 Circuit for measuring collector output capacitance (Cob)                          |

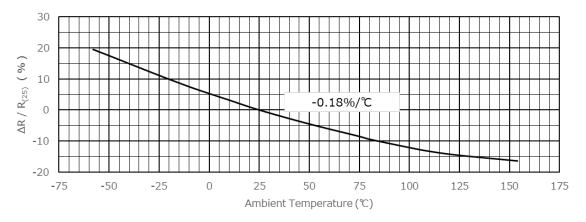

| Figure 4-11 Example of temperature dependence of internal resistor values (baseline: 25°C).16 |

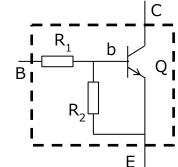

| Figure 4-12 BRT equivalent circuit                                                            |

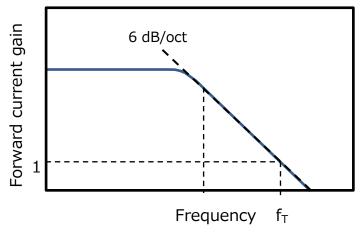

| Figure 4-13 h <sub>FE</sub> vs. frequency                                                     |

## 1. Introduction

TOSHIBA

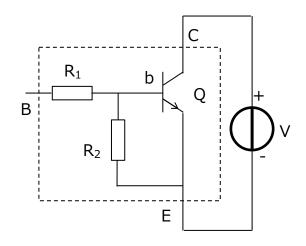

Also called digital transistors, bias resistor built-in transistors (BRTs) are used as on/off switches. BRTs incorporate a series base resistor and a base-emitter bias resistor necessary for such applications. Therefore, BRTs help reduce the parts count, size, and the time required for the assembly of electronic applications.

Toshiba provides BRTs with a wide range of resistor values to meet the requirements of various digital circuits. Toshiba's BRTs are available in single and dual (2-in-1) versions and in various packaging options.

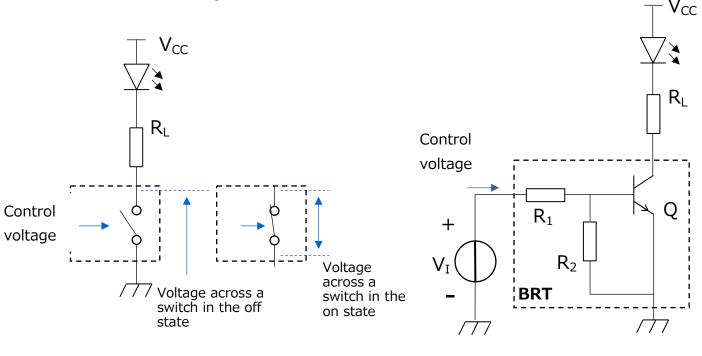

This application note mainly describes the maximum ratings and electrical characteristics shown in the BRT datasheets. They are specified under the assumption that BRTs are used as on/off switches. Specifications as switches include control voltage, withstand voltage across a switch in the off state (off-state withstand voltage), and voltage across a switch in the on state (on-resistance).

The relationships between these specifications and the BRT characteristics are as follows:

Control voltage  $\Rightarrow$  Input voltage (ON), input voltage (OFF) Voltage across a switch in the off state  $\Rightarrow$  Collector-emitter voltage Voltage across a switch in the on state  $\Rightarrow$  Collector-emitter saturation voltage

The requirements for these characteristics can be met by selecting BRTs with appropriate internal resistor values (R<sub>1</sub>and R<sub>2</sub>). See the application note "*Basics of Bias Resistor Built-in Transistors (BRTs)*" for the relationships between internal resistors and electrical characteristics as well as for selection guidelines.

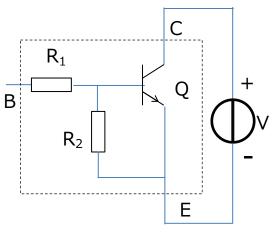

a) On and off states of a switch

b) Switch circuit using a BRT

Figure 1-1 On and off states of a switch and a switch circuit using a BRT

# 2. Part naming conventions

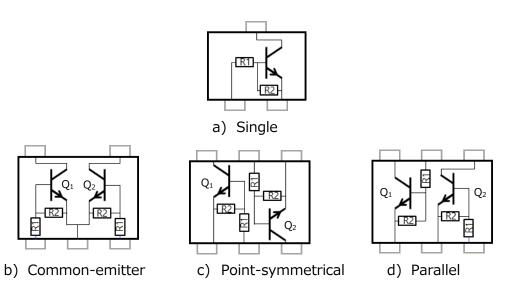

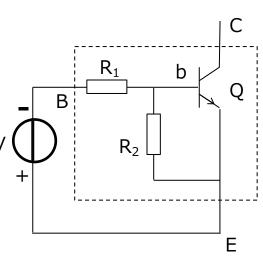

This section shows the basic part naming conventions that Toshiba uses for its BRTs. BRTs are available in several types with different configurations as shown in Figure 2-1.

## 2.1. Part numbers beginning with RN

Example: RN 1 3 14 JE

TOSHIBA

Symbol representing a package Number beginning with 01 indicating a combination of internal resistors (R<sub>1</sub> and R<sub>2</sub>). See Table 2-2. Number representing a package (e.g., USM package). See Table 2-1. Number representing a polarity 1: NPN transistor 2: PNP transistor 4: PNP-NPN transistor pair

Prefix indicating Toshiba's BRT

Figure 2-1 BRTs with different configurations

Table 2-1 Examples of package numbers and symbols

| Package | Package<br>code | Part number<br>example     | Number<br>representing<br>a package | Symbol<br>representing<br>a package | Туре                         |  |  |  |  |

|---------|-----------------|----------------------------|-------------------------------------|-------------------------------------|------------------------------|--|--|--|--|

|         | COT 722         |                            |                                     |                                     |                              |  |  |  |  |

| VESM    | SOT-723         | RN1 <b>1</b> 01 <b>MFV</b> | 1                                   | MFV                                 |                              |  |  |  |  |

| SSM     | SOT-416         | RN1 <mark>1</mark> 01      | 1                                   | Null                                | Single                       |  |  |  |  |

| USM     | SOT-323         | RN1 <mark>3</mark> 01      | 3                                   | Null                                | Single                       |  |  |  |  |

| S-Mini  | SOT-346         | RN1 <b>4</b> 01            | 4                                   | Null                                |                              |  |  |  |  |

| ESV     | SOT-553         | RN1701 <b>JE</b>           | 7                                   | JE                                  | 2-in-1                       |  |  |  |  |

| USV     | SOT-353         | RN1 <b>7</b> 01            | 7                                   | Null                                | (Common-emitter)             |  |  |  |  |

| SMV     | SOT-25          | RN1 <b>5</b> 01            | 5                                   | Null                                | (Common-emitter)             |  |  |  |  |

| ES6     | SOT-563         | RN1901FE                   | 9                                   | FE                                  | 2-in-1                       |  |  |  |  |

| US6     | SOT-363         | RN1 <mark>9</mark> 01      | 9                                   | Null                                | (Point-symmetrical/parallel) |  |  |  |  |

| SM6     | SOT-26          | RN1 <mark>6</mark> 01      | 6                                   | Null                                | (Fonte-symmetrical/paraller) |  |  |  |  |

Table 2-2 shows the combinations of internal resistors available for single and 2-in-1 BRTs. Most 2-in-1 BRTs consist of two combinations of identical transistors ( $Q_1$  and  $Q_2$ ) with resistors ( $R_1$  and  $R_2$ ) having equal values. Table 2-2 shows only such  $R_1$ - $R_2$  combinations. Toshiba also provides 2-in-1 BRTs consisting of two transistors with different-value resistors—namely, the RN46A1, RN49A1, and RN49A2. For  $R_1$ - $R_2$  combinations available with these BRTs, see their datasheets.

#### Table 2-2 Internal resistor combinations available with each type of BRT

As shown in the table below, the part number of the RNxxxx series contains a number that represents a combination of internal resistors.

(Example: RN11<u>01</u>MFV  $\Rightarrow$  R<sub>1</sub> = R<sub>2</sub> = 4.7 k $\Omega$ )

| a) Single        |                        |    |    |    |     |    |    |                          |     |    |  |

|------------------|------------------------|----|----|----|-----|----|----|--------------------------|-----|----|--|

|                  | $I_C = 100 \text{ mA}$ |    |    |    |     |    |    | $I_{C} = 800 \text{ mA}$ |     |    |  |

| $R_{1}(k\Omega)$ | 4.7                    | 10 | 22 | 47 | 100 | 8  | 1  | 2.2                      | 4.7 | 10 |  |

| 0.47             |                        |    |    |    |     |    |    |                          |     | 25 |  |

| 1                |                        | 14 |    |    |     | 19 | 21 |                          |     | 26 |  |

| 2.2              |                        | 15 |    | 05 |     |    |    | 22                       |     | 27 |  |

| 4.7              | 01                     | 16 |    | 06 |     | 10 |    |                          | 23  |    |  |

| 10               | 17                     | 02 |    | 07 |     | 11 |    |                          |     | 24 |  |

| 22               |                        |    | 03 | 08 |     | 12 |    |                          |     |    |  |

| 47               |                        | 18 | 09 | 04 |     | 13 |    |                          |     |    |  |

| 100              |                        |    |    |    | 30  | 31 |    |                          |     |    |  |

| 200              |                        |    |    |    |     | 32 |    |                          |     |    |  |

b) 2-in-1 BRTs with a common-emitter configuration

| R1 (kΩ) | 4.7 | 10 | 22 | 47 | $\infty$ |

|---------|-----|----|----|----|----------|

| 1       |     | 14 |    |    |          |

| 2.2     |     |    |    | 05 |          |

| 4.7     | 01  |    |    | 06 | 10       |

| 10      |     | 02 |    | 07 | 11       |

| 22      |     |    | 03 | 08 | 12       |

| 47      |     |    | 09 | 04 | 13       |

c) 2-in-1 BRTs in a point-symmetrical configuration (NPN\*2, PNP\*2, PNP+NPN)

| $R_1(k\Omega)$ $R_2(k\Omega)$ | 4.7 | 10 | 22 | 47 | 8  |

|-------------------------------|-----|----|----|----|----|

| 2.2                           |     |    |    | 05 |    |

| 4.7                           | 01  |    |    | 06 | 10 |

| 10                            |     | 02 |    | 07 | 11 |

| 22                            |     |    | 03 | 08 | 12 |

| 47                            |     |    | 09 | 04 |    |

#### d) 2-in-1 BRTs in a parallel configuration

|                                   |     |    |    | -  |    |

|-----------------------------------|-----|----|----|----|----|

| $R_2(k\Omega)$<br>R1(k $\Omega$ ) | 4.7 | 10 | 22 | 47 | 8  |

| 2.2                               |     |    |    | 65 |    |

| 4.7                               | 61  |    |    |    | 70 |

| 10                                |     | 62 |    | 67 | 71 |

| 22                                |     |    | 63 | 68 |    |

| 47                                |     |    | 69 | 64 |    |

e) 2-in-1 BRTs in a point-symmetrical configuration (NPN+PNP)

| $\begin{array}{c} R_{2}\left(k\Omega\right)\\ R_{1}\left(k\Omega\right)\end{array}$ | 4.7 | 10 | 22 | 47 | 8  |

|-------------------------------------------------------------------------------------|-----|----|----|----|----|

| 2.2                                                                                 |     |    |    | 05 |    |

| 4.7                                                                                 | 01  |    |    | 06 | 10 |

| 10                                                                                  |     | 02 |    | 07 | 11 |

| 22                                                                                  |     |    | 03 | 08 | 12 |

| 47                                                                                  |     |    | 09 | 04 |    |

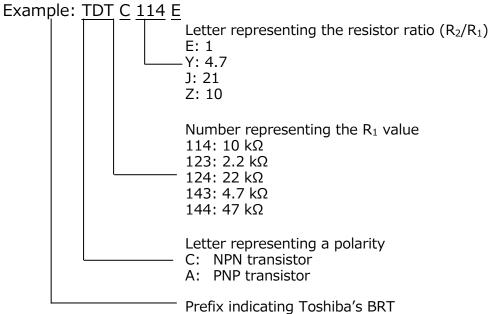

## 2.2. Part numbers beginning with TDT

# 3. Absolute maximum ratings

## 3.1. Definition of maximum ratings

The operation and function of semiconductor devices are substantially constrained by the applied voltage, current, temperature, power dissipation, and other factors.

Maximum ratings are the permissible values that must not be exceeded in order to ensure that semiconductor devices operate properly and maintain sufficient reliability. These values are specified as absolute maximum ratings.

None of the absolute maximum ratings must be exceeded, even instantaneously. Exposure to conditions exceeding the maximum ratings may damage or degrade a device.

They are specified at an ambient temperature of 25°C unless otherwise specified.

Overvoltage and overcurrent conditions cause internal degradation of semiconductor devices. In the worst-case scenario, these conditions might lead to wire melting by internal heating or permanent damage of semiconductor chips. Excessive storage or operating temperature might not only degrade semiconductor devices but also cause an open-circuit failure of wire bonds or degradation of hermeticity owing to a difference in thermal expansion coefficient among different types of materials that constitute a semiconductor device.

Absolute maximum ratings include the permissible voltage and current at each terminal, power dissipation, junction temperature, and storage temperature. The stresses specified as absolute maximum ratings differ from device to device. When parameters are shown as maximum ratings in datasheets and other technical documents, they mean absolute maximum ratings.

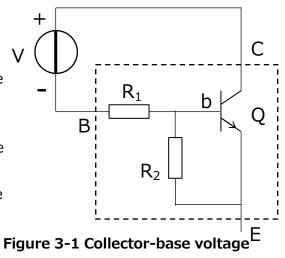

## 3.2. Collector-base voltage (V<sub>CBO</sub>)

Voltage is applied with the emitter (E) open as shown in 3-1 so that the pn junction between the base (b) and collector (C) is reverse-biased.  $V_{CBO}$  is the maximum voltage that can be applied across the collector (C) and base (B) terminals. When voltage (V) is low, current does not flow because the diode formed by the pn junction is off. As voltage is increased, leakage current begins to flow, as is the case with typical diodes, eventually degrading and destroying the BRT.

## 3.3. Collector-emitter voltage (V<sub>CEO</sub>)

Voltage is applied across the collector (C) and emitter (E) terminals with the base (B) terminal open-circuited as shown in Figure 3-2.  $V_{CEO}$  is the maximum voltage that can be applied across the collector (C) and emitter (E) terminals. When a BRT is used as a switch,  $V_{CEO}$  is the maximum voltage that can be applied when it is off.

When voltage is applied as shown in Figure 3-2, the pn junction between the base (b) and collector (C) is

reverse-biased while the pn junction between the base (b) and emitter (E) is forward-biased, as is the case with a transistor operating in the linear region. Since the pn junctions are biased in the same direction as for a transistor in the linear region, the BRT begins to operate as a transistor as the base current flows into Q.

As described in the previous section, application of large voltage across the collector and base terminals causes collector cut-off current ( $I_{CBO}$ ) to flow from the collector to the base. When  $I_{CBO}$  flows into the base, it is amplified by the DC forward current gain ( $h_{FE}$ ) to produce the amplified collector current. Therefore,  $V_{CEO}$  depends on the collector-base voltage  $V_{CBO}$ .

#### Figure 3-2 Collector-emitter voltage (NPN BRT)

## 3.4. Emitter-base voltage (V<sub>EBO</sub>)

Voltage is applied with the collector terminal (C) open as shown in Figure 3-3 so that the pn junction between the emitter (E) and base (b) is reverse-biased.

Since it is reverse-biased, no current flows through the built-in transistor when voltage is low. Current flows when voltage rises to such a level as to cause breakdown of the pn junction.

Since BRTs contain resistors R<sub>1</sub> and R<sub>2</sub>, when the reverse bias voltage is low, current flows through the built-in resistors. Therefore, the voltage divided by these resistors is applied across b and E. V<sub>EBO</sub> is defined as the external reverse bias voltage (V) at which this divided voltage exceeds the breakdown voltage. BRTs with a higher resistor ratio provide a higher V<sub>EBO</sub>. Generally, the emitter, base, and collector regions of an internal transistor of the BRT are doped in such a manner that the relationship of their dopant concentrations<sup>V</sup> becomes emitter > base > collector. Since the withstand voltage is inversely proportional to the dopant concentration, V<sub>EBO</sub> is smaller than V<sub>CBO</sub>.

Figure 3-3 Emitter-base voltage (NPN BRT)

## 3.5. Collector current (I<sub>c</sub>), output current (I<sub>o</sub>)

$I_C$  and  $I_0$  are the maximum currents that can flow through the collector pn junction in the reverse direction when a transistor is operating (when its operating point (Q point) is in the linear or saturation region). Since  $I_C$  and  $I_0$  are the maximum collector currents when a BRT is operating mainly in the linear region, they might be constrained by other electrical characteristics, depending on the operating condition. When the BRT goes into deep saturation (with low  $h_{FE}$ ), ensure that the power dissipated by  $R_1$  does not exceed 1/8 W (see Section 4.8, "Internal resistors").

## **3.6.** Collector power dissipation (P<sub>c</sub>), power dissipation (P<sub>D</sub>)

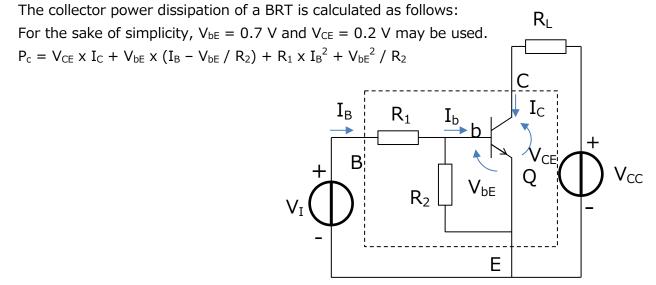

The power dissipated in a BRT includes not only collector power dissipation ( $I_C \times V_{CE}$ ) but also the power dissipated by other elements that constitute the BRT, including the power dissipated by the internal resistors and the emitter.

In the case of a typical bipolar transistor operating in the linear region, the emitter power dissipation is related to the base current of the internal transistor ( $I_b$ ) and the base-emitter voltage ( $V_{bE}$ ) of the internal transistor to which  $I_b$  flows. Because  $I_b = I_C / h_{FE}$ , the emitter power dissipation is small with respect to the collector current ( $I_C$ ) and collector-emitter voltage ( $V_{CE}$ ). Therefore, the collector power dissipation is treated as the power dissipation of a transistor. In the case of the BRT, the total power dissipated by all the constituent elements is called the collector power dissipation, following the conventional nomenclature for bipolar transistors.

For an example of calculation of collector power dissipation, see Section 6, "Calculating the power dissipation of a BRT," of the application note *Basics of Bias Resistor Built-in Transistors (BRTs)*.

Figure 3-4 Collector power dissipation (P<sub>c</sub>) (NPN BRT)

## 3.7. Junction temperature (T<sub>j</sub>)

$T_j$  is the maximum temperature at the pn junction of an internal transistor. At higher temperatures, numerous electrons and holes are generated in both the p and n regions. This reduces differences between p-type and n-type semiconductors, causing their interfaces not to function as pn junctions. Consequently, excessive current might flow in the transistor, leading to destruction. In addition, the service life of semiconductor devices is affected by temperature (see the description of the Arrhenius model in Section 3.3.3 of *Reliability Handbook*). It is therefore necessary to take not only temperature characteristics but also temperature derating into consideration.

## 3.8. Storage temperature (T<sub>stg</sub>)

$T_{\text{stg}}$  is the temperature range in which BRTs should be stored without voltage application.

## 4. Electrical characteristics of BRTs

Since BRTs are generally used as switches, their use as switches is assumed in this section. The following subsections describe the electrical characteristics to be considered when using BRTs as switches.

## 4.1. Collector cut-off current ( $I_{CBO}$ , $I_{CEO}$ )

There are two definitions of collector cut-off current:  $I_{CBO}$  and  $I_{CEO}$ .  $I_{CBO}$  is related to  $V_{CBO}$  described in Section 3.2, "Collector-base voltage ( $V_{CBO}$ )," whereas  $I_{CEO}$  is related to  $V_{CEO}$  described in Section 3.3, "Collector-emitter voltage ( $V_{CEO}$ )."

## 4.1.1. Collector cut-off current (ICBO)

Voltage is applied across the collector (C) and base (B) terminals with the emitter (E) terminal open-circuited as shown in Figure 4-1 so that the pn junction between the collector and base is reverse-biased. This causes the pn-junction diode between the collector (C) and base (b) of the internal transistor (Q) to be reverse-biased. As this reverse bias increases, leakage current begins to flow. The maximum leakage current is defined as the collector cut-off current ( $I_{CBO}$ ).

$I_{\mbox{\scriptsize CBO}}$  is highly dependent on temperature. It is expressed as follows as a function of temperature:

$I_{CBO}(T_x) = I_{CBO}(T_0) * exp(K * (T_x - T_0))$

$T_0$ : Reference temperature (K)

K: Temperature coefficient, which is generally  $0.07/^{\circ}$ C to  $0.08/^{\circ}$ C for silicon transistors

As described in Section 3.3,  $V_{CEO}$  is related to  $I_{CBO}$ , which increases as temperature increases, as indicated by the above equation. Care should be exercised in the use of BRTs particularly when the collector-emitter voltage in the off state is close to the maximum rated  $V_{CEO}$  value and the ambient temperature is high.

## 4.1.2. Collector cut-off current (ICEO)

Voltage is applied across the collector (C) and emitter (E) terminals with the base (B) terminal open-circuited as shown in Figure 4-2. The pn junction between the collector (C) and base (b) is reverse-biased whereas the pn junction between the base (b) and emitter (E) is forward-biased. As described in Section 3.3, "Collector-emitter voltage ( $V_{CEO}$ )," the leakage current flowing between C and b is amplified, producing collector cut-off current ( $I_{CEO}$ ).

Figure 4-1 I<sub>CBO</sub>

Figure 4-2 I<sub>CEO</sub>

#### 4.2. Emitter cut-off current (I<sub>EBO</sub>)

Emitter cut-off current ( $I_{EBO}$ ) is the leakage current that flows when the pn junction between the base (b) and emitter (E) is reverse-biased with the collector (C) terminal open-circuited. A BRT incorporates resistors R<sub>1</sub> and R<sub>2</sub>. For example, in the case of an NPN BRT, the emitter-base voltage divided by R<sub>1</sub> / (R<sub>1</sub>+R<sub>2</sub>) is applied across E and b in the low-voltage region, as described in Section 3.4, "Emitter-base voltage (V<sub>EBO</sub>)." As this voltage approaches the breakdown voltage of the pn junction between b and E, leakage current begins to flow. BRTs with a higher resistor ratio (R<sub>1</sub>/R<sub>2</sub>) cause higher leakage current. At the same time, I<sub>R2</sub> flows through R<sub>2</sub>. BRTs with an equal resistor ratio cause lower leakage current if they contain R<sub>1</sub> with a higher value.

Figure 4-3 IEBO

## 4.3. DC forward current gain (h<sub>FE</sub>)

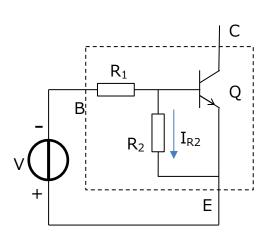

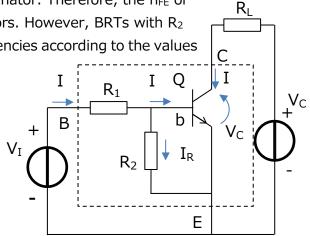

The DC forward current gain ( $h_{\text{FE}}$ ) is defined as follows:

$h_{FE} = I_C / I_B = I_C / (I_b + I_{R2})$

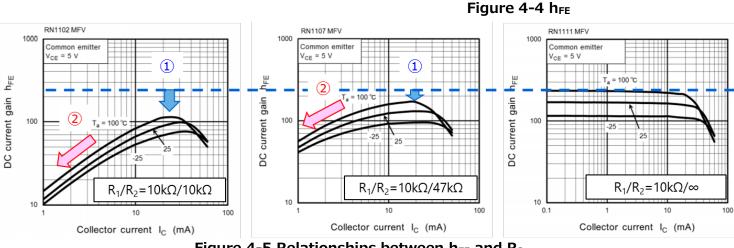

Unlike typical bipolar transistors, the  $h_{FE}$  equation of a BRT has a term of  $I_{R2}$  (i.e., current flowing through internal resistor  $R_2$ ) in the denominator. Therefore, the  $h_{FE}$  of BRTs without  $R_2$  is equal to that of typical bipolar transistors. However, BRTs with  $R_2$  provide lower  $h_{FE}$  because of  $I_{R2}$ .  $h_{FE}$  has the following tendencies according to the values of the internal resistors:

- 1. BRTs with higher  $R_2$  provide higher  $h_{FE}$ .

- 2. BRTs with low  $R_2$  exhibit a considerable decrease in  $h_{\text{FE}}$  in the low-current region.

When the internal transistor is on,  $V_{bE} \approx 0.7 \text{ V}$ . Therefore,  $I_{R2}$  is almost constant. Therefore, BRTs with large  $I_{R2}$  (i.e., low  $R_2$ ) exhibit a decrease in  $h_{FE}$  in the low-current region because it is greatly affected by  $I_{R2}$ .

Figure 4-5 Relationships between h<sub>FE</sub> and R<sub>2</sub>

#### 4.4. Collector-emitter saturation voltage (VCE(sat)), output voltage (VO(on))

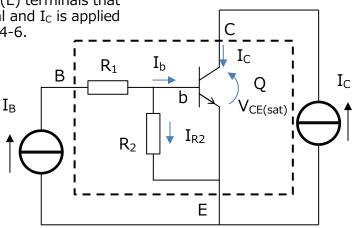

The collector-emitter saturation voltage ( $V_{CE(sat)}$ ) is defined as a voltage drop across the collector (C) and emitter (E) terminals that occurs when  $I_B$  is applied to the base (B) terminal and  $I_C$  is applied to the collector (C) terminal, as shown in Figure 4-6.

This method is employed to obtain uniform measurement results. For example, under the condition  $I_C = 20 \times I_B$ ,  $V_{CE(sat)}$  equals the collector-emitter voltage in the saturation state when  $h_{FE} = 20$ .

TOSHIBA

For some BRTs, this voltage is specified as output voltage ( $V_{O(on)}$ ). In this case, replace  $I_B$  with  $I_I$  and  $I_C$  with  $I_O$  in the above paragraph.

Figure 4-6 V<sub>CE(sat)</sub>

## 4.5. Input voltage (ON) (V<sub>I(ON)</sub>, V<sub>I(on)</sub>)

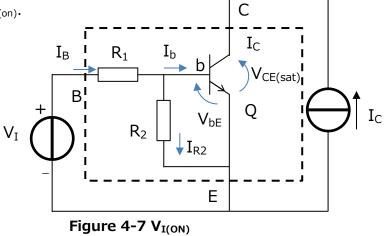

The input voltage required to turn on the internal transistor of a BRT in the saturation region is specified as  $V_{I(ON)}$  or  $V_{I(on)}$  (see Figure 4-7).

- $V_{I(ON)}$ : In the case of the RNxxxx series,  $V_{I(ON)}$  is defined as the input voltage (i.e., base-emitter (B-E) voltage) that provides the specified collector current (I<sub>C</sub>) and collector-emitter voltage ( $V_{CE}$ ).

- $V_{I(on)}$ : In the case of the TDTCxxx and TDTAxxx series,  $V_{I(on)}$  is defined as the input voltage (i.e., base-emitter (B-E) voltage) at which a BRT turns on at the specified output current ( $I_0$ ) and collector-emitter (C-E) voltage ( $V_0$ ).

Set the input voltage as follows to ensure that a BRT turns on in the saturation region under the test conditions shown in the datasheet:

- When  $V_{I(ON)}$  is specified, apply a voltage higher than the maximum  $V_{I(ON)}$  value.

- When  $V_{I(on)}$  is specified, apply a voltage higher than the minimum  $V_{I(on)}$  value.

When the internal transistor is on under the test conditions, the  $V_{I(ON)}$  and  $V_{I(on)}$  of BRTs are affected by the internal resistors.

All BRTs provide equal input current for the internal transistor and equal voltage at each terminal under the specified test conditions.

However,  $I_{R2}$  (=  $V_{bE}$  /  $R_2$ ) and therefore  $I_B$  (=  $I_b$  +  $I_{R2}$ ) differ from BRT to BRT.

$V_{I(ON)} = \underline{V_{bE}} + R_1 \times (I_b + I_{R2}) = V_{bE} + R_1 \times \underline{I_b} + R_1 \times \underline{V_{bE}} / R_2$

The underscored parameters are equal for all BRTs. Therefore,  $V_{I(on)}$  is proportional to  $R_1$  and inversely proportional to  $R_2$ .

These relationships also apply to  $V_{I(on)}$ .

## 4.6. Input voltage (OFF) (V<sub>I(OFF)</sub>, V<sub>I(off)</sub>)

TOSHIBA

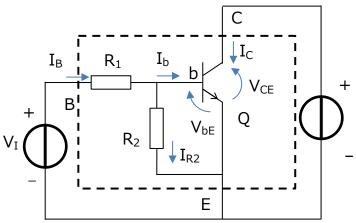

$V_{I(\text{OFF})}$  and  $V_{I(\text{off})}$  are the input voltages required to turn off a BRT.

- V<sub>I(OFF)</sub>: In the case of the RNxxxx series, V<sub>I(OFF)</sub> is defined as the input voltage (i.e., base-emitter (B-E) voltage) that provides the specified collector current (I<sub>C</sub>) and collector-emitter voltage (V<sub>CE</sub>).

- V<sub>I(off)</sub>: In the case of the TDTCxxx and TDTAxxx series, V<sub>I(on)</sub> is defined as the input voltage (i.e., base-emitter (B-E) voltage) at which a BRT turns off at the specified output current (I<sub>0</sub>) and collector-emitter (C-E) voltage (V<sub>0</sub>).

Set the input voltage as follows to ensure that a BRT turns off under the test conditions shown in the datasheet:

- When  $V_{I(OFF)}$  is specified, apply a voltage lower than the minimum  $V_{I(OFF)}$  value.

- When  $V_{I(\text{off})}$  is specified, apply a voltage lower than the maximum  $V_{I(\text{off})}$  value.

$V_{I(\text{OFF})}$  and  $V_{I(\text{off})}$  are also affected by the internal resistors of BRTs.

In Figure 4-8, the internal transistor is off. The base-emitter voltage ( $V_{bE}$ ) at which the internal transistor turns off is determined by its threshold, irrespective of the internal resistors. Because the base current ( $I_b$ ) does not flow to the internal transistor in the off state,  $V_{I(OFF)}$  is expressed as follows. Since  $V_{bE}$  is a fixed value intrinsic to the internal transistor lower than its threshold,  $V_{I(OFF)}$  is proportional to the resistor ratio ( $R_1/R_2$ ).

$V_{bE} = R_2 / (R_1 + R_2) \times V_{I(OFF)}$  $V_{I(OFF)} = (R_1 / R_2 + 1) \times V_{bE}$ These relationships also apply to V

These relationships also apply to  $V_{I(\mbox{\scriptsize off})}.$

#### Figure 4-8 VI(OFF)

## 4.7. Collector output capacitance (Cob)

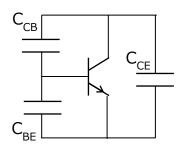

A transistor consists of two pn junctions: a base-emitter junction ( $C_{BE}$ ) and a collector-base junction ( $C_{CB}$ ). These pn junctions have parasitic capacitances (junction capacitances). In addition, discrete transistors such as BRTs, which have the collector region on the backside of a chip, have collector-emitter capacitance ( $C_{CE}$ ).

Collector output capacitance ( $C_{ob}$ ) is measured by applying V<sub>C</sub> across the collector (C) and base (B) terminals with the emitter (E) terminal open-circuited as shown in the test circuit of Figure 4-10.

Therefore,  $C_{ob}$  can be expressed as:

$C_{ob} = C_{CB} + (C_{BE} \times C_{CE}) / (C_{BE} + C_{CE})$

In the case of BRTs,  $C_{CE}$  is smaller than other capacitances. Hence,  $C_{ob}$  is almost equal to  $C_{CB}$ .

When a typical bipolar transistor operates in the linear region, C<sub>CB</sub> acts as Miller capacitance, reducing a current gain. However, this hardly ever occurs in BRTs that are mainly used in the saturation region as switches.

## Figure 4-10 Circuit for measuring collector output capacitance ( $C_{ob}$ )

#### 4.8. Internal resistors

The internal resistors of BRTs are polysilicon resistors whose power dissipation is specified to be 1/8 W. In most cases, the input voltage (V<sub>I</sub>) applied across the base (B) and emitter (E) terminals is constrained by the collector current  $(I_c)$  and collector power dissipation  $(P_c)$ . However, in the case of applications in which BRTs go into deep saturation with low h<sub>FE</sub>, V<sub>I</sub> might be constrained by the power dissipation of the internal resistors.

The values of the internal resistors are dependent on temperature. Figure 4-11 shows an example of their temperature characteristics curve.

Figure 4-11 Example of temperature dependence of internal resistor values (baseline: 25°C)

## 4.9. Series base resistor (R<sub>1</sub>)

R<sub>1</sub> is defined as the value of the resistor connected in series between the base terminal (B) of a BRT and the base (b) of the internal transistor in it. This resistor is a polysilicon resistor. Its value decreases with temperature as shown in Section 4.8, "Internal resistors." There is ±30% variation in R<sub>1</sub> from the typical value shown in the datasheet. This variation is caused by the variations in the resistor width and dopant concentration in polysilicon as well as temperature.

$R_1$  converts the voltage applied to the base (B) terminal of a BRT into current. A bipolar transistor is a current-driven device. It is difficult to control a bipolar transistor with voltage because the collector current varies substantially when it is driven directly with voltage.  $R_1$  in a BRT makes it relatively easier to control the collector current.

When a BRT is on, the internal transistor operates in the saturation region where  $h_{FE}$  (=I<sub>C</sub>/I<sub>b</sub>) is in the range of 10 to 20, depending on the input voltage. Therefore, the base current (I<sub>B</sub>) that flows through R<sub>1</sub> is relatively large—on the order of several milliamperes. Since the allowable power dissipation of R<sub>1</sub> is 1/8 W, the maximum input voltage (V<sub>I</sub>) of BRTs with a high R<sub>1</sub> value is determined by the value of R<sub>1</sub>.

## 4.10. Resistor ratio (R<sub>1</sub>/R<sub>2</sub>)

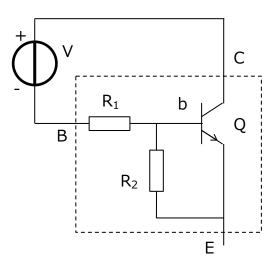

The value of  $R_2$  is not specified on its own. Instead, the resistor ratio  $(R_1/R_2)$  is specified. There is ±10% variation in  $R_1/R_2$  from the typical value.

The input voltage (ON) specification ( $V_{I(ON)}$ ) is dependent on  $R_1/R_2$ . Since the base current ( $I_B$ ) does not flow immediately before the transistor turns on, the voltage applied to the B terminal ( $V_I$ ) is divided by  $R_1$  and  $R_2$ . Let the turn-on threshold voltage of the internal transistor be  $V_{bE}$ . Then,  $V_{bE}$  can be expressed as:

$V_{bE} = R_2 / (R_1 + R_2) * V_{I(ON)}$

The V<sub>bE</sub> of BRTs is not affected by the values of R<sub>1</sub> and R<sub>2</sub> if they contain the same transistor:  $V_{I(ON)} = V_{bE}^* (R_1 + R_2) / R_2 = V_{bE}^* (1 + R_1 / R_2)$ Hence,  $V_{I(ON)}$  is dependent on the resistor ratio (R<sub>1</sub>/R<sub>2</sub>).

Figure 4-12 BRT equivalent circuit

## 4.11. Transition frequency (f<sub>T</sub>)

The transition frequency  $(f_T)$  is defined as the frequency at which the internal transistor provides a DC forward current gain  $(h_{FE})$  of 1. In the linear region,  $h_{FE}$  decreases at a rate of 6 dB per octave. Therefore,  $h_{FE}$  is measured at a low frequency (e.g., at 1 MHz) first, and then a straight line is drawn with a negative slope of 6 dB/octave.  $f_T$  is defined as a frequency at which  $h_{FE}$ becomes 1 on this line.

Figure 4-13 h<sub>FE</sub> vs. frequency

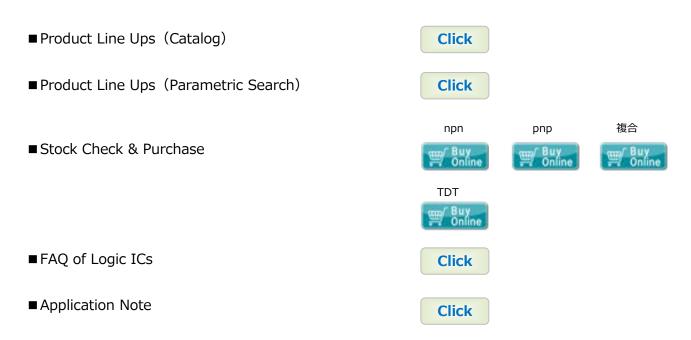

To download the application note Basics of Bias Resistor Built-in Transistors (BRTs)  $\rightarrow$  Click Here

To view the lineup of BRTs  $\rightarrow$  Click Here

TOSHIBA

To download Reliability Handbook  $\rightarrow$  Click Here

# TOSHIBA

# 5. Related Links

# **6. RESTRICTIONS ON PRODUCT USE**

TOSHIBA

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative or contact us via our website.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

# **Toshiba Electronic Devices & Storage Corporation**

https://toshiba.semicon-storage.com/