東芝 Bi-CMOS 形リニア集積回路 シリコン モノリシック

# TB9083FTG

Automotive GATE-driver for Brushless motor

## 1. 概要

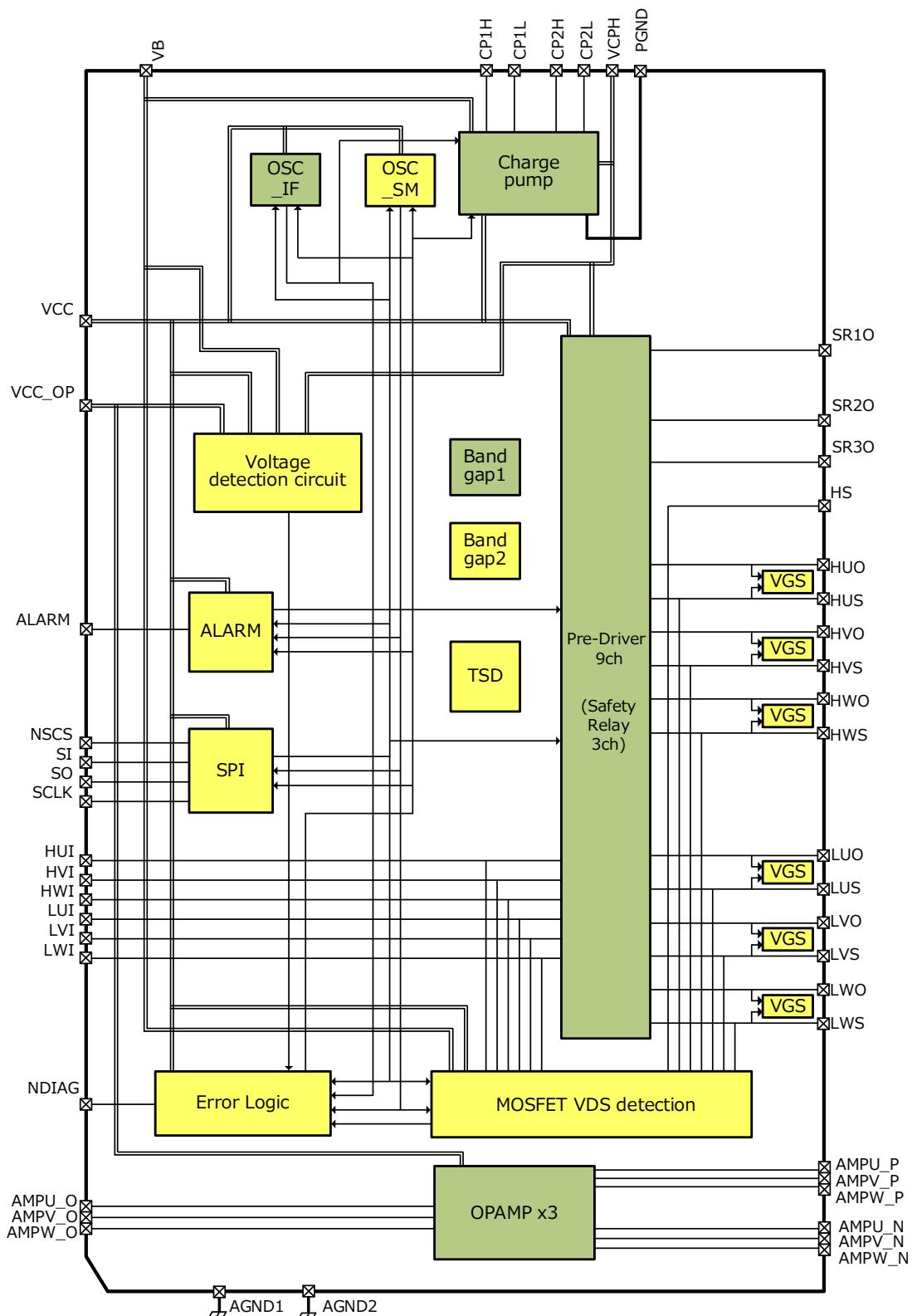

TB9083FTG は、車載向けブラシレスモーター用のプリドライバーICです。

3相プリドライバー以外に、セーフティーリレー用のプリドライバーも内蔵しています。

チャージポンプ、モーター電流検出回路、発振回路、SPI 通信回路を内蔵しています。

各種異常検出機能を搭載しており、異常検出条件、異常検出後の動作を設定できます。各設定については、SPI 通信を介して設定可能です。

また、各種異常検出機能の正常動作を診断するための ABIST/LBIST 機能を搭載しています。

質量: 137.9mg (標準)

## 2. 用途

EPS 用、電動ブレーキ用、ポンプ用など

## 3. 特長

- 3相プリドライバー : PWM 制御 ~20kHz

- フェールセーフリレー用プリドライバー

- チャージポンプ回路内蔵

- 電流検出回路内蔵

- 各種異常検出機能内蔵

(低電圧(VB, VCC, VCC\_OP) / 高電圧(VCC, VCC\_OP, VCPH, 外部 MOSFET の VGS) / 過熱 / 外部 MOSFET の VDS 検出)

- ABIST / LBIST 機能内蔵

- AEC-Q100/AEC-Q006 適合

- 動作電圧範囲 : VB=4.5~28V, VCC=3.0~5.5V

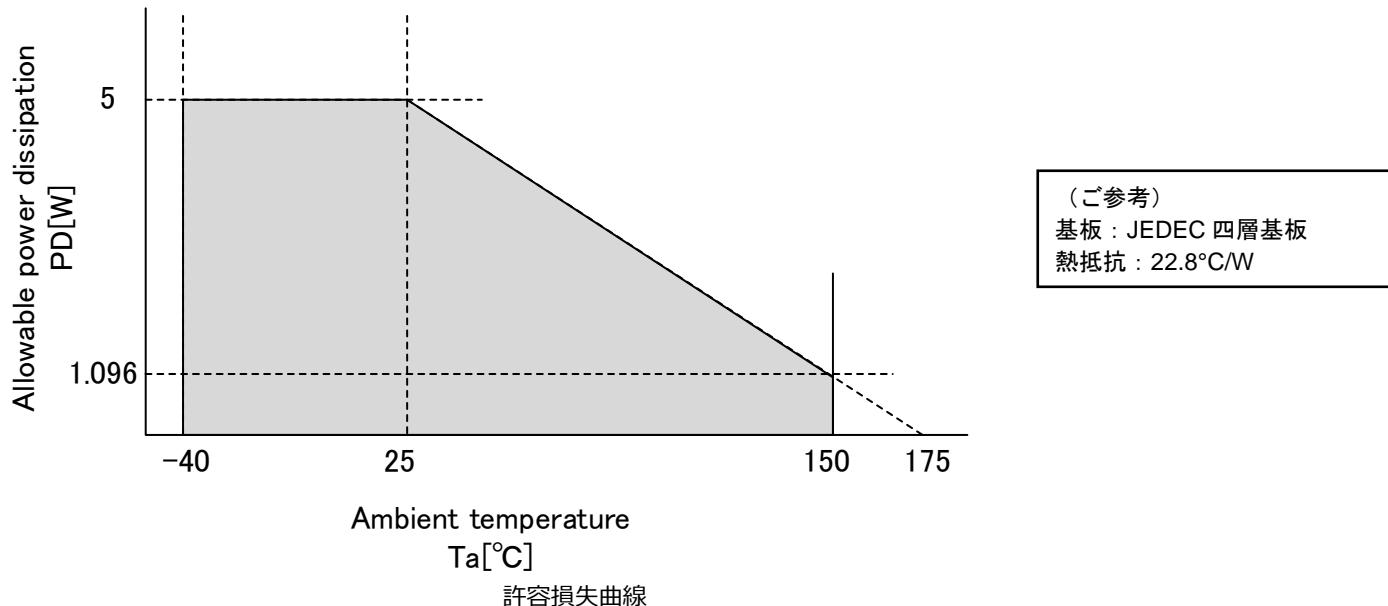

- 動作温度範囲 : Ta=-40~150°C, Tj=-40~175°C

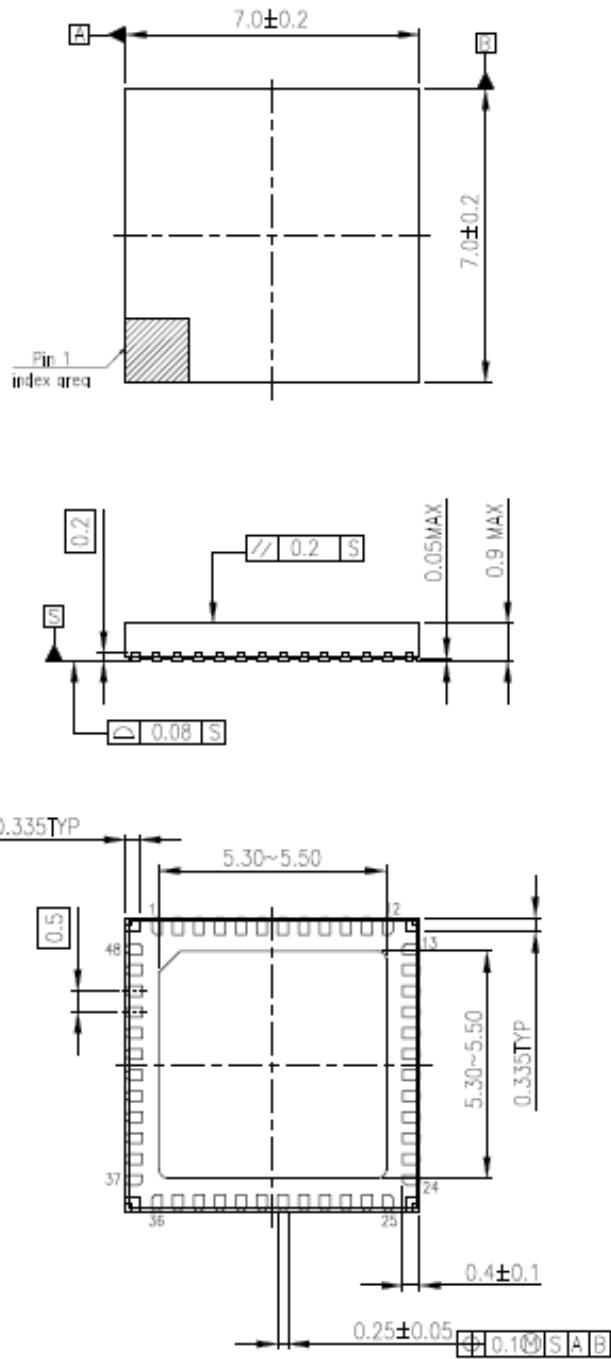

- パッケージ : P-VQFN48-0707-0.50-005(Wettable flank, 0.5mm ピッチ)

- 機能安全

- ISO 26262 2nd edition に従った開発。 ASIL-D Capable.

- セーフティーマニュアルや安全分析のレポート

- 機能冗長およびABISTとLBIST内蔵

- CRCチェックを備えたSPIインターフェイス

包装箱ラベルに”[G]/RoHS COMPATIBLE”、”[G]/RoHS [[Chemical symbol(s) of controlled substance(s)]”、”RoHS COMPATIBLE”または”RoHS COMPATIBLE, [[Chemical symbol(s) of controlled substance(s)]]>MCV”と記載があれば、本製品はその記載の意味において欧州RoHS 指令(2011 / 65 / EU)対応品です。

製品量産開始時期

2022-11

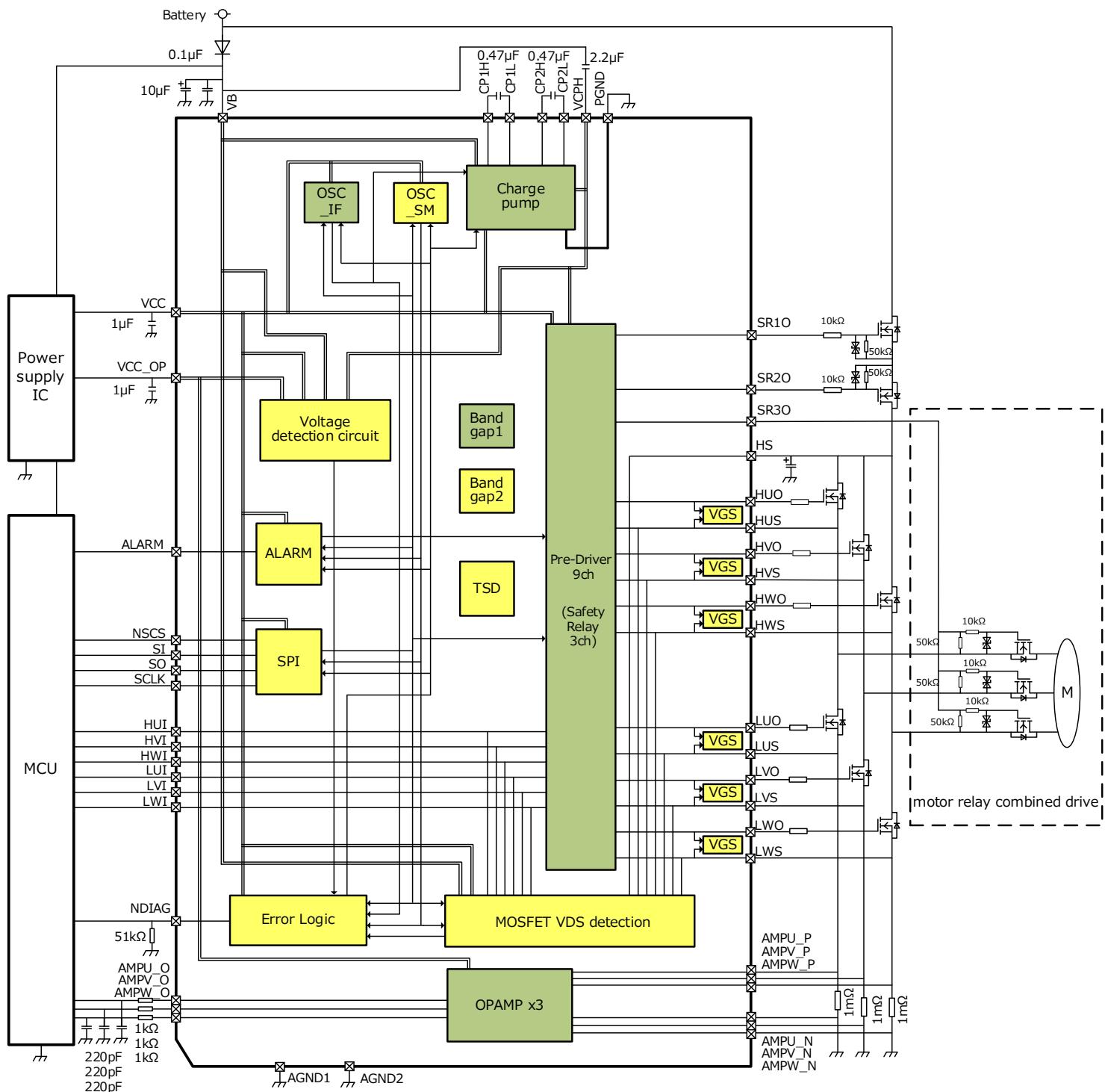

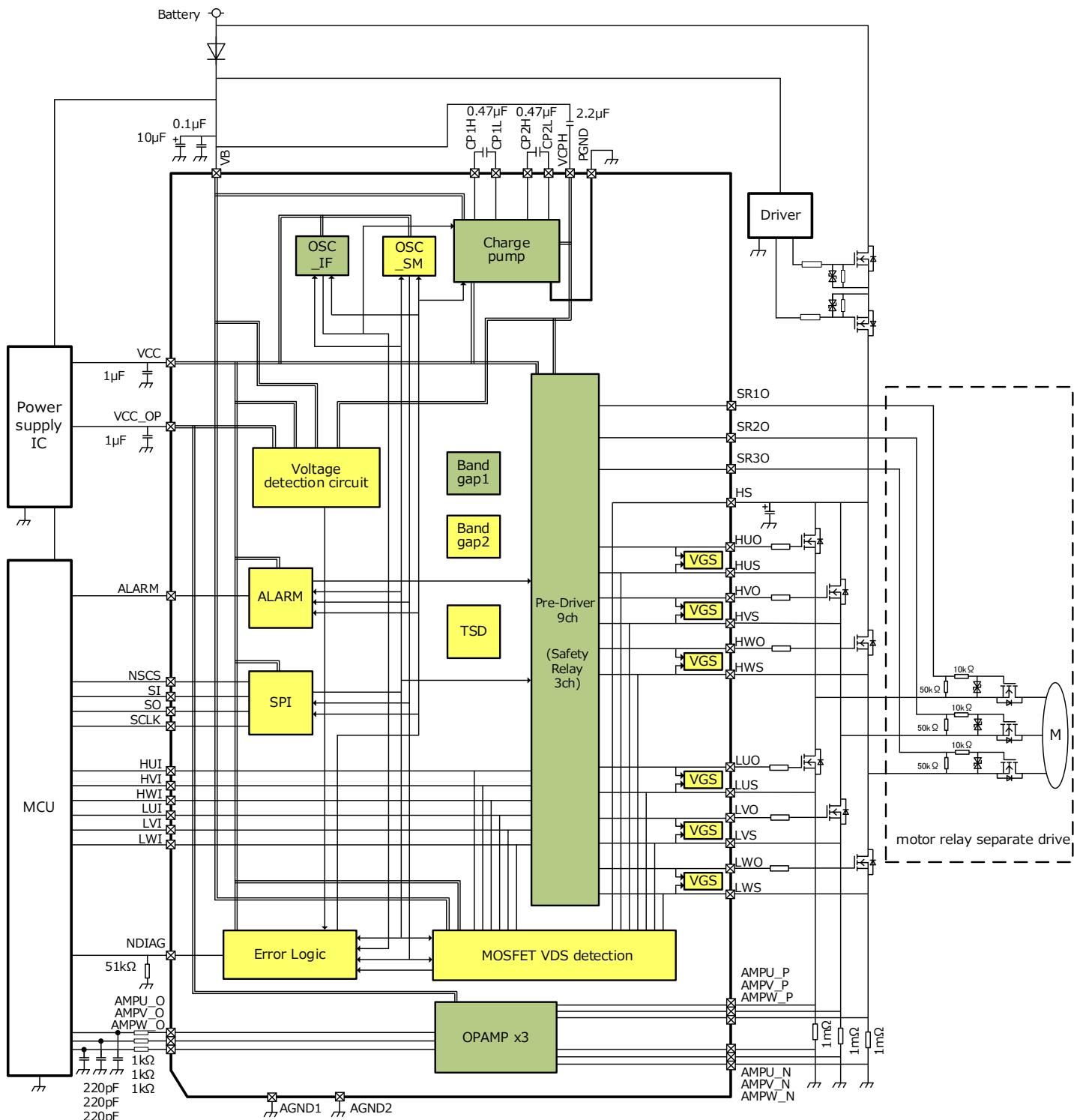

## 4. ブロック図

- ・ ブロック図内の機能ブロック/接続配線などは機能説明のため、一部省略または簡略化している場合があります。

(個別ブロック図も含む)

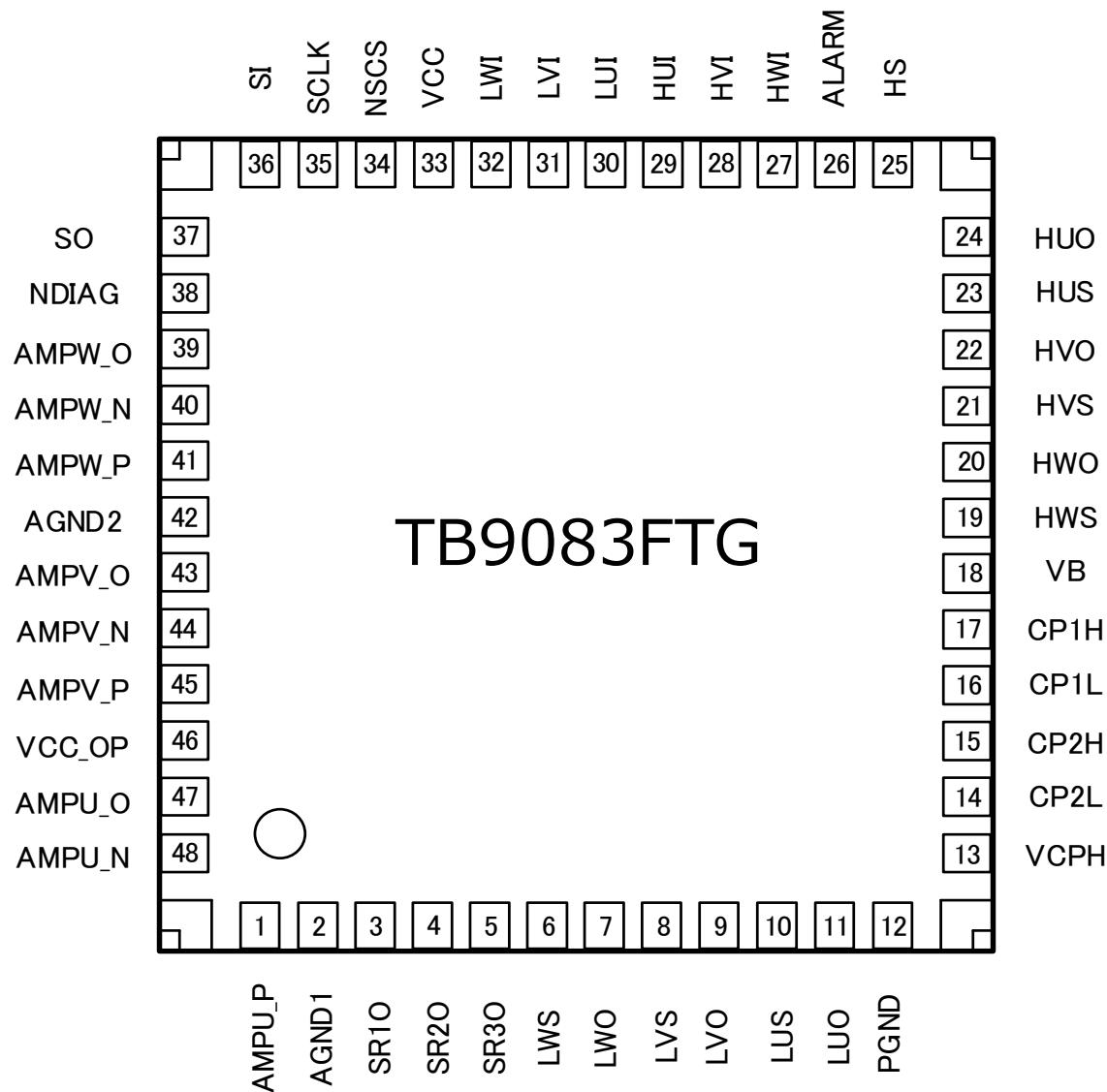

## 5. 端子配置図(Top View)

## 6. 端子説明

| No. | 端子名称   | 入出力 | 機能                          | Pull-up/down 抵抗                   | 備考                                               |

|-----|--------|-----|-----------------------------|-----------------------------------|--------------------------------------------------|

| 1   | AMPU_P | IN  | 電流検出アンプ(+)入力(U 相)           | —                                 | —                                                |

| 2   | AGND1  | GND | アナログ回路用グランド 1               | —                                 | —                                                |

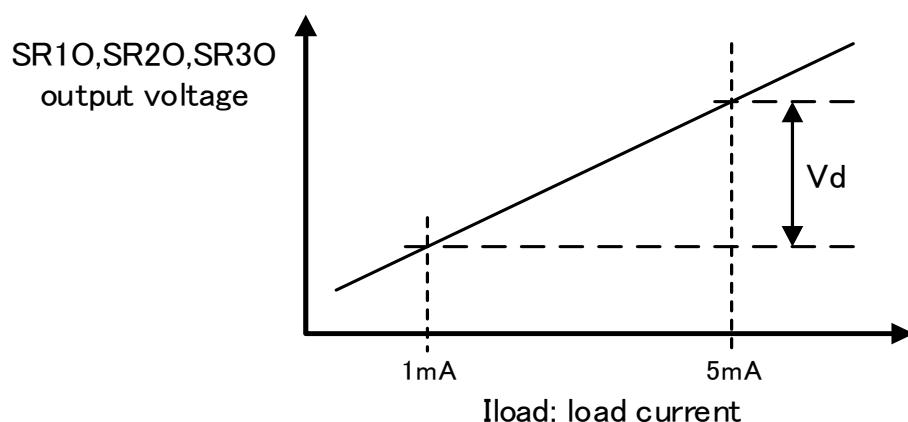

| 3   | SR1O   | OUT | セーフティーリレー 1 出力              | —                                 | SPI 設定                                           |

| 4   | SR2O   | OUT | セーフティーリレー 2 出力              | —                                 | SPI 設定                                           |

| 5   | SR3O   | OUT | セーフティーリレー 3 出力              | —                                 | SPI 設定                                           |

| 6   | LWS    | IN  | プリドライバー基準入力(W 相ローサイドソース)    | —                                 | —                                                |

| 7   | LWO    | OUT | プリドライバー出力(W 相ローサイド)         | Pull-down to LWS                  | —                                                |

| 8   | LVS    | IN  | プリドライバー基準入力(V 相ローサイドソース)    | —                                 | —                                                |

| 9   | LVO    | OUT | プリドライバー出力(V 相ローサイド)         | Pull-down to LVS                  | —                                                |

| 10  | LUS    | IN  | プリドライバー基準入力(U 相ローサイドソース)    | —                                 | —                                                |

| 11  | LUO    | OUT | プリドライバー出力(U 相ローサイド)         | Pull-down to LUS                  | —                                                |

| 12  | PGND   | GND | パワーグランド                     | —                                 | —                                                |

| 13  | VCPh   | 電源  | チャージポンプ電圧                   | Pull-down to VB                   | —                                                |

| 14  | CP2L   | OUT | チャージポンプ 2 段目出力              | —                                 | —                                                |

| 15  | CP2H   | I/O | チャージポンプ 2 段目ドライブ出力          | —                                 | —                                                |

| 16  | CP1L   | OUT | チャージポンプ 1 段目出力              | —                                 | —                                                |

| 17  | CP1H   | I/O | チャージポンプ 1 段目ドライブ出力          | —                                 | —                                                |

| 18  | VB     | 電源  | バッテリー電源                     | —                                 | —                                                |

| 19  | HWS    | IN  | プリドライバー基準入力(W 相ハイサイドソース)    | Pull-up to HS<br>Pull-down to LWS | プルアップ、プルダウン<br>抵抗は外部 FET 検査モード(FET_TEST)時のみ接続可能。 |

| 20  | HWO    | OUT | プリドライバー出力(W 相ハイサイド)         | Pull-down to HWS                  | —                                                |

| 21  | HVS    | IN  | プリドライバー基準入力(V 相ハイサイドソース)    | Pull-up to HS<br>Pull-down to LVS | プルダウン、プルアップ<br>抵抗は外部 FET 検査モード(FET_TEST)時のみ接続可能。 |

| 22  | HVO    | OUT | プリドライバー出力(V 相ハイサイド)         | Pull-down to LVS                  | —                                                |

| 23  | HUS    | IN  | プリドライバー基準入力(U 相ハイサイドソース)    | Pull-up to HS<br>Pull-down to LUS | プルダウン、プルアップ<br>抵抗は外部 FET 検査モード(FET_TEST)時のみ接続可能。 |

| 24  | HUO    | OUT | プリドライバー出力(U 相ハイサイド)         | Pull-down to HUS                  | —                                                |

| 25  | HS     | IN  | 外部 MOSFET の VDS 検出入力(ハイサイド) | —                                 | —                                                |

| 26  | ALARM  | IN  | プリドライバーイネーブル信号              | Pull-down to GND                  | —                                                |

| 27  | HWI    | IN  | プリドライバー入力(W 相ハイサイド)         | Pull-down to GND                  | —                                                |

| 28  | HVI    | IN  | プリドライバー入力(V 相ハイサイド)         | Pull-down to GND                  | —                                                |

| 29  | HUI    | IN  | プリドライバー入力(U 相ハイサイド)         | Pull-down to GND                  | —                                                |

| 30  | LUI    | IN  | プリドライバー入力(U 相ローサイド)         | Pull-down to GND                  | —                                                |

| 31  | LVI    | IN  | プリドライバー入力(V 相ローサイド)         | Pull-down to GND                  | —                                                |

| 32  | LWI    | IN  | プリドライバー入力(W 相ローサイド)         | Pull-down to GND                  | —                                                |

| 33  | VCC    | 電源  | 外部 5V/3.3V 電源               | —                                 | —                                                |

| 34  | NSCS   | IN  | SPI チップセレクト                 | Pull-up to VCC                    | —                                                |

| 35  | SCLK   | IN  | SPI クロック入力                  | Pull-down to GND                  | —                                                |

| 36  | SI     | IN  | SPI 入力                      | Pull-down to GND                  | —                                                |

| 37  | SO     | OUT | SPI 出力                      | —                                 | —                                                |

| 38  | NDIAG  | OUT | エラー出力                       | —                                 | —                                                |

| 39  | AMPW_O | OUT | 電流検出アンプ出力(W 相)              | —                                 | —                                                |

| 40  | AMPW_N | IN  | 電流検出アンプ(−)入力(W 相)           | —                                 | —                                                |

| 41  | AMPW_P | IN  | 電流検出アンプ(+)入力(W 相)           | —                                 | —                                                |

| 42  | AGND2  | GND | アナログ回路用グランド 2               | —                                 | —                                                |

| 43  | AMPV_O | OUT | 電流検出アンプ出力(V 相)              | —                                 | —                                                |

| 44  | AMPV_N | IN  | 電流検出アンプ(−)入力(V 相)           | —                                 | —                                                |

| 45  | AMPV_P | IN  | 電流検出アンプ(+)入力(V 相)           | —                                 | —                                                |

| 46  | VCC_OP | 電源  | 電流検出アンプ用電源(5V/3.3V)         | —                                 | —                                                |

| 47  | AMPU_O | OUT | 電流検出アンプ出力(U 相)              | —                                 | —                                                |

| 48  | AMPU_N | IN  | 電流検出アンプ(−)入力(U 相)           | —                                 | —                                                |

## ●内部信号名解説

| 内部信号名        | 概要                             | 状態       |           |

|--------------|--------------------------------|----------|-----------|

|              |                                | H        | L         |

| (abst_pass)  | ABIST 正常信号                     | ABIST 正常 | ABIST 異常  |

| (abst_end)   | ABIST 終了信号                     | ABIST 終了 | ABIST 未終了 |

| (gate_en_u)  | プリドライバー出力イネーブル信号(U 相)          | Enable   | Disable   |

| (gate_en_v)  | プリドライバー出力イネーブル信号(V 相)          | Enable   | Disable   |

| (gate_en_w)  | プリドライバー出力イネーブル信号(W 相)          | Enable   | Disable   |

| (gate_en_r)  | プリドライバー出力イネーブル信号(セーフティーリレー)    | Enable   | Disable   |

| (gate_off_u) | ALARM 要因以外のプリドライバー停止指示信号 U 相   | —        | —         |

| (gate_off_v) | ALARM 要因以外のプリドライバー停止指示信号 V 相   | —        | —         |

| (gate_off_w) | ALARM 要因以外のプリドライバー停止指示信号 W 相   | —        | —         |

| (gate_off_r) | ALARM 要因以外のリレー停止指示信号           | —        | —         |

| (cp_en)      | チャージポンプ回路イネーブル信号               | Enable   | Disable   |

| (cp_off)     | チャージポンプ停止指示信号                  | —        | —         |

| (vbl)        | VB 低電圧検出信号                     | 検出       | 解除        |

| (vcphh)      | VCPh 高電圧検出信号                   | 検出       | 解除        |

| (vcl1)       | VCC 低電圧検出信号 1                  | 検出       | 解除        |

| (vcl2)       | VCC 低電圧検出信号 2                  | 検出       | 解除        |

| (por_x)      | 内部リセット信号                       | リセット解除   | リセット      |

| (vccopl)     | VCC_OP 低電圧検出信号                 | 検出       | 解除        |

| (vccoph)     | VCC_OP 高電圧検出信号                 | 検出       | 解除        |

| (vch)        | VCC 高電圧検出信号                    | 検出       | 解除        |

| (tsddet)     | 過熱検出信号                         | 検出       | 解除        |

| (clk4m_if)   | 4MHz クロック(IF 用源振)              | —        | —         |

| (clk4m_sm)   | 4MHz クロック(SM 用源振)              | —        | —         |

| (vdsuho)     | 外部 MOSFET の VDS 検出信号(U 相ローサイド) | 検出       | 解除        |

| (vdsvho)     | 外部 MOSFET の VDS 検出信号(V 相ローサイド) | 検出       | 解除        |

| (vdswho)     | 外部 MOSFET の VDS 検出信号(W 相ローサイド) | 検出       | 解除        |

| (vdsulo)     | 外部 MOSFET の VDS 検出信号(U 相ハイサイド) | 検出       | 解除        |

| (vdsvlo)     | 外部 MOSFET の VDS 検出信号(V 相ハイサイド) | 検出       | 解除        |

| (vdswlo)     | 外部 MOSFET の VDS 検出信号(W 相ハイサイド) | 検出       | 解除        |

## &lt;使用電源 / GND リスト&gt;

| 略号    | 端子名         | 機能・用途               |

|-------|-------------|---------------------|

| Vb    | VB          | バッテリー電源             |

| Vcc   | VCC         | 外部 5V/3.3V 電源       |

| Vccop | VCC_OP      | 電流検出アンプ用電源(5V/3.3V) |

| Vcph  | VCPh        | チャージポンプ電圧(ハイサイド)    |

| AGND  | AGND1,AGND2 | アナログ回路用グランド         |

| PGND  | PGND        | パワーグランド             |

## 7. 機能動作説明

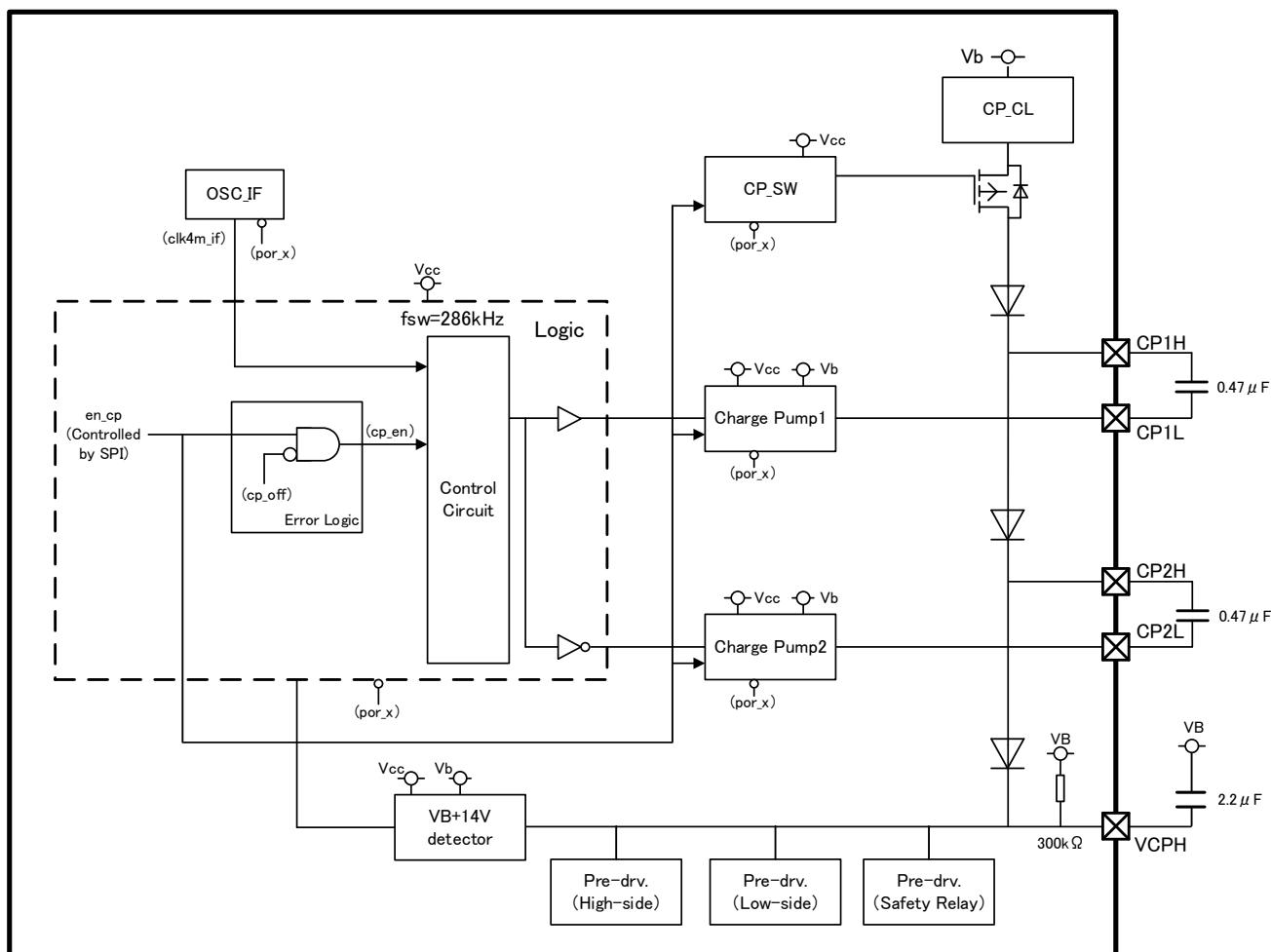

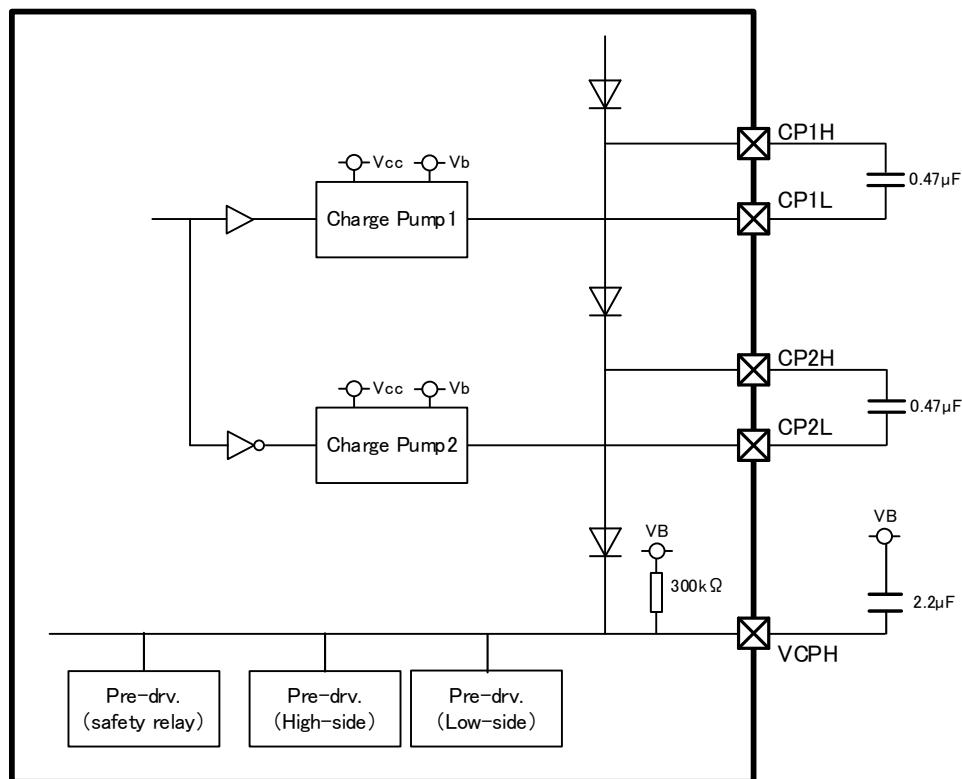

### 7.1. チャージポンプ回路

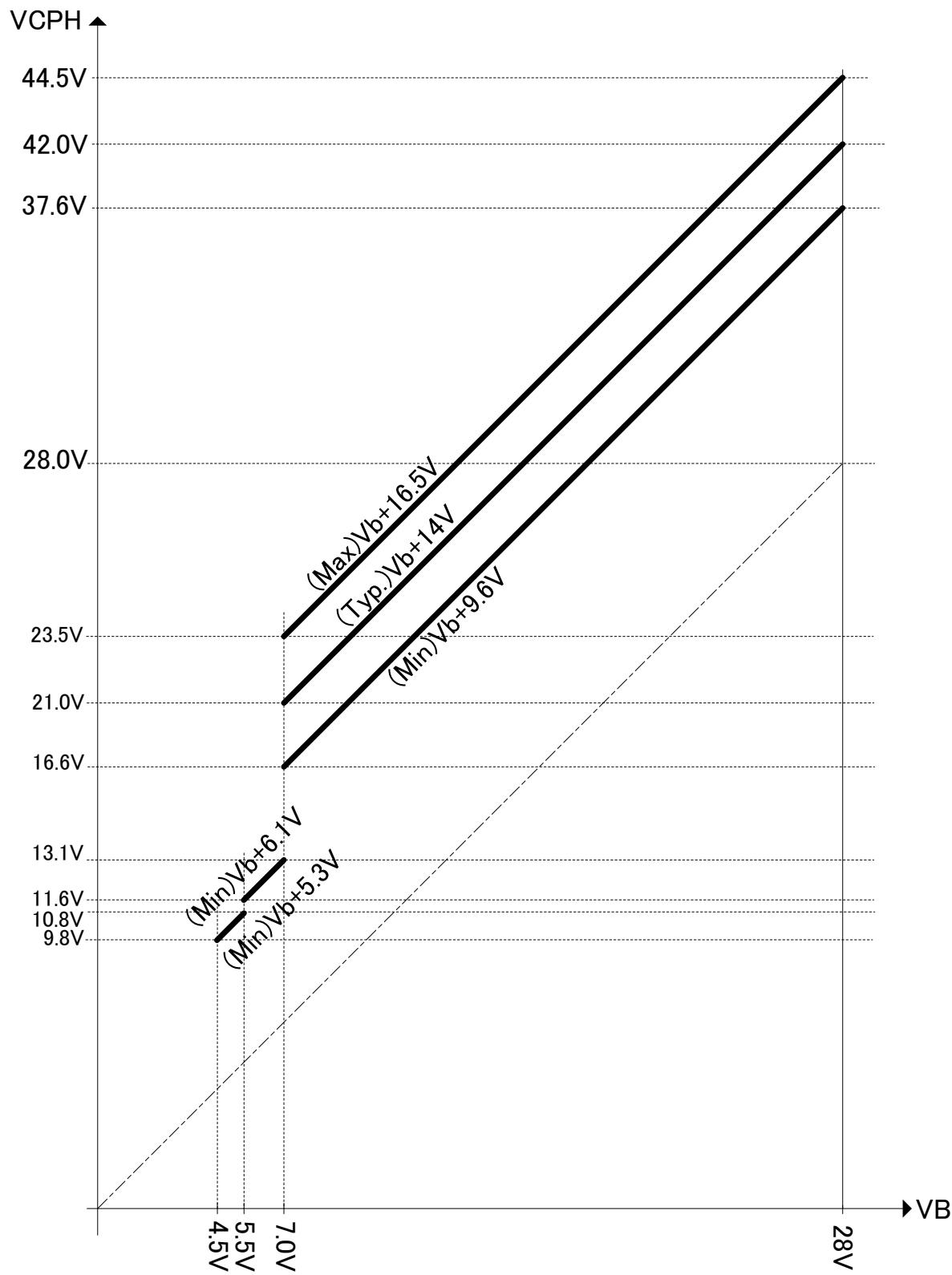

外付け MOSFET を駆動するプリドライバー用のチャージポンプ  $V_{cph}$  が  $V_b+14V$ (Typ.)まで上がると内部回路の制御によりチャージポンプは動作を停止します。

チャージポンプの  $V_b$  側にはスイッチ回路(CP\_SW)を内蔵しています。CP\_SW はトランジスターをオフさせ  $V_b$  から  $V_{cph}$  への供給を停止させることができます。CP\_SW によりトランジスターをオフすると、チャージポンプが動作を停止し VCPH 端子の出力電圧が  $V_b$  となります。VCC 電圧が VCC 低電圧検出しきい値以下となる条件で、CP\_SW はトランジスターをオフします。また、SPI 通信により制御し CP\_SW にトランジスターをオフさせることも可能です。VB より VCPH への供給ラインの電流を監視して規定の電流に制限する電流制限回路 CP\_CL を備えています。

Fig. 7.1-a チャージポンプ回路ブロック図

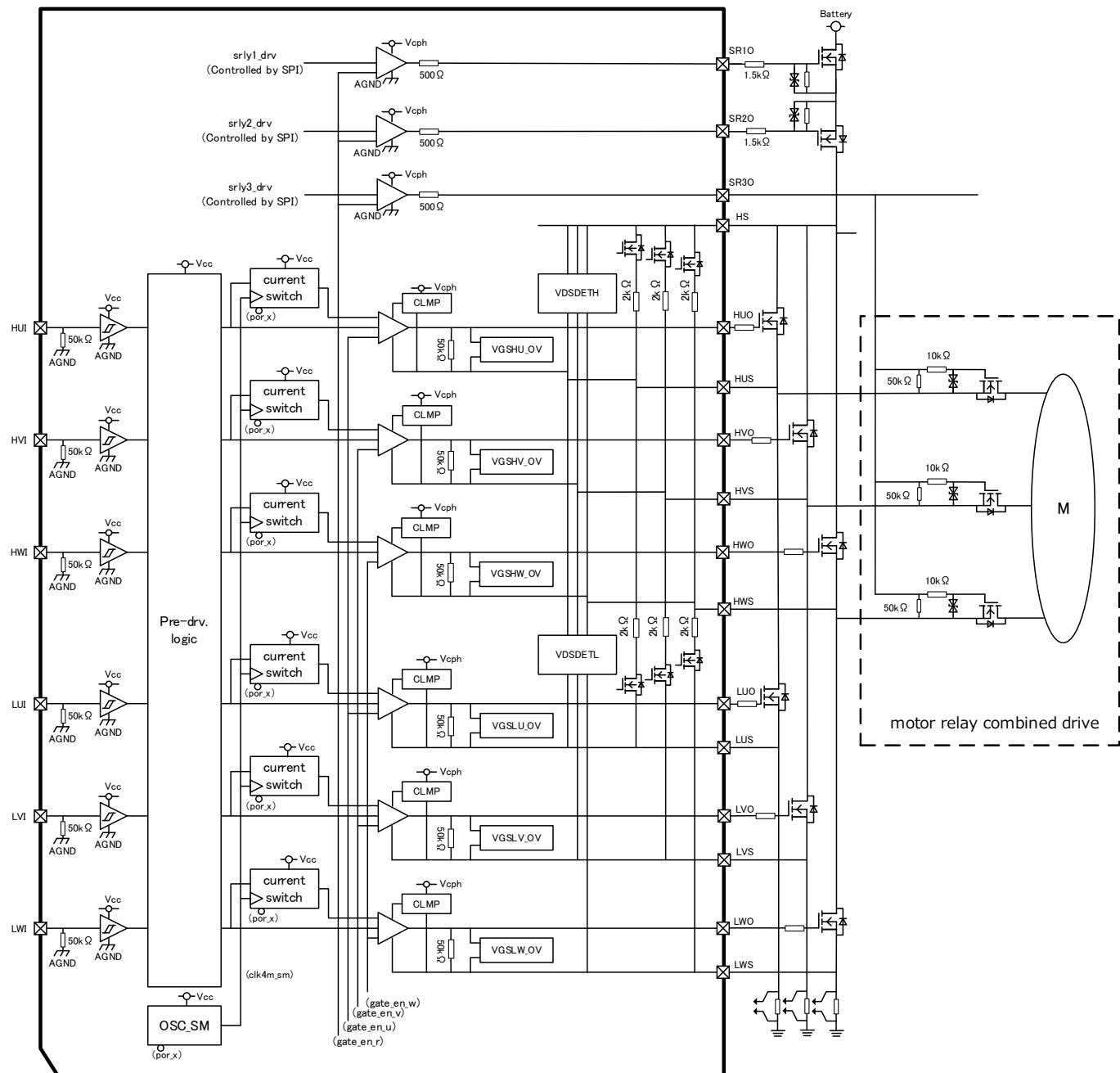

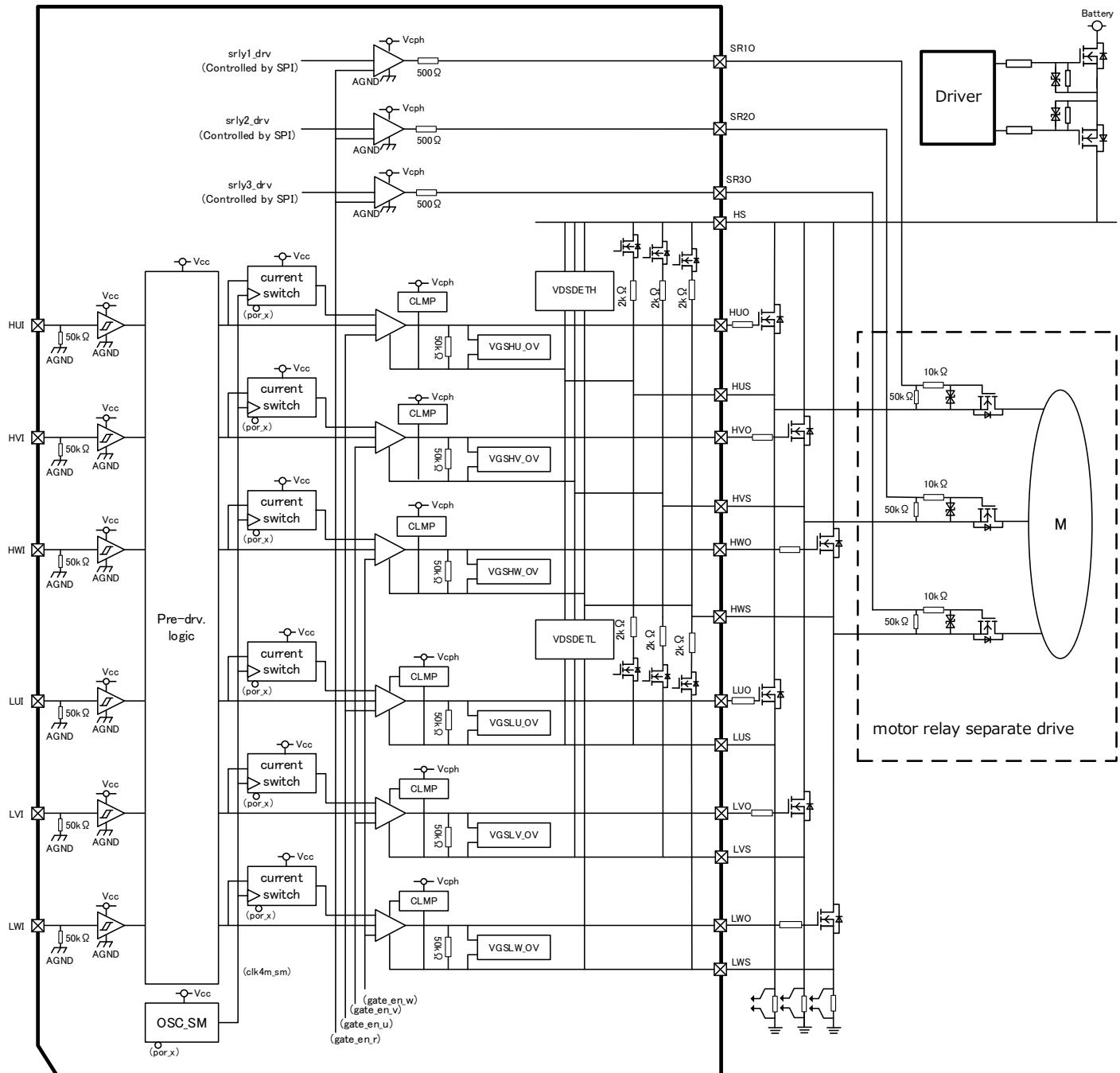

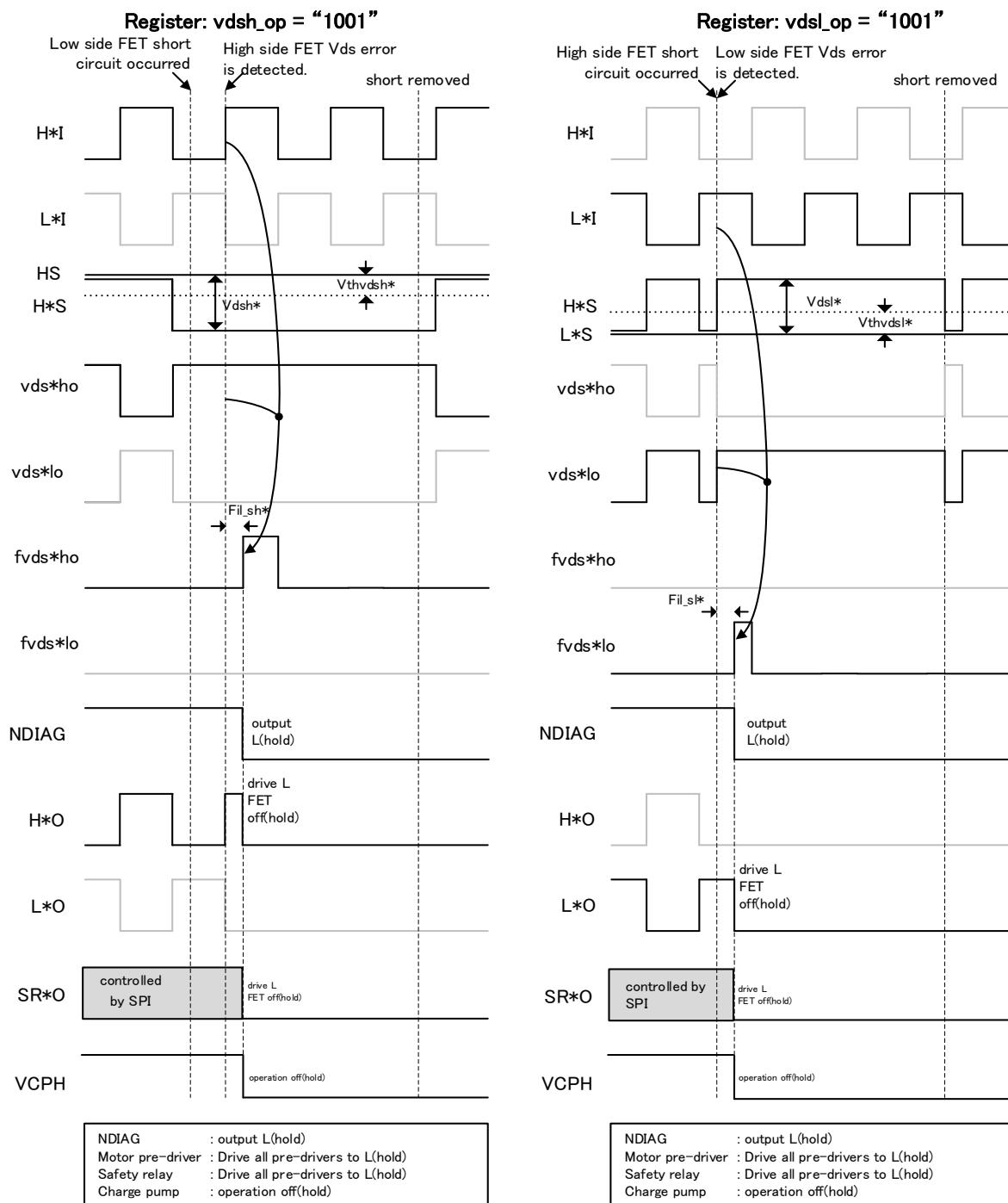

## 7.2. プリドライバー回路

プリドライバ回路はハイサイド駆動用、ローサイド駆動用、セーフティーリレー(電源リレーまたはモーターリレー)駆動用プリドライバ回路を有します。

ハイサイド駆動およびローサイド駆動用プリドライバー回路はそれぞれ入出力端子を持ち、各入力端子に入力された信号により制御します。

セーフティーリレー駆動用プリドライバ回路は CP\_RLY\_CTRL レジスターにより制御します。セーフティーリレー駆動用プリドライバ回路は  $500\Omega$  の抵抗および逆接続時の逆流防止用ダイオードを内蔵しています(Fig. 7.2-c)。モーターリレーにプルダウン抵抗を接続する場合は、ゲート抵抗との分圧に注意してください。セーフティーリレー出力 SR10, SR20, SR30 を電源リレーに使用する場合は外付けシリーズ抵抗値の制限はありません。

HUS, HVS, HWS 端子を中点電圧に保つための抵抗は 7.8 の初期診断を実行するときだけ接続されます。

Fig. 7.2-a プリドライバー回路ブロック図 (モーターリレー 一括駆動時)

Fig. 7.2-b プリドライバー回路ブロック図（モーターリレー個別駆動時）

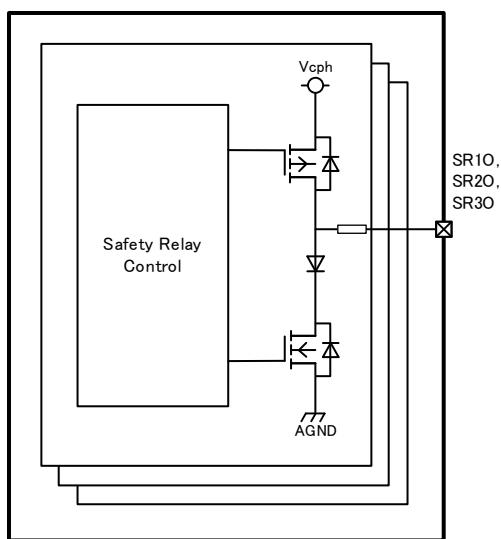

## &lt;セーフティーリレー(電源リレーまたはモーターリレー)駆動回路&gt;

セーフティーリレー駆動回路は電源リレーまたはモーターリレーを制御する回路です。セーフティーリレー用プリドライバ回路は [CP\\_RLY\\_CTRL](#) レジスターにより制御します。セーフティーリレー駆動用プリドライバー回路は  $500\Omega$  の抵抗および逆接続時の逆流防止用ダイオードを内蔵しています(Fig. 7.2-c)

真理値表を表 7.2-a に示します。真理値表内の内部信号(gate\_en\_r)の詳細は 7.6 を参照してください。

表 7.2-a 入出力真理値表 (セーフティーリレー駆動回路)

## ・電源リレーまたは、モーターリレー駆動回路 1 (SR1O)

| 内部信号        | 入力 (SPI)           | 出力   | 備考 |

|-------------|--------------------|------|----|

| (gate_en_r) | レジスター<br>srly1_drv | SR1O |    |

| “L”         | *                  | “L”  | —  |

| “H”         | “0”                | “L”  | —  |

|             | “1”                | “H”  | —  |

## ・電源リレーまたは、モーターリレー駆動回路 2 (SR2O)

| 内部信号        | 入力 (SPI)           | 出力   | 備考 |

|-------------|--------------------|------|----|

| (gate_en_r) | レジスター<br>srly2_drv | SR2O |    |

| “L”         | *                  | “L”  | —  |

| “H”         | “0”                | “L”  | —  |

|             | “1”                | “H”  | —  |

## ・電源タリレーまたは、モーターリレー駆動回路 3 (SR3O)

| 内部信号        | 入力 (SPI)           | 出力   | 備考 |

|-------------|--------------------|------|----|

| (gate_en_r) | レジスター<br>srly3_drv | SR3O |    |

| “L”         | *                  | “L”  | —  |

| “H”         | “0”                | “L”  | —  |

|             | “1”                | “H”  | —  |

\*:Don't care

Fig. 7.2-c セーフティーリレー回路ブロック図

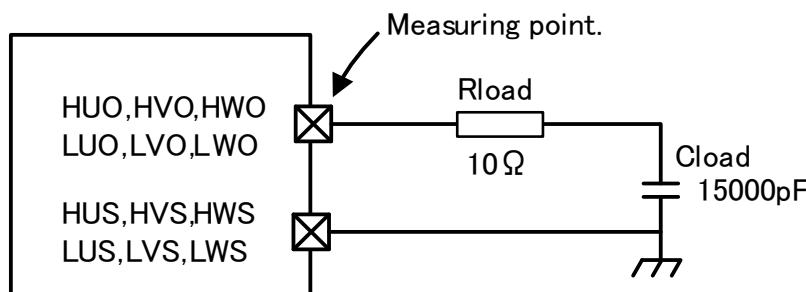

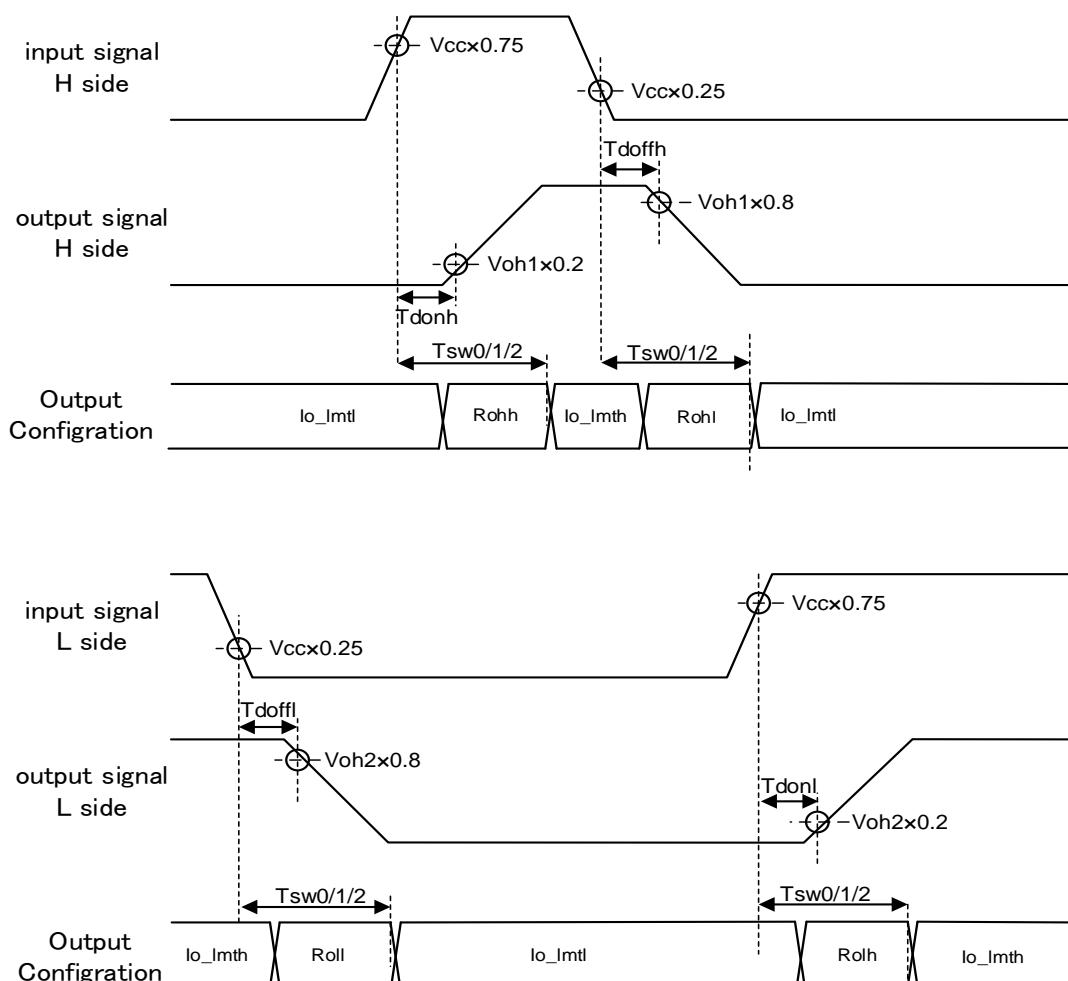

## &lt;ハイサイド駆動回路、ローサイド駆動回路&gt;

ハイサイド駆動回路はハイサイドの MOSFET を駆動する回路です。ローサイド駆動回路はローサイドの MOSFET を駆動する回路です。ハイサイド、ローサイド各 3ch 内蔵しています。入力信号(HUI/HVI/HWI, LUI/LVI/LWI)は制御ブロックで変換され、出力信号(HUO/HVO/HWO, LUO/LVO/LWO)を出力します。

➤ 電流制限機能

ハイサイド駆動およびローサイド駆動回路の Turn on/Turn off 時間後の電流は T\_IILIM レジスターの t\_ilim 設定に応じて電流制限(Io\_lmth/ Io\_lmtl)がかかります。レジスター:t\_ilim="11"の場合は電流制限無し(設定した定電流)となり、t\_ilim="00"~"10"の場合は設定した時間となります。

➤ 禁止入力機能

真理値表を表 7.2-b に示します。代表例として U 相について記載します。プリドライバーが有効な期間(gate\_en\_u="H")に HUI=LUI="H" となった場合の動作は、PL\_CTRL レジスターにより選択可能です。plu\_dis ビットが "L" の場合は入力禁止モードが有効であり、出力が HUO=LUO="L" として出力されます。この時 pl\_op によってステータスレジスターを "H" に設定するかどうかを選択できます。pl\_op が "H" に設定されている場合は err\_pl\_u に "H" をセットします。pl\_op="L" の場合は err\_pl\_u に "H" をセットしません。DIAG 端子はステータスレジスターに従います。また plu\_dis="H" に設定された場合は、禁止入力検出自体が無効となり、出力を HUO=LUO="H" することができます。真理値表内の内部信号(gate\_en\_u, gate\_en\_v, gate\_en\_w)の詳細は 7.6 を参照してください。

表 7.2-b 入出力真理値表 (ハイサイド、ローサイド駆動回路)

## ・MOSFET 駆動回路 1 (U 相)

| 内部信号<br>(gate_en_u) | 入力  |     | レジスター設定 |       | 出力  |     | status<br>err_pl_u | 備考              |

|---------------------|-----|-----|---------|-------|-----|-----|--------------------|-----------------|

|                     | HUI | LUI | plu_dis | pl_op | HUO | LUO |                    |                 |

| "L"                 | "L" | *   | *       | *     | "L" | "L" | —                  | —               |

|                     | *   | "L" | *       | *     |     |     | —                  | —               |

|                     | "H" | "H" | "L"     | "L"   |     |     | —                  | 禁止入力モード         |

|                     | "H" | "H" | "L"     | "H"   | "L" | "L" | "set"              | 禁止入力モード、ステータスあり |

|                     | "H" | "H" | "H"     | *     |     |     | —                  | 禁止入力モードを無効(U 相) |

|                     | "H" | "H" | "L"     | "L"   |     |     | —                  | —               |

| "H"                 | "L" | "H" | *       | *     | "L" | "H" | —                  | —               |

|                     | "L" | "H" | *       | *     | "L" | "L" | —                  | —               |

|                     | "H" | "L" | *       | *     | "H" | "L" | —                  | —               |

|                     | "H" | "H" | "L"     | "L"   | "L" | "L" | —                  | 禁止入力モード         |

|                     | "H" | "H" | "L"     | "H"   | "L" | "L" | "set"              | 禁止入力モード、ステータスあり |

|                     | "H" | "H" | "H"     | *     | "H" | "H" | —                  | 禁止入力モードを無効(U 相) |

## ・MOSFET 駆動回路 2 (V 相)

| 内部信号        | 入力  |     | レジスター設定 |       | 出力  |     | status | 備考              |

|-------------|-----|-----|---------|-------|-----|-----|--------|-----------------|

| (gate_en_v) | HVI | LVI | plv_dis | pl_op | HVO | LVO |        |                 |

| “L”         | “L” | *   | *       | *     | “L” | “L” | —      | —               |

|             | *   | “L” | *       | *     |     |     | —      | —               |

|             | “H” | “H” | “L”     | “L”   |     |     | —      | 禁止入力モード         |

|             |     |     | “L”     | “H”   |     |     | “set”  | 禁止入力モード、ステータスあり |

|             |     |     | “H”     | *     |     |     | —      | 禁止入力モードを無効(V 相) |

| “H”         | “L” | “L” | *       | *     | “L” | “L” | —      | —               |

|             | “L” | “H” | *       | *     | “L” | “H” | —      | —               |

|             | “H” | “L” | *       | *     | “H” | “L” | —      | —               |

|             | “H” | “H” | “L”     | “L”   | “L” | “L” | —      | 禁止入力モード         |

|             |     |     | “L”     | “H”   | “L” | “L” | “set”  | 禁止入力モード、ステータスあり |

|             |     |     | “H”     | *     | “H” | “H” | —      | 禁止入力モードを無効(V 相) |

## ・MOSFET 駆動回路 3 (W 相)

| 内部信号        | 入力  |     | レジスター設定 |       | 出力  |     | status   | 備考              |

|-------------|-----|-----|---------|-------|-----|-----|----------|-----------------|

| (gate_en_w) | HWI | LWI | plw_dis | pl_op | HWO | LWO | err_pl_w |                 |

| “L”         | “L” | *   | *       | *     | “L” | “L” | —        | —               |

|             | *   | “L” | *       | *     |     |     | —        | —               |

|             | “H” | “H” | “L”     | “L”   |     |     | —        | 禁止入力モード         |

|             |     |     | “L”     | “H”   |     |     | “set”    | 禁止入力モード、ステータスあり |

|             |     |     | “H”     | *     |     |     | —        | 禁止入力モードを無効(W 相) |

| “H”         | “L” | “L” | *       | *     | “L” | “L” | —        | —               |

|             | “L” | “H” | *       | *     | “L” | “H” | —        | —               |

|             | “H” | “L” | *       | *     | “H” | “L” | —        | —               |

|             | “H” | “H” | “L”     | “L”   | “L” | “L” | —        | 禁止入力モード         |

|             |     |     | “L”     | “H”   | “L” | “L” | “set”    | 禁止入力モード、ステータスあり |

|             |     |     | “H”     | *     | “H” | “H” | —        | 禁止入力モードを無効(W 相) |

・ \*:Don't care

・ DIAG 端子はステータスに連動します。ステータスのクリアは err\_pl\_\*\_cl ビットを設定することで行います。

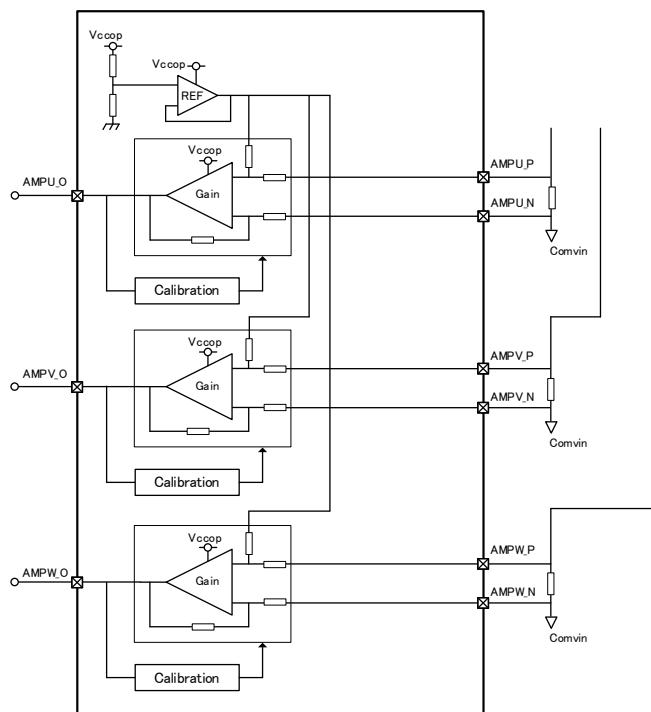

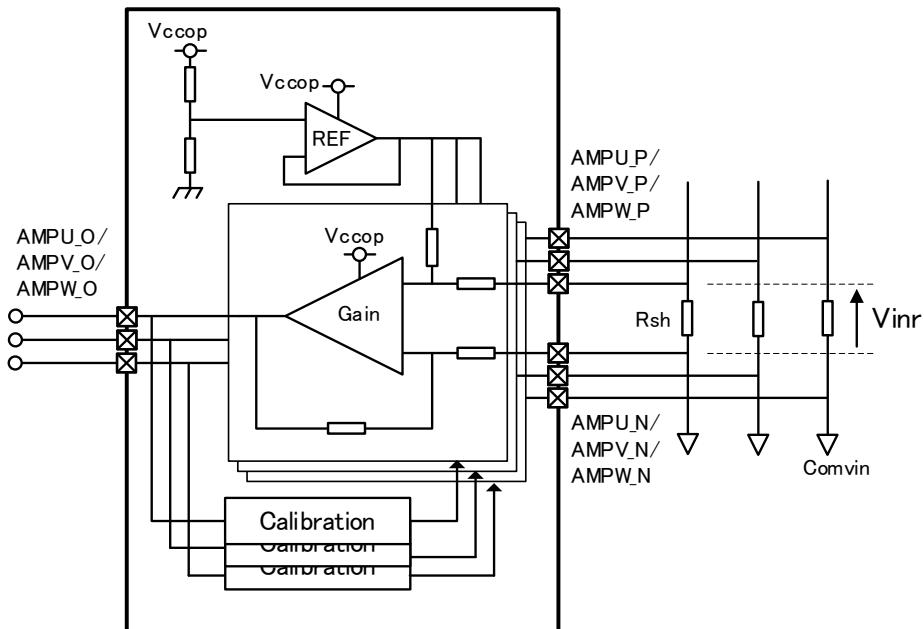

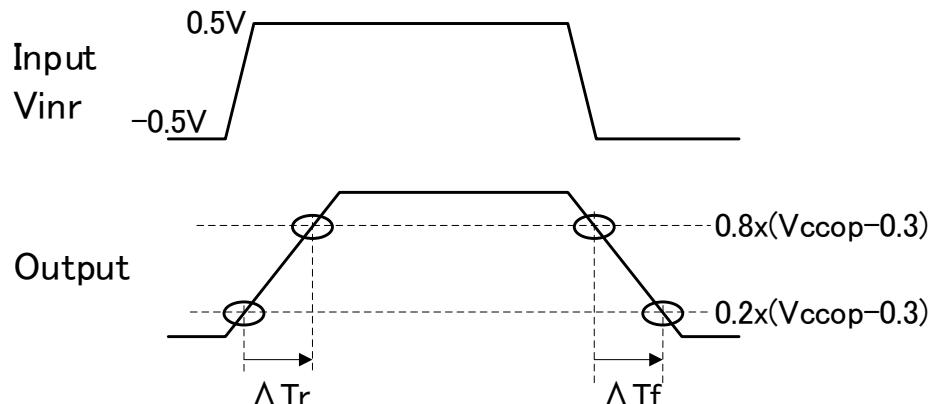

## 7.3. 電流検出回路

### 7.3.1. 構成

モーター電流検出用アンプを3つ、基準電圧生成用アンプを1つ内蔵しています(Fig7-3-a, Fig7-3-b)。モーター電流検出用アンプはモーター駆動部に接続されているシャント抵抗を流れる電流により生じる差電圧を増幅して出力することができます。基準電圧生成用アンプは基準電圧生成用のバッファーアンプとして用います。電流検出の外部構成として、1シャント構成と3シャント構成のどちらにも対応可能です。

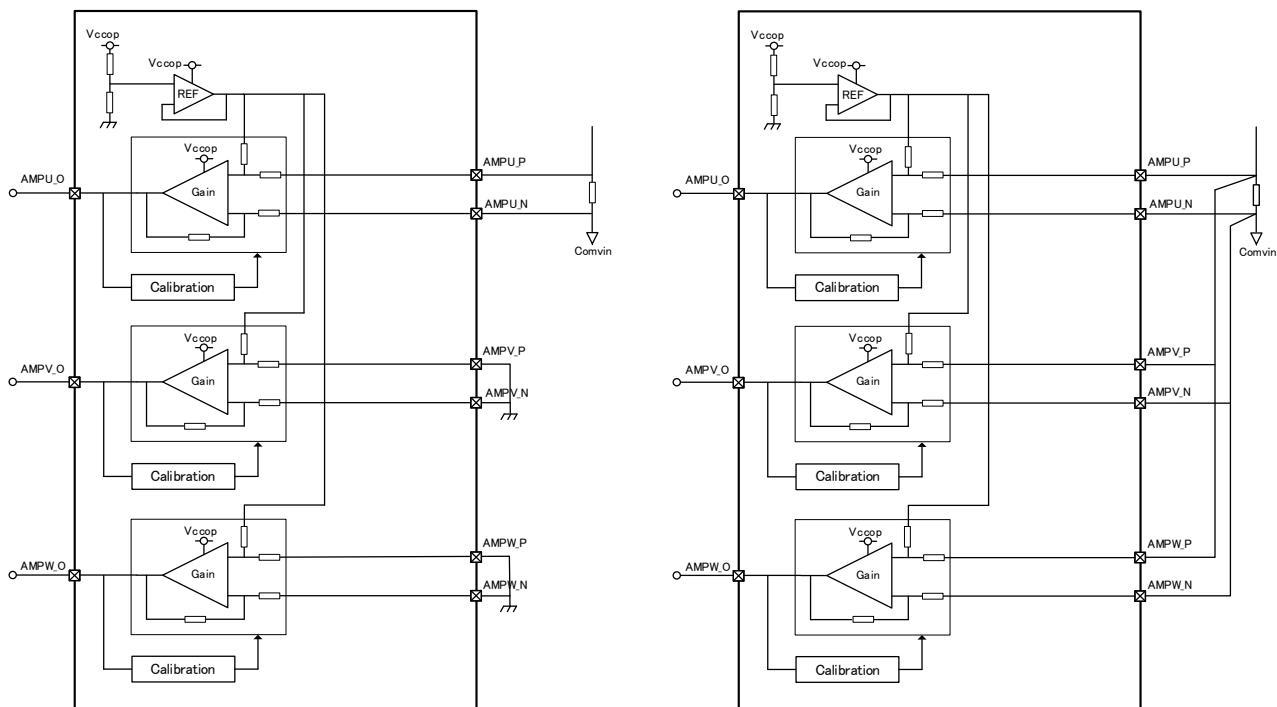

Fig. 7.3-a モーター電流検出回路ブロック図 (3 シャント構成)

Fig. 7.3-b モーター電流検出回路ブロック図 (1 シャント構成)

### 7.3.2. オフセットキャリブレーション

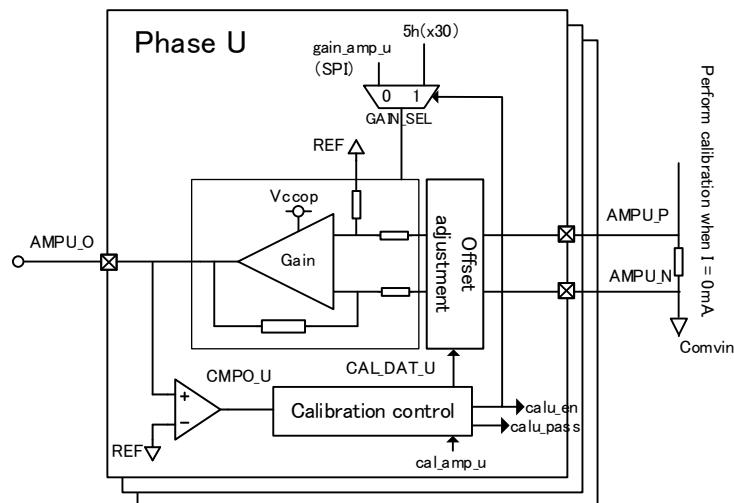

AMP\_CTRL レジスター:cal\_amp\_\*(\*はu/v/w)に“1”を書き込むと、電流検出アンプのオフセットキャリブレーションを実行します。キャリブレーションの実行は入力差電圧が同電位(0V)のときに行ってください。入力差電圧がある場合は正しくキャリブレーションが実行されません。ブロック図を Fig. 7.3-c に示します。cal\_amp\_\*を設定することでオフセットキャリブレーションがスタートし AMP\_STAT の cal\_en="H" となります。調整中は GAIN\_SEL=5h(27.4倍)に固定されます。CAL\_DAT\_\*

Fig. 7.3-c オフセットキャリブレーションブロック図

を変化させながらアンプ出力を REF と比較することにより、オフセット補正值を探査します。調整が完了すると cal\_en="L" となり調整後の結果の妥当性を判断して cal\*\_pass にセットします。cal\*\_pass="H" となった場合は結果がそのまま保持され調整値として使用されます。cal\*\_pass="L" となった場合は調整結果が破棄されリセット時のデフォルト値に戻ります。

AMP\_CTRL レジスターの cal\_amp\_\* のビットが複数同時に設定された場合は、設定された相に対するオフセットキャリブレーションを同時に実行します。AMP\_STAT の cal\_en="L" となりキャリブレーションが終了した時点で cal\*\_pass が設定さ

Fig. 7.3-d オフセットキャリブレーションの実行

れますが、AMP\_STAT CLR レジスターの cal\*\_pass\_cl ビットに 1 をライトすることによりステータスを任意のタイミングでクリアすることができます。また、cal\*\_pass は対応する相のキャリブレーションが開始されたときに自動的に”L”にクリアされます。cal\_en が”H”の期間はキャリブレーション実行中であるため、この期間で cal\_amp\_\*を設定しても破棄されます。

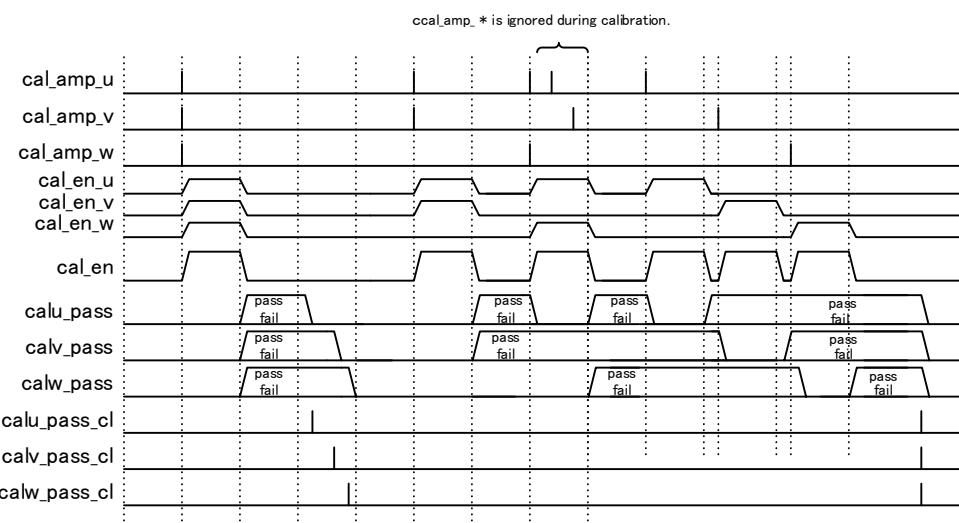

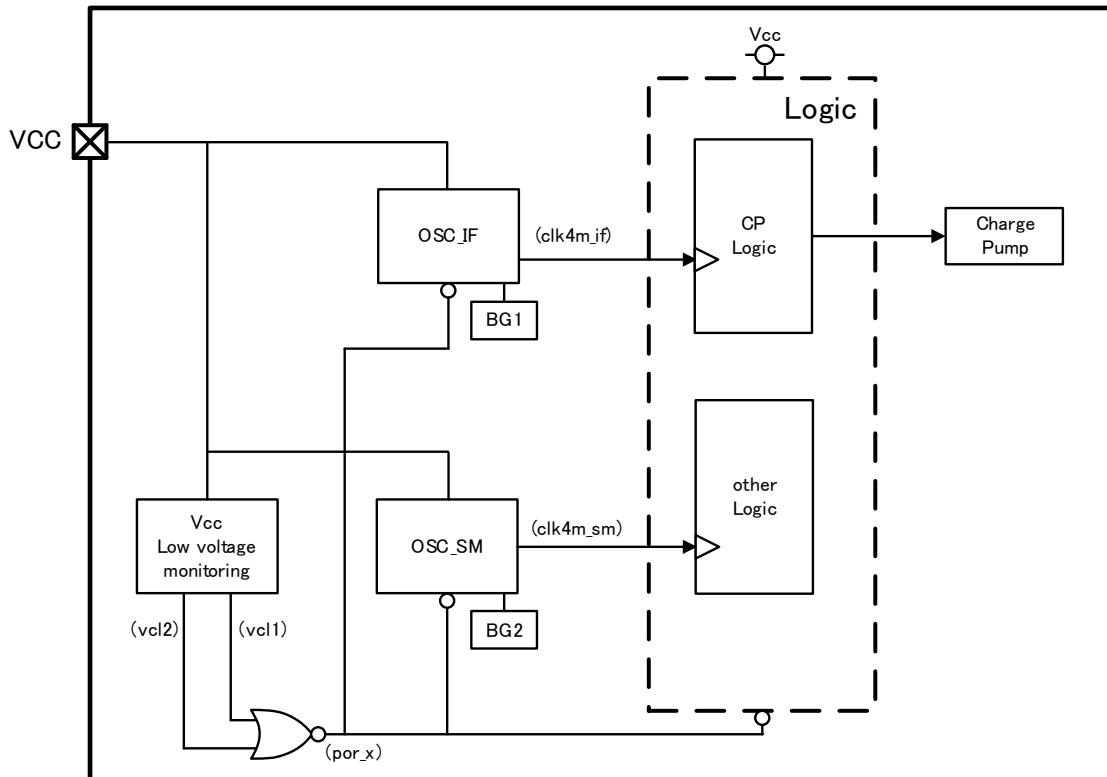

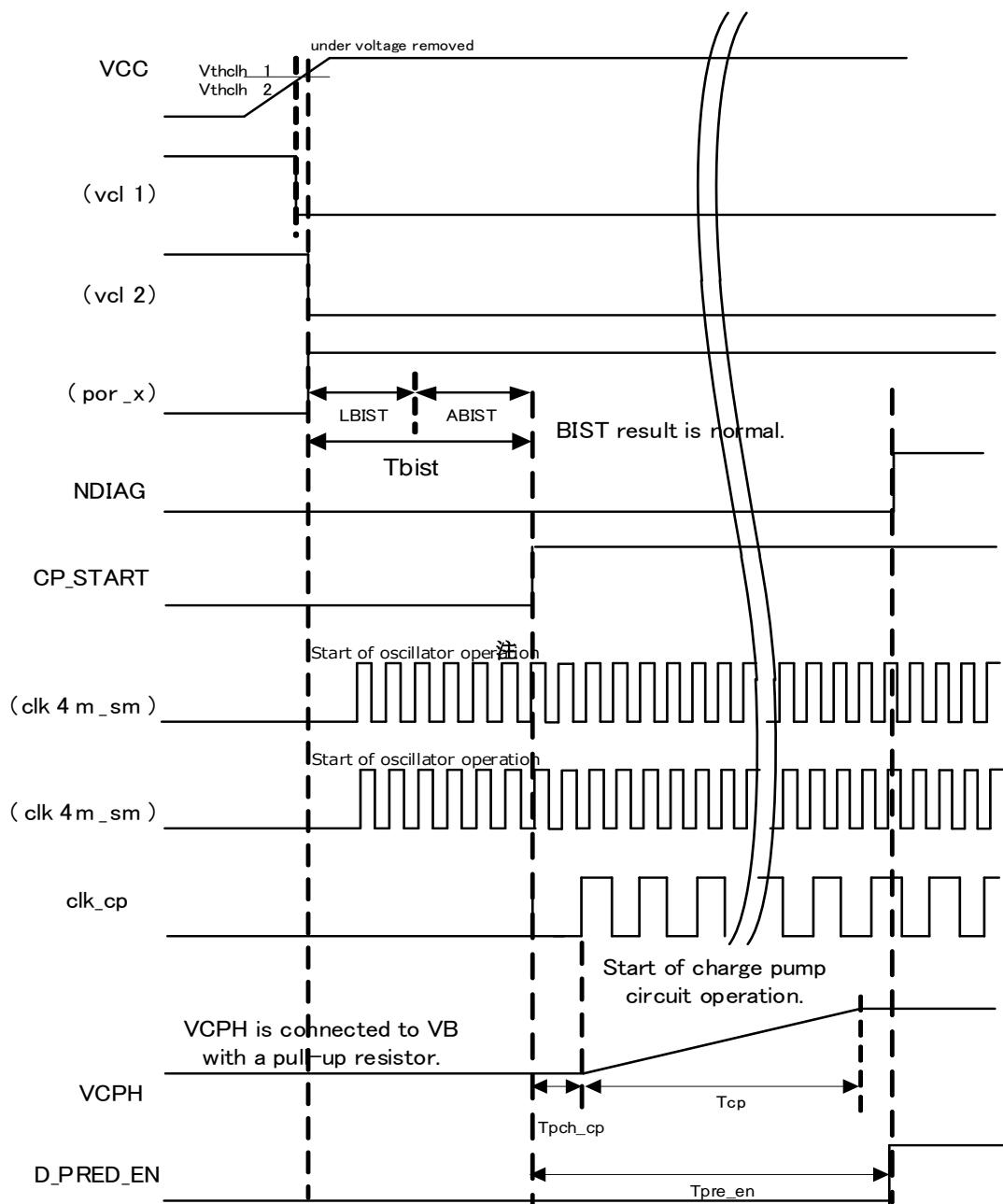

## 7.4. 発振回路

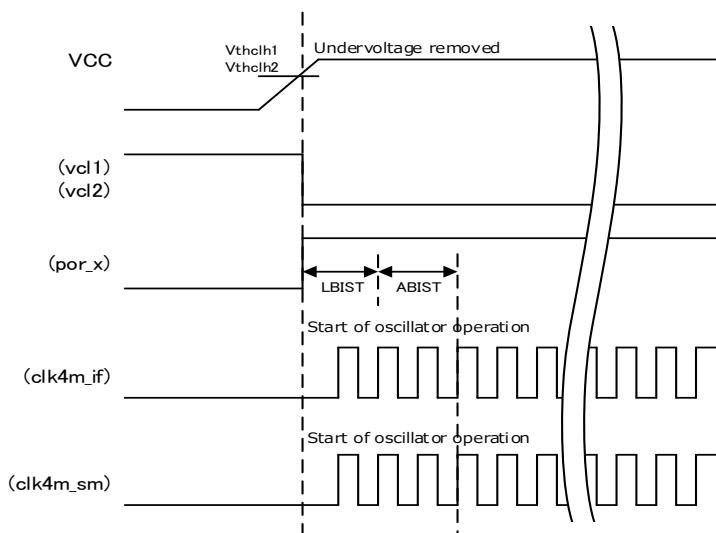

発振回路を2つ内蔵しています。OSC\_IFはチャージポンプ用、OSC\_SMはシステムクロック/監視/SPI用です。発振回路はCR内蔵構成となっており、発振周波数はおのおの 4MHz(typ.)です。発振回路は内部信号(por\_x)解除後に動作を開始します。2つの発振器に使用する基準電圧源(BG1,BG2)は各々別系統のものを使用します。

Fig. 7.4-a 発振回路ブロック図

Fig. 7.4-b 発振回路タイミングチャート

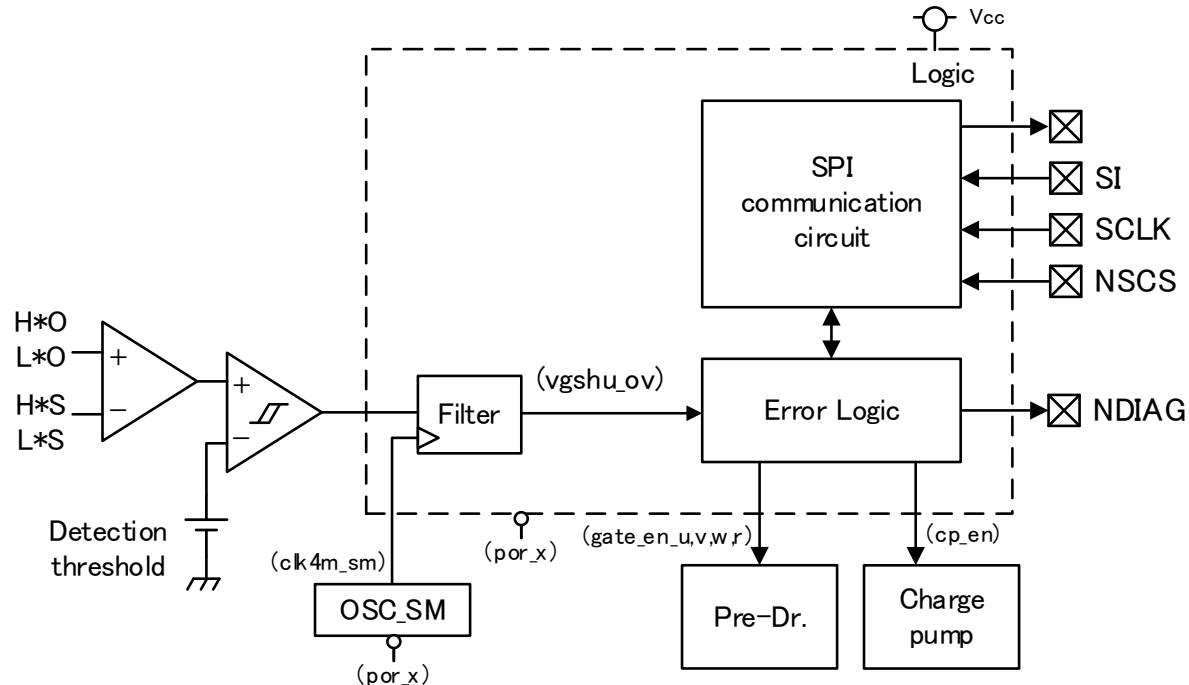

## 7.5. 異常検出回路

低電圧(VB, VCC, VCC\_OP) / 高電圧(VCPh, VCC, VCC\_OP, 外部 MOSFET の VGS) / 過熱 / 外部 MOSFET の VDS / 周波数異常検出機能を内蔵しています。監視機能一覧および内部信号の内容について以下に示します。動作詳細は 7.5.1 以降を参考してください。異常検出してプリドライバー回路がオフする場合、外部 MOSFET の VDS 検出機能が無効となります。その後、異常から復帰しプリドライバー回路が動作可能になると、外部 MOSFET の VDS 検出機能は再び有効になります。

表 7.5-a 監視機能一覧

| 監視機能                   | 設定 Reg.   | 設定 bit | 検出時動作<br>注 4,5,6,7                        | 初期値 | BI ST<br>注 8 | Status Reg.<br>注 2 | Status Clear<br>注 1 | NDI AG<br>注 3 |

|------------------------|-----------|--------|-------------------------------------------|-----|--------------|--------------------|---------------------|---------------|

| VCC 低電圧 1<br>VCC 低電圧 2 | 無         | —      | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ、発振回路オフ  | —   | —            | —                  | —                   | “L”           |

| VB 低電圧                 | uvb_op    | “000”  | 全ての(9ch)プリドライバー回路オフ                       | —   | A            | uvb                | uvb_cl              | “L”           |

|                        |           | “001”  | 全ての(9ch)プリドライバー回路オフ                       | ○   |              |                    | —                   | “L”           |

|                        |           | “010”  | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                    | —                   | “H”           |

|                        |           | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | uvb_cl              | “L”           |

|                        |           | “100”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “L”           |

|                        |           | “101”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “H”           |

| VCPh 高電圧               | ocph_op   | “000”  | 検出無効                                      | ○   | A            | ocph               | —                   | “H”           |

|                        |           | “001”  | 動作継続                                      | —   |              |                    | —                   | “H”           |

|                        |           | “010”  | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                    | ocph_cl             | “L”           |

|                        |           | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “L”           |

|                        |           | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                    | —                   | “L”           |

|                        |           | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                    | —                   | “H”           |

| VCC 高電圧                | ovc_op    | “000”  | 検出無効                                      | —   | A            | ovcc               | —                   | “H”           |

|                        |           | “001”  | 動作継続                                      | —   |              |                    | —                   | “H”           |

|                        |           | “010”  | 全ての(9ch)プリドライバー回路オフ                       | ○   |              |                    | ovcc_cl             | “L”           |

|                        |           | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “L”           |

|                        |           | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                    | —                   | “L”           |

|                        |           | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                    | —                   | “H”           |

| VCC_OP 低電圧             | uvccop_op | “000”  | 検出無効                                      | ○   | A            | uvccop             | —                   | “H”           |

|                        |           | “001”  | 動作継続                                      | —   |              |                    | —                   | “H”           |

|                        |           | “010”  | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                    | uvccop_cl           | “L”           |

|                        |           | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “L”           |

|                        |           | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                    | —                   | “L”           |

|                        |           | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                    | —                   | “H”           |

| VCC_OP 高電圧             | ovccop_op | “000”  | 検出無効                                      | ○   | A            | ovccop             | —                   | “H”           |

|                        |           | “001”  | 動作継続                                      | —   |              |                    | —                   | “H”           |

|                        |           | “010”  | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                    | ovccop_cl           | “L”           |

|                        |           | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                    | —                   | “L”           |

|                        |           | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                    | —                   | “L”           |

|                        |           | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                    | —                   | “H”           |

| 監視機能                                | 設定Reg       | 設定bit  | 検出時動作<br>注 4,5,6,7                        | 初期値 | BIS T<br>注 8 | Status Reg.<br>注 2                                       | Status Clear<br>注 1                                                        | NDI AG<br>注 3 |

|-------------------------------------|-------------|--------|-------------------------------------------|-----|--------------|----------------------------------------------------------|----------------------------------------------------------------------------|---------------|

| 過熱                                  | tsd_op      | “000”  | 検出無効                                      | —   | A            | —                                                        | —                                                                          | “H”           |

|                                     |             | “001”  | 動作継続                                      | —   |              | tsd                                                      | tsd_cl                                                                     | “L”           |

|                                     |             | “010”  | 全ての(9ch)プリドライバー回路オフ                       | ○   |              |                                                          |                                                                            |               |

|                                     |             | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                                                          |                                                                            |               |

|                                     |             | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                                                          |                                                                            |               |

|                                     |             | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                                                          |                                                                            |               |

| ALARM                               | alr_op      | “0”    | 全ての(9ch)プリドライバー回路オフ                       | ○   | —            | alm_de<br>t                                              | —                                                                          | “L”           |

|                                     |             | “1”    | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                                                          |                                                                            |               |

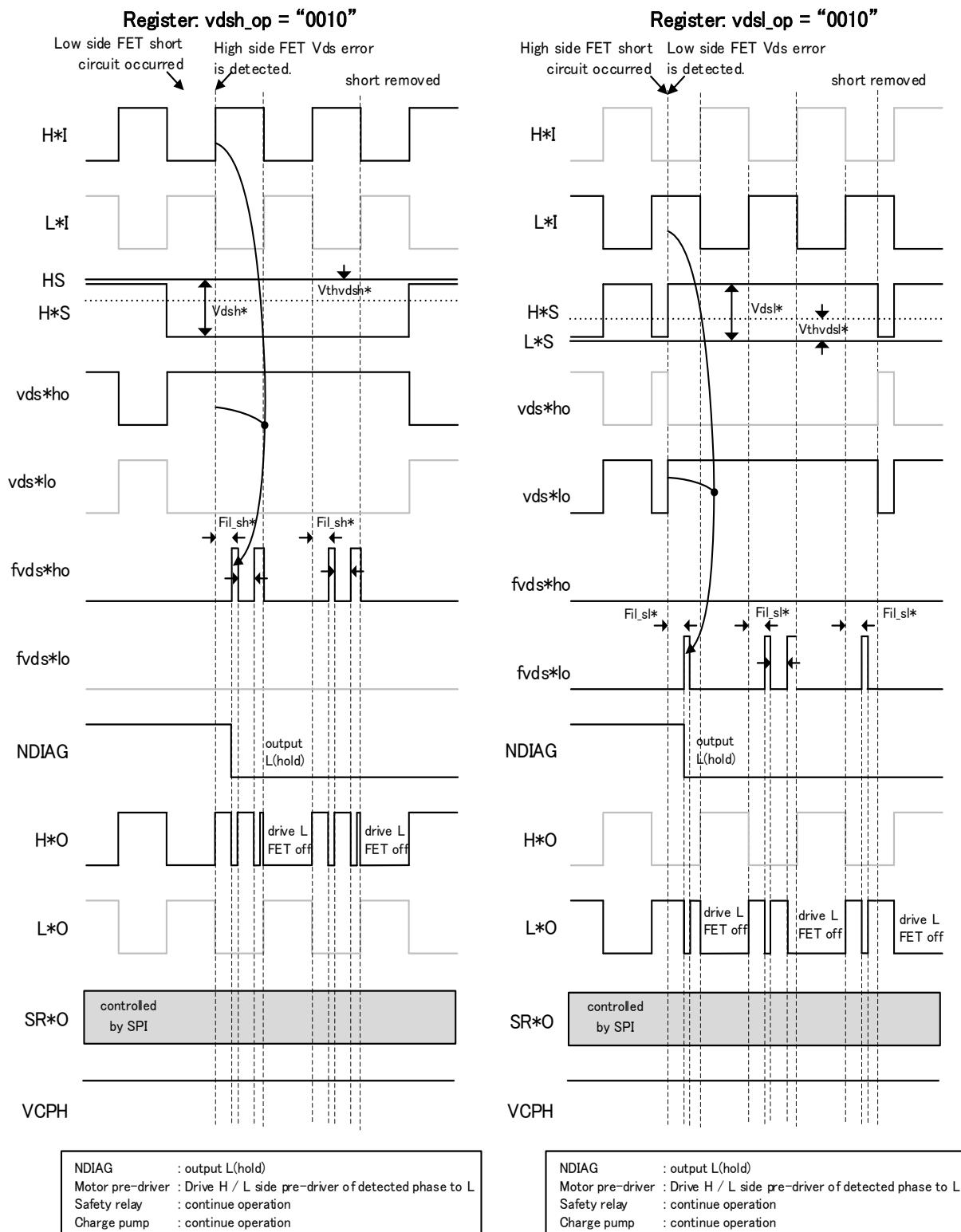

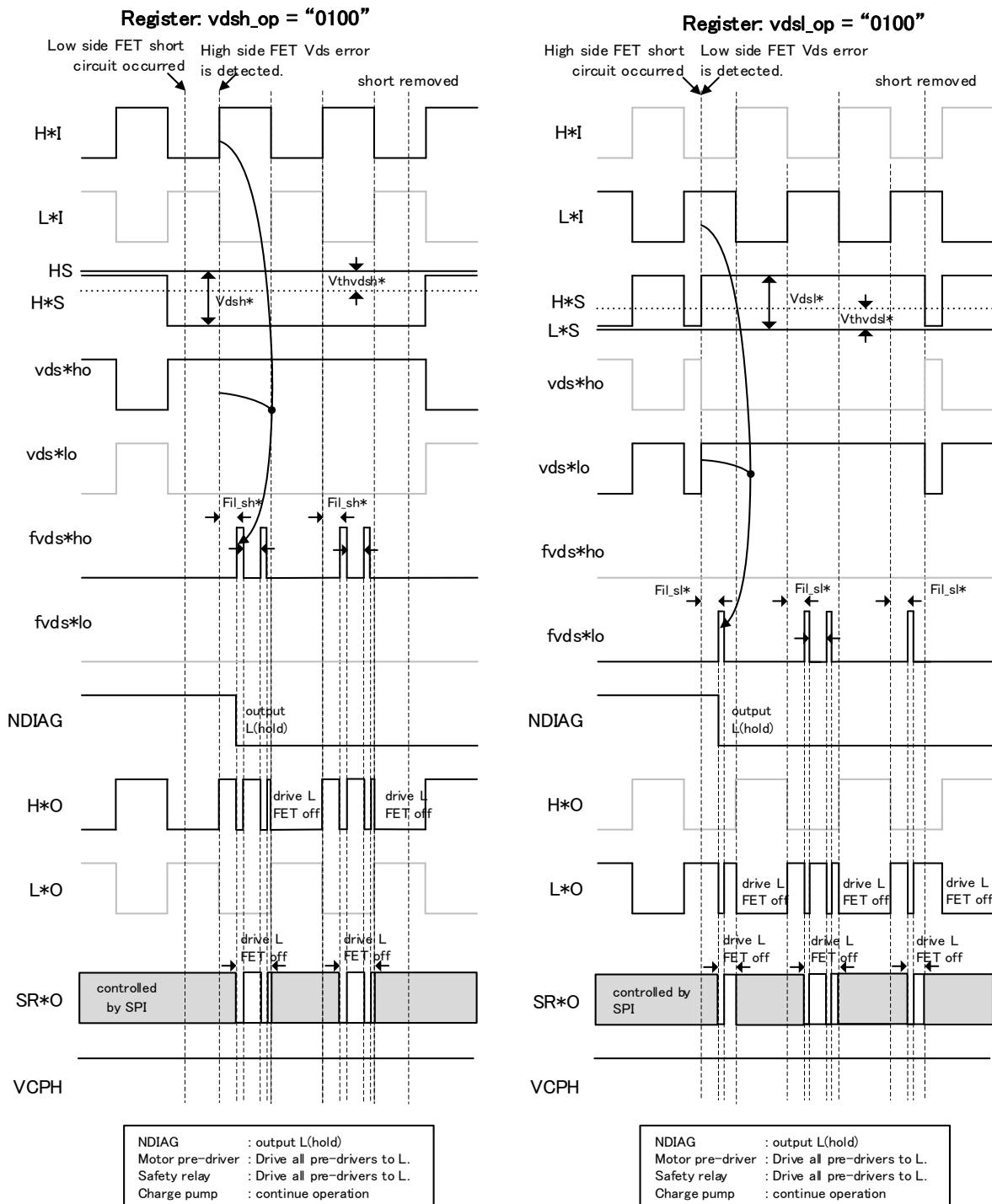

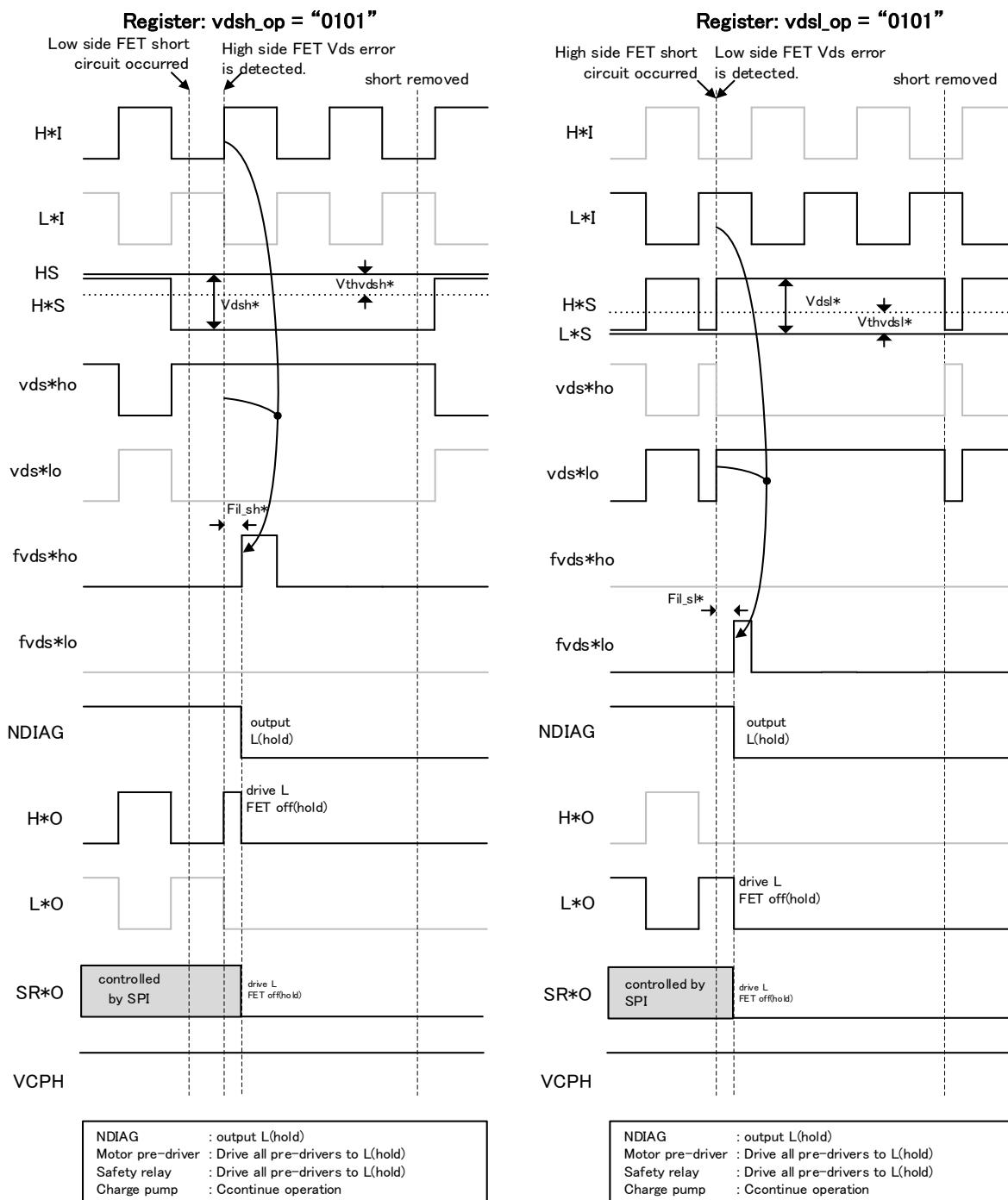

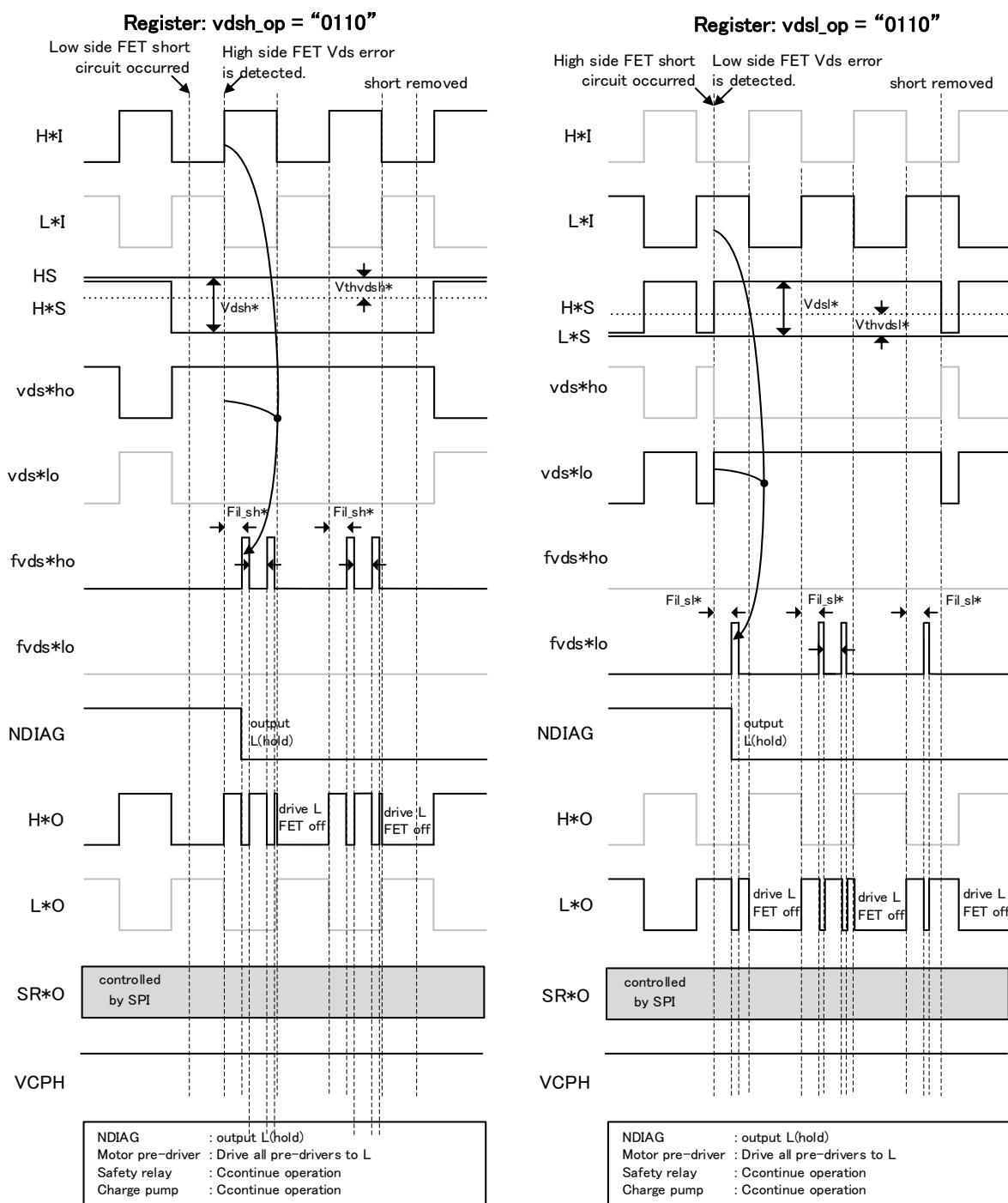

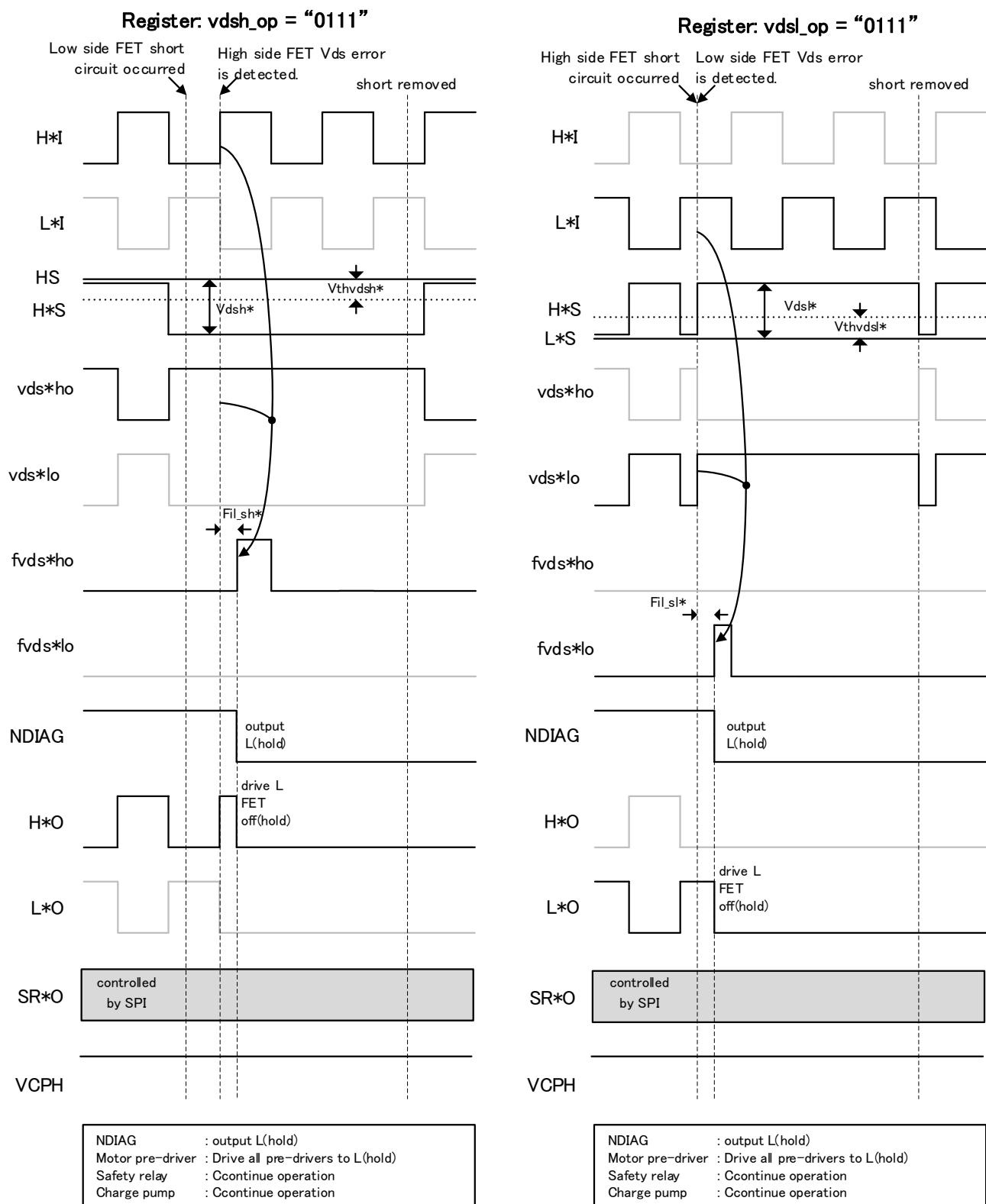

| 外部<br>MOSFET<br>のVds<br>(ハイサイ<br>ド) | vdsh<br>_op | “0000” | 検出無効                                      | —   | —            | —                                                        | —                                                                          | “H”           |

|                                     |             | “0001” | 動作継続                                      | —   |              | vds_uh<br>vds_vh<br>vds_wh                               | vds_uh_cl<br>vds_vh_cl<br>vds_wh_cl                                        | “L”           |

|                                     |             | “0010” | 検出した相のH/Lプリドライバー回路オフ                      | —   |              |                                                          |                                                                            |               |

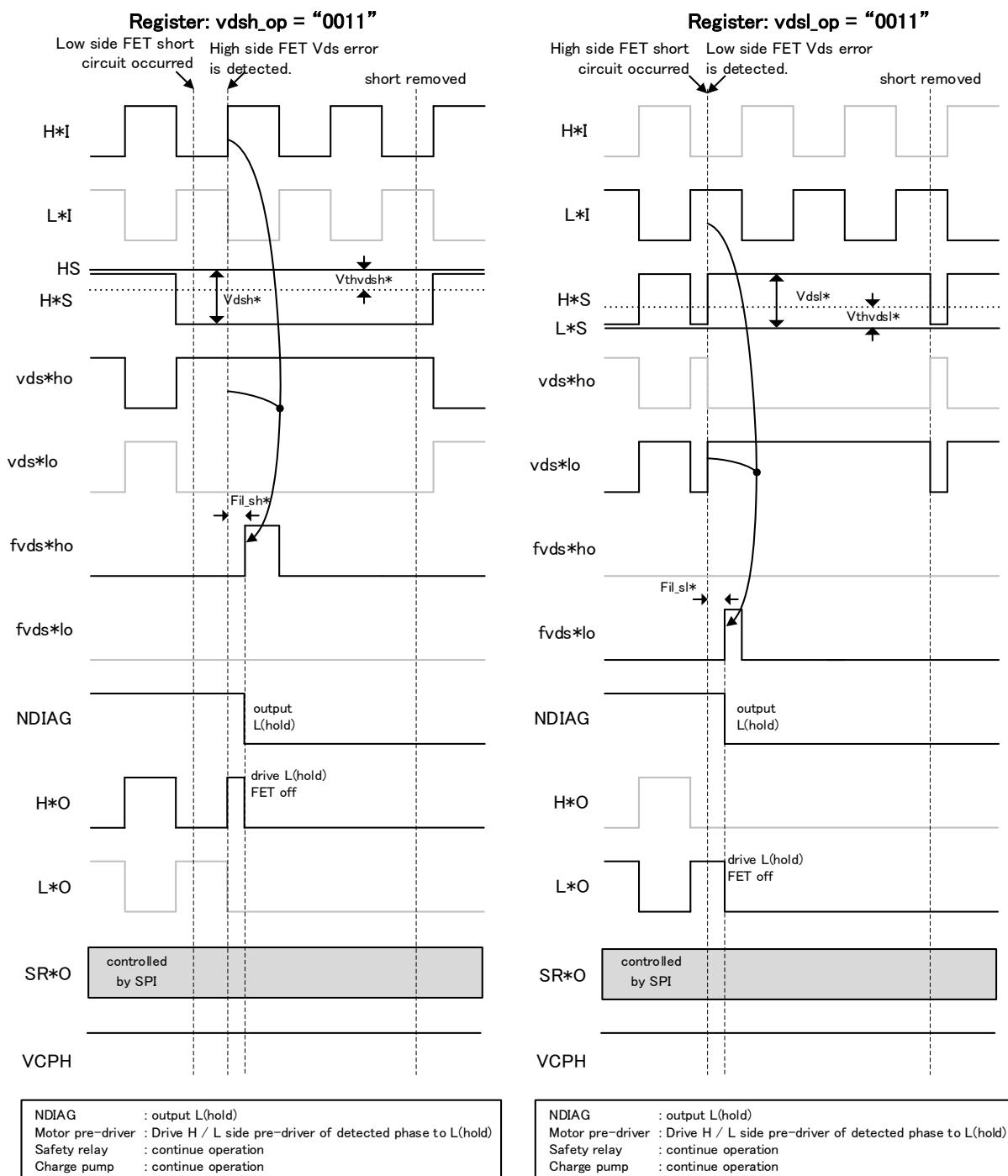

|                                     |             | “0011” | 検出した相のH/Lプリドライバー回路オフ(保<br>持)              | —   |              |                                                          |                                                                            |               |

|                                     |             | “0100” | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                                                          |                                                                            |               |

|                                     |             | “0101” | 全ての(9ch)プリドライバー回路オフ(保持)                   | —   |              |                                                          |                                                                            |               |

|                                     |             | “0110” | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                                                          |                                                                            |               |

|                                     |             | “0111” | モーター駆動(6ch)プリドライバー回路オフ<br>(保持)            | ○   |              |                                                          |                                                                            |               |

|                                     |             | “1000” | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                                                          |                                                                            |               |

|                                     |             | “1001” | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                                                          |                                                                            |               |

| 外部<br>MOSFET<br>のVds<br>(ローサイ<br>ド) | vdsl<br>_op | “0000” | 検出無効                                      | —   | —            | —                                                        | —                                                                          | “H”           |

|                                     |             | “0001” | 動作継続                                      | —   |              | vds_ul<br>vds_vl<br>vds_wl                               | vds_ul_cl<br>vds_vl_cl<br>vds_wl_cl                                        | “L”           |

|                                     |             | “0010” | 検出した相のH/Lプリドライバー回路オフ                      | —   |              |                                                          |                                                                            |               |

|                                     |             | “0011” | 検出した相のH/Lプリドライバー回路オフ(保<br>持)              | —   |              |                                                          |                                                                            |               |

|                                     |             | “0100” | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                                                          |                                                                            |               |

|                                     |             | “0101” | 全ての(9ch)プリドライバー回路オフ(保持)                   | —   |              |                                                          |                                                                            |               |

|                                     |             | “0110” | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                                                          |                                                                            |               |

|                                     |             | “0111” | モーター駆動(6ch)プリドライバー回路オフ<br>(保持)            | ○   |              |                                                          |                                                                            |               |

|                                     |             | “1000” | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                                                          |                                                                            |               |

|                                     |             | “1001” | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | —   |              |                                                          |                                                                            |               |

| 外部<br>MOSFET<br>Vgs 過電<br>圧         | vgs_op      | “000”  | 検出無効                                      | —   | A            | —                                                        | —                                                                          | “H”           |

|                                     |             | “001”  | 動作継続                                      | —   |              | vgs_uh<br>vgs_ul<br>vgs_vh<br>vgs_vl<br>vgs_wh<br>vgs_wl | vgs_uh_cl<br>vgs_ul_cl<br>vgs_vh_cl<br>vgs_vl_cl<br>vgs_wh_cl<br>vgs_wl_cl | “L”           |

|                                     |             | “010”  | 全ての(9ch)プリドライバー回路オフ                       | —   |              |                                                          |                                                                            |               |

|                                     |             | “011”  | モーター駆動(6ch)プリドライバー回路オフ                    | —   |              |                                                          |                                                                            |               |

|                                     |             | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ         | —   |              |                                                          |                                                                            |               |

|                                     |             | “101”  | 全ての(9ch)プリドライバー回路オフ(保持)、<br>チャージポンプオフ(保持) | ○   |              |                                                          |                                                                            |               |

| 監視機能                | 設定 Reg. | 設定 bit | 検出時動作<br>注 4,5,6,7                            | 初期値 | BIS T<br>注 8 | Status Reg.<br>注 2               | Status Clear<br>注 1                       | NDI AG<br>注 3 |

|---------------------|---------|--------|-----------------------------------------------|-----|--------------|----------------------------------|-------------------------------------------|---------------|

| 周波数異常<br>注 9        | ferr_op | “000”  | 検出無効                                          | ○   | L            | err_of<br>err_uf                 | err_of_cl<br>err_uf_cl                    | “H”<br>“L”    |

|                     |         | “001”  | 動作継続                                          | —   |              |                                  |                                           |               |

|                     |         | “010”  | 全ての(9ch)プリドライバー回路オフ                           | —   |              |                                  |                                           |               |

|                     |         | “011”  | モーター駆動(6ch)プリドライバー回路オフ                        | —   |              |                                  |                                           |               |

|                     |         | “100”  | 全ての(9ch)プリドライバー回路オフ、<br>チャージポンプオフ             | —   |              |                                  |                                           |               |

|                     |         | “101”  | 全ての(9ch)プリドライバー回路オフ<br>(保持)、<br>チャージポンプオフ(保持) | —   |              |                                  |                                           |               |

| プリドライバ<br>ー<br>禁止入力 | pl_op   | “0”    | 禁止入力時に検出相のプリドライバー<br>オフ                       | ○   |              |                                  |                                           |               |

|                     |         | “1”    | 禁止入力時に検出相のプリドライバー<br>オフ                       | —   |              | err_pl_u<br>err_pl_v<br>err_pl_w | err_pl_u_cl<br>err_pl_v_cl<br>err_pl_w_cl | “H”<br>“L”    |

| SPI 通信異常            | 無       | —      | 動作継続                                          | —   | —            |                                  |                                           |               |

| QA 演算               | qat_op  | “001”  | 動作継続                                          | ○   | L            | err_qac                          | err_qac_cl                                | “L”           |

|                     |         | “010”  | 全ての(9ch)プリドライバー回路オフ<br>(保持)                   | —   |              |                                  |                                           |               |

|                     |         | “011”  | モーター駆動(6ch)プリドライバー回<br>路オフ(保持)                | —   |              |                                  |                                           |               |

|                     |         | “100”  | 全ての(9ch)プリドライバー回路オフ<br>(保持)、<br>チャージポンプオフ(保持) | —   |              |                                  |                                           |               |

注1) Status Clear の列にステータスクリアビットが記載されている動作モードでは、異常検出によってステータスピットが一度セットされるとステータスピットは保持されます。保持されたステータスピットをクリアする場合は、該当するステータスクリアビットに 1 を書き込んでください。異常検出回路が異常を検出している間は、保持されているステータスレジスターをクリアすることはできません。Status Clear の列にステータスクリアビットが記載されていない動作モードでは、異常検出が解消されるとステータスピットがクリアされます。

注2) Status Reg の列に“—”が記載されている動作モードでは、ステータスレジスターに値はセットされません。

注3) NDIAG の列に“H”と記載のある動作モードでは、異常を検出しても NDIAG 端子は“L”になりません。NDIAG の列に“L”と記載のある動作モードでは、NDIAG 端子はステータスレジスターに従います(VCC 低電圧検出以外)。ステータスレジスターが保持されている期間 NDIAG=“L”を出力し、全てのステータスレジスターがクリアされると NDIAG=“H”に復帰します。ステータスレジスターが保持されない動作モードでは、ステータスレジスターをクリアしなくても異常検出が解消されると NDIAG=“H”に復帰します。

注4) 検出時動作の列に(保持)と記載のある動作モードでは、保持されたステータスレジスターによって動作が決まります。異常検出時に通常動作へ復帰させるためには、該当するステータスレジスターをクリアしてください。検出時動作に(保持)と記載の無い動作モードでは、ステータスレジスターをクリアしなくても異常検出が解消されると通常の動作に復帰します。

注5) 各監視機能に対する設定レジスター\*\*\*\*\_op の値はいつでも変更することが可能ですが、監視機能に対応するステータスレジスターが異常を検出したことを示している間は\*\*\*\*\_op の設定は実際の動作に反映されません。

注6) チャージポンプのオフは CP\_SW オフと CP ドライバーが停止します。

注7) 全ての(9ch)プリドライバー回路オフは、セーフティーリレーを含め外部 FET がオフとなるようにプリドライバーを“L”に駆動します。モーター駆動(6ch)プリドライバー回路オフは、セーフティーリレーを除く外部 FET がオフとなるようにプリドライバーを“L”に駆動します。検出した相の H/L(2ch)プリドライバー回路オフは、検出相ハイサイド、ローサイドプリドライバーがオフとなるようにプリドライバーを“L”に駆動します。

注8) A:ABIST、L:LBIST

注9) OSC\_SM のクロックが消失した場合は、検出時動作を実行させることは可能ですが、NDIAG は“L”になりません。

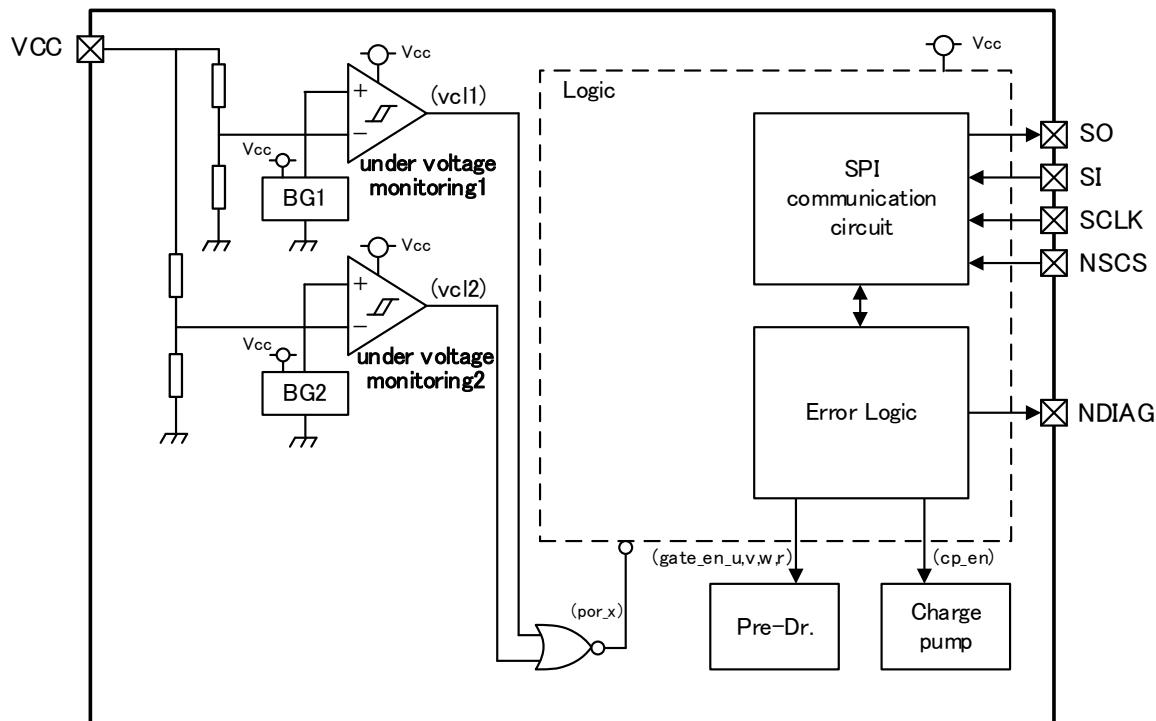

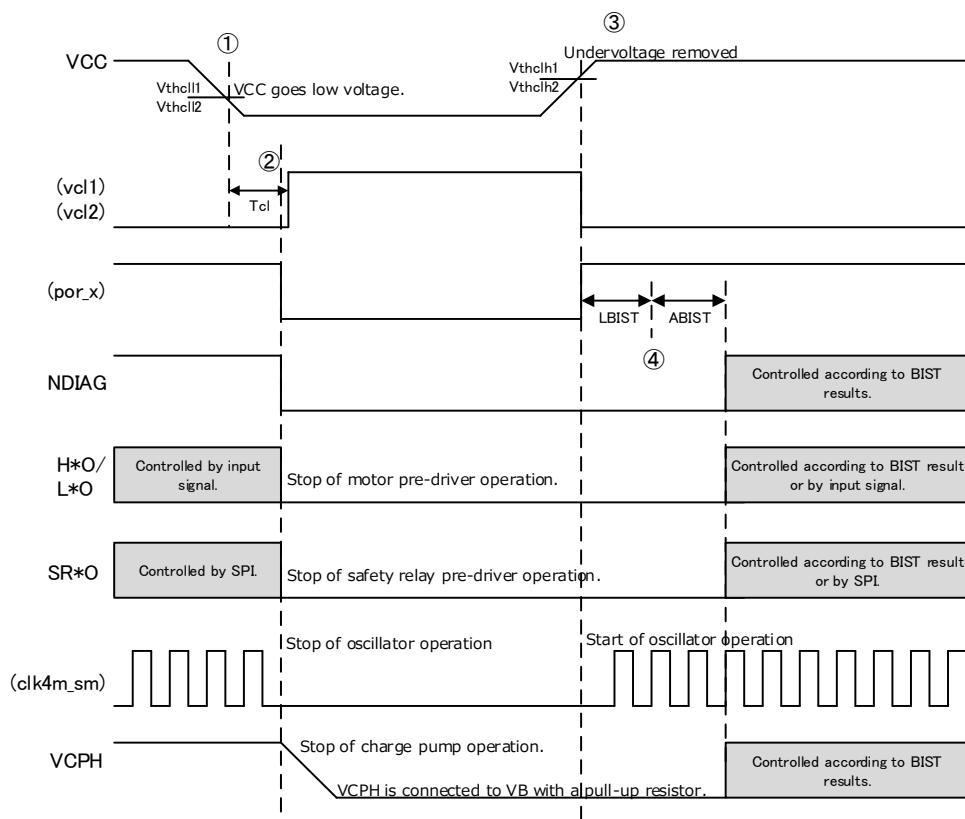

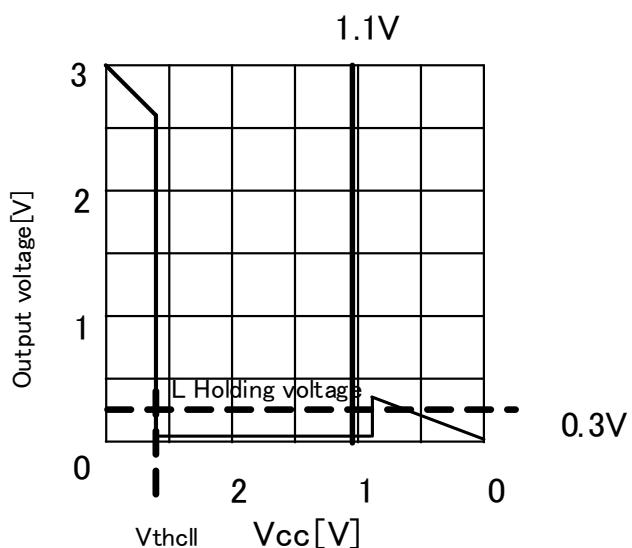

### 7.5.1. VCC 低電圧検出 1, 2 機能

VCC の低電圧検出を行います。検出コンパレーターを 2 つ内蔵しており、2 つのコンパレーターのうち 1 つでもコンパレーターの出力が“H”となれば、低電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、別々のバンドギャップ回路(BG1、BG2)から生成します。

Fig. 7.5.1-a VCC 低電圧検出ブロック図

## &gt; ① VCC 電圧低下

VCC 電圧が低電圧検出電圧  $V_{thcl1}$ ,  $V_{thcl2}$  を下回ります。

## &gt; ② VCC 低電圧検出

応答時間  $T_{cl}$  後、VCC 低電圧検出信号( $vcl1$ ),( $vcl2$ )="H"により低電圧状態を検出し、( $por_x$ )="L"となり、NDIAG="L"を出力し、モーター駆動(6ch)プリドライバー回路、セーフティーリレー(3ch)プリドライバー回路、チャージポンプ回路、発振回路をオフします。低電圧が解除されるまで、各回路はオフを保持します。

## &gt; ③ VCC 電圧復帰(低電圧解除)

VCC 電圧が  $V_{thclh1}$ ,  $V_{thclh2}$  を上回ると、VCC 低電圧検出信号( $vcl1$ ),( $vcl2$ )="L"となり低電圧が解除されます。

## &gt; ④ 通常動作復帰

LBIST、ABIST を実行後、BIST の診断が OK の場合に通常動作となります。チャージポンプ回路が動作を開始し、プリドライバー回路をオンすることが可能になります。診断が NG の場合は、チャージポンプ回路、プリドライバー回路は動作しません。また NDIAG は、診断 OK の場合は "H"、診断 NG の場合は "L" を出力します(7.7 を参照)。

Fig. 7.5.1-b VCC 低電圧検出タイミングチャート

- V<sub>cc</sub> 低電圧検出電圧よりもさらに V<sub>cc</sub> が低下すると、スタンバイ状態となります。スタンバイ状態では、V<sub>cc</sub> 低電圧検出以外の機能はオフします。

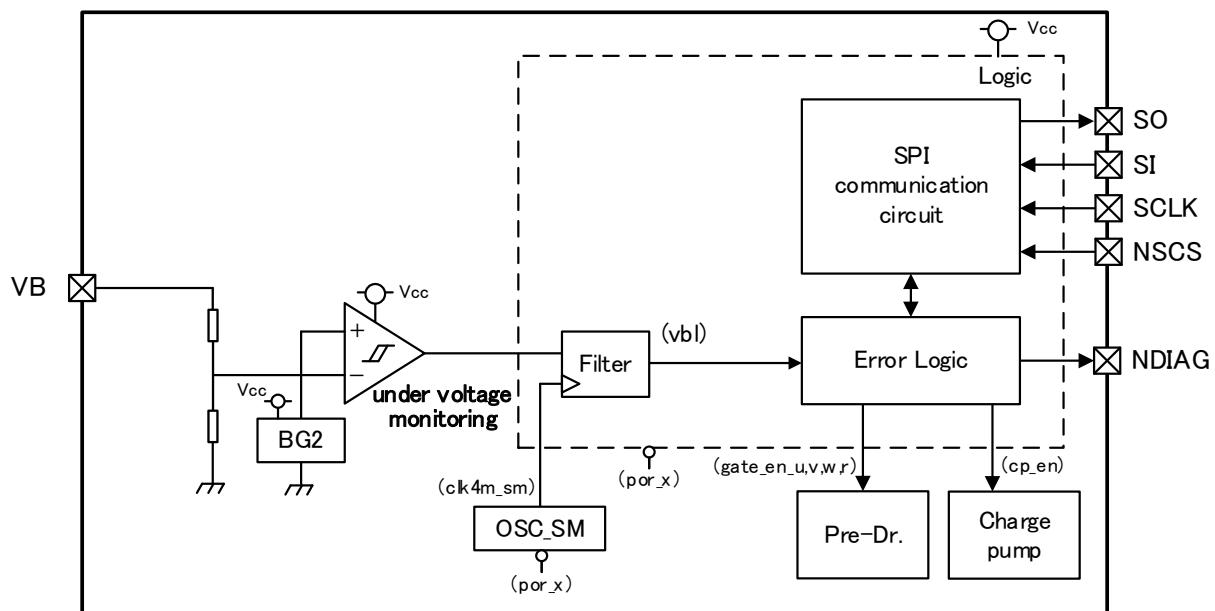

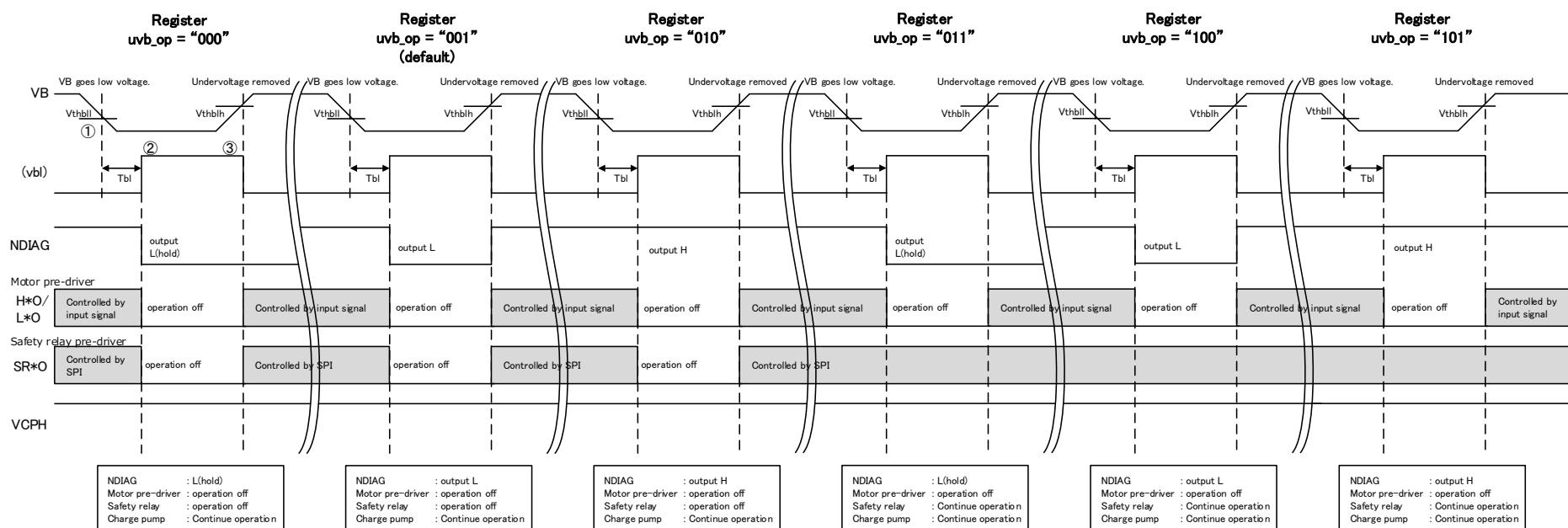

### 7.5.2. VB 低電圧検出機能

VB の低電圧検出を行います。検出コンパレーターおよびフィルターを内蔵しており、フィルター出力が“H”となれば、低電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、バンドギャップ回路(BG2)から生成します。

Fig. 7.5.2-a VB 低電圧検出ブロック図

## ➤ ① VB 電圧低下

VB 電圧が低電圧検出電圧  $V_{thbll}$  を下回ると、VB の L 検出コンパレーター出力が H となります。

## ➤ ② VB 低電圧検出

検出フィルター時間  $T_{bl}$  後、VB 低電圧検出信号(vbl)=“H”により低電圧状態を検出し、セーフティーリレー含めた全ての(9ch)プリドライバー回路または、モーター駆動(6ch)プリドライバー回路をオフします。発振回路、チャージポンプ回路はオフしません。低電圧が解除されるまで、プリドライバー回路はオフを保持します。

検出後の動作は、SPI 通信を介して 6 モードの選択が可能です。

VB 低電圧検出状態時にモード変更しても、設定が有効になりません。VB 低電圧が解除されレジスター:uvb をクリア後に設定が有効になります。

## ➤ ③ VB 電圧復帰(低電圧解除)

VB 電圧が  $V_{thblh}$  を上回ると、VB 低電圧検出信号(vbl)=“L”となり低電圧が解除され、プリドライバー回路は通常動作となります。

NDIAG=“L”を出力している場合、SPI 通信によりレジスター:uvb がクリアされると、NDIAG=“H”となります。

低電圧検出中は、レジスター:uvb をクリアできず、NDIAG=“L”を出力します。

Fig. 7.5.2-b VB 低電圧検出タイミングチャート

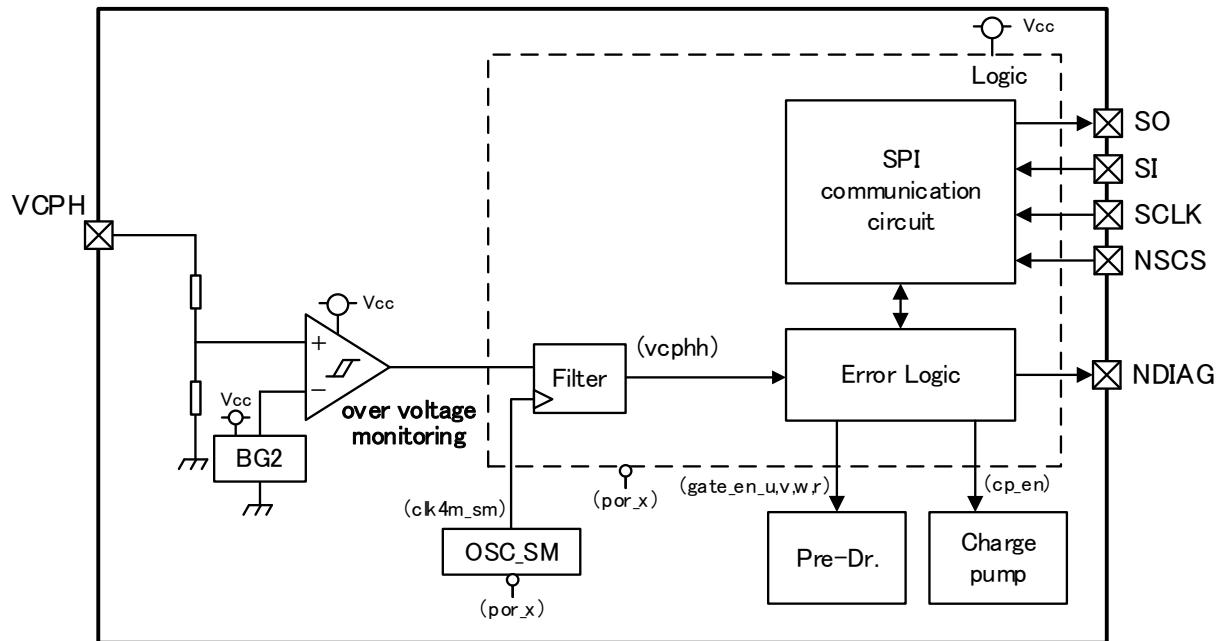

### 7.5.3. VCPH 高電圧検出機能

VCPH の高電圧検出を行います。検出コンパレーターおよびフィルターを内蔵しており、各フィルター出力が“H”となれば、高電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、バンドギャップ回路(BG2)から生成します。

Fig. 7.5.3-a VCPH 高電圧検出ブロック図

## ➤ ① VCPH 電圧上昇

VCPH 電圧が高電圧検出電圧  $V_{thcphhh}$  を上回ると、VCPH の H 検出コンパレーター出力が“H”となります。

## ➤ ② VCPH 高電圧検出

検出フィルター時間  $T_{cphh}$  後、VCPH 高電圧検出信号( $v_{cphh}$ )=“H”により高電圧状態を検出し、NDIAG=“L”となります。

ただし、レジスター:  $ocph\_op = "000"$  の場合、VCPH 高電圧検出時でも NDIAG=“H”を出力し、各回路も通常動作を継続します。

検出後の動作は、SPI 通信を介して 6 モードの選択が可能です。

VCPH 高電圧検出状態時にモード変更しても、設定が有効になりません。VCPH 高電圧が解除されレジスター:  $ocph$  をクリア後に設定が有効になります。

## ➤ ③ VCPH 電圧復帰(高電圧解除)

VCPH 電圧が  $V_{thcphhl}$  を下回ると、VCPH 高電圧検出信号( $v_{cphh}$ )=“L”となり高電圧が解除されます。

レジスター:  $ocph\_op = "101"$  の場合、高電圧が解除されてもチャージポンプ、プリドライバーはオフを保持し、NDIAG=“L”も保持します。

レジスター:  $ocph\_op = "001", "010", "011", "100"$  の場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG=“L”を保持します。

SPI 通信によりレジスター:  $ocph$  がクリアされると、各回路は通常動作となり、NDIAG=“H”となります。

高電圧検出中は、レジスター:  $ocph$  をクリアできず、NDIAG=“L”を出力します。

Fig. 7.5.3-b VCPH 高電圧検出タイミングチャート

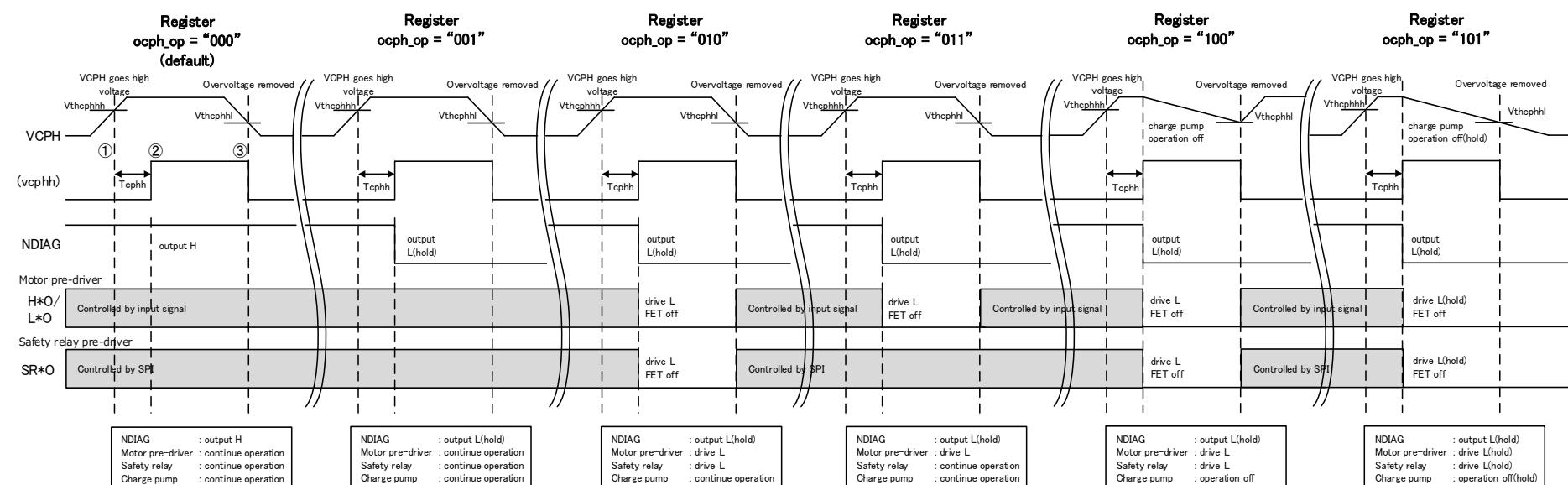

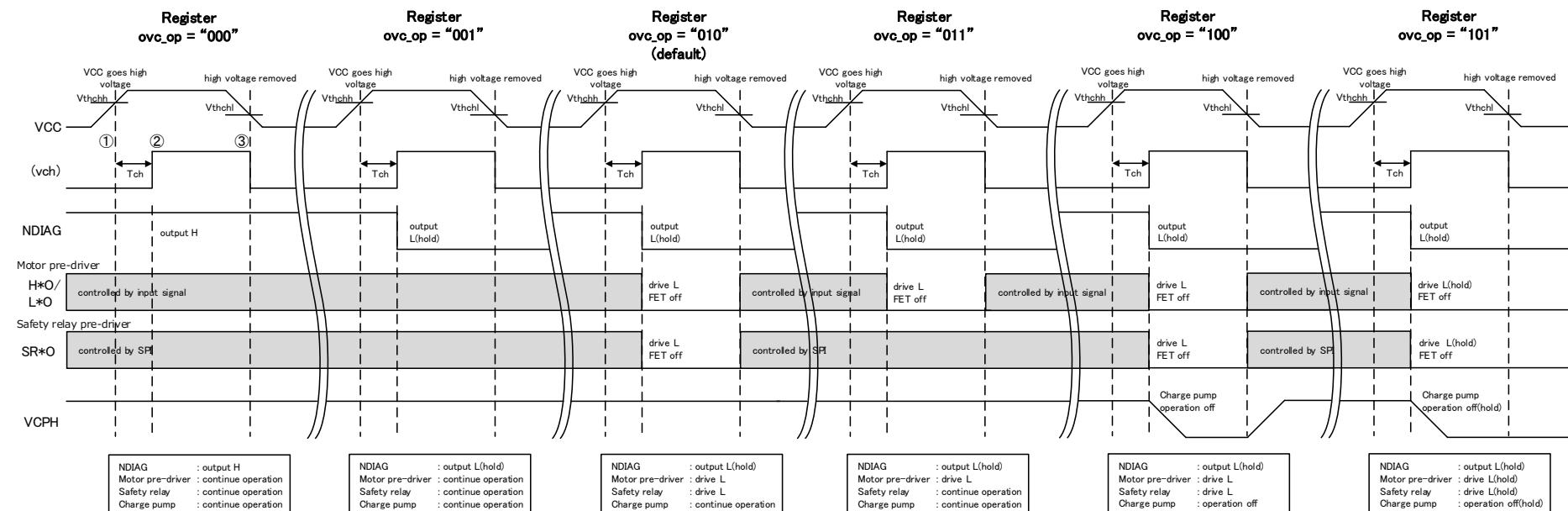

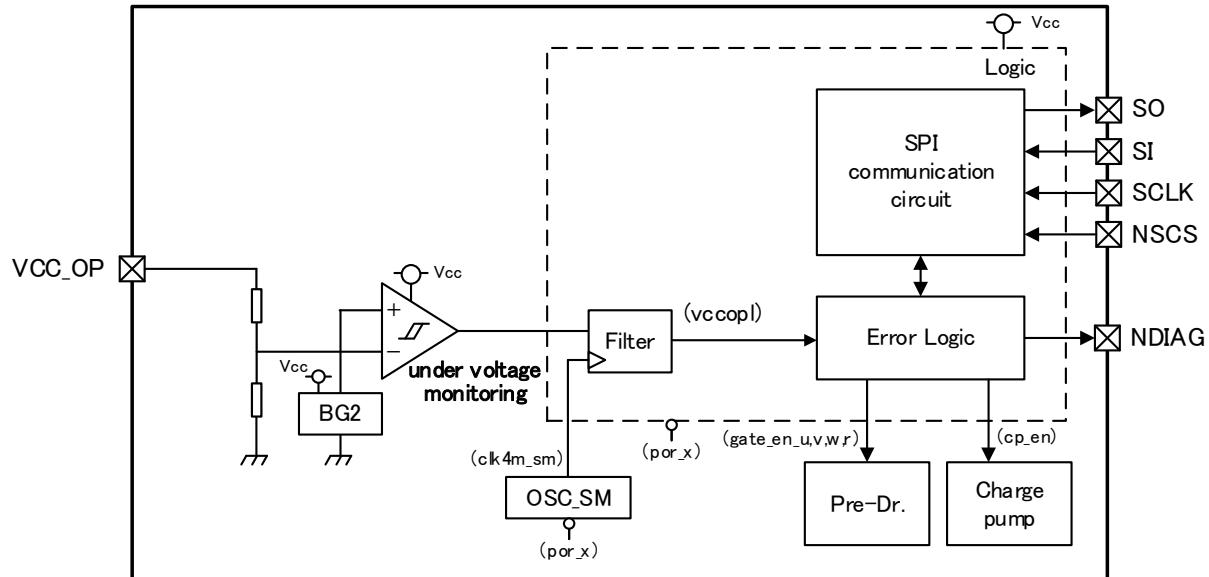

#### 7.5.4. VCC 高電圧検出機能

VCC の高電圧検出を行います。検出コンパレーターおよびフィルターを内蔵しており、各フィルター出力が“H”となれば、高電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、バンドギャップ回路(BG2)から生成します。

Fig. 7.5.4-a VCC 高電圧検出ブロック図

## &gt; ① VCC 電圧上昇

VCC 電圧が高電圧検出電圧  $V_{thchh}$  を上回ると、VCC の H 検出コンパレーター出力が“H”となります。

## &gt; ② VCC 高電圧検出

検出フィルター時間  $T_{ch}$  後、VCC 高電圧検出信号( $v_{ch}$ )=“H”により高電圧状態を検出し、NDIAG=“L”となります。

ただし、レジスター:ovc\_op=“000”的場合、VCC 高電圧検出時でも NDIAG=“H”を出力し、各回路も通常動作を継続します。

検出後の動作は、SPI 通信を介して 6 モードの選択が可能です。

VCC 高電圧検出状態時にモード変更しても、設定が有効になりません。VCC 高電圧が解除されレジスター:ovc をクリア後に設定が有効になります。

## &gt; ③ VCC 電圧復帰(高電圧解除)

VCC 電圧が  $V_{thchl}$  を下回ると、VCC 高電圧検出信号( $v_{ch}$ )=“L”となり高電圧が解除されます。

レジスター:ovc\_op=“101”的場合、高電圧が解除されてもチャージポンプ、プリドライバーはオフを保持し、NDIAG=“L”も保持します。

レジスター:ovc\_op=“001”, “010”, “011”, “100”的場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG=“L”を保持します。

SPI 通信によりレジスター:ovc がクリアされると、各回路は通常動作となり、NDIAG=“H”となります。

高電圧検出中は、レジスター:ovc をクリアできず、NDIAG=“L”を出力します。

Fig. 7.5.4-b VCC 高電圧検出タイミングチャート

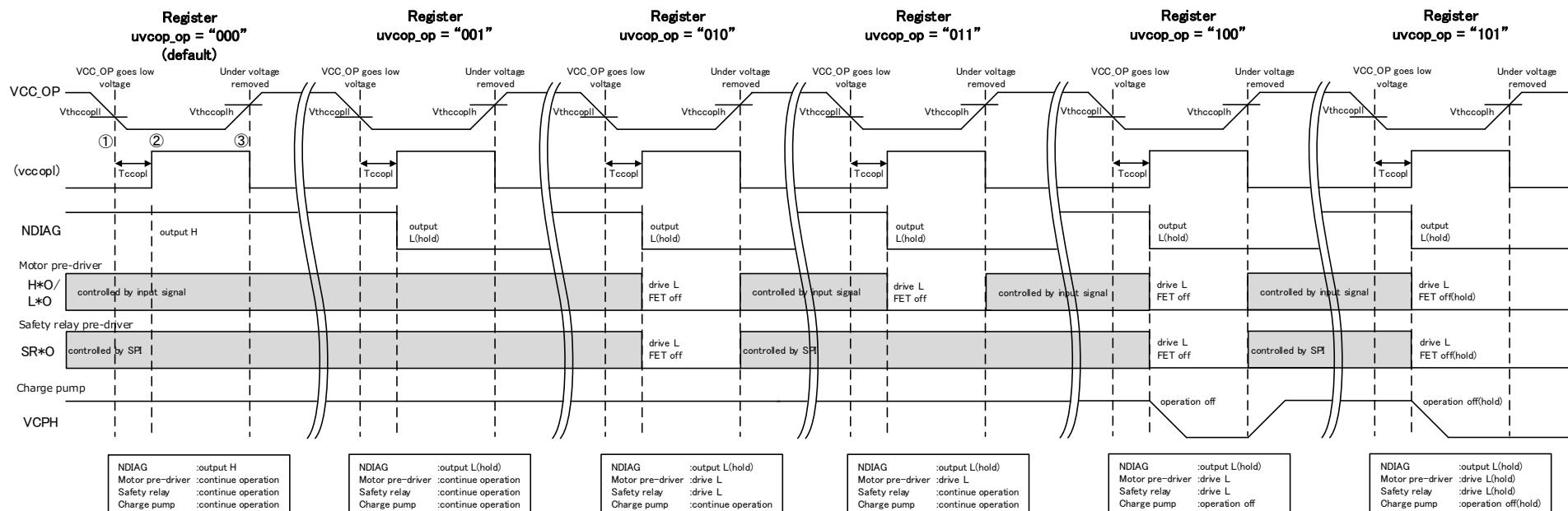

### 7.5.5. VCC\_OP 低電圧検出機能

VCC\_OP の低電圧検出を行います。検出コンパレーターおよびフィルターを内蔵しており、各フィルター出力が“H”となれば、低電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、バンドギャップ回路(BG2)から生成します。

Fig. 7.5.5-a VCC\_OP 低電圧検出ブロック図

## ➤ ① VCC\_OP 電圧低下

VCC\_OP 電圧が低電圧検出電圧  $V_{thccopl1}$  を下回ると、VCC\_OP の L 検出コンパレーター出力が“H”となります。

## ➤ ② VCC\_OP 低電圧検出

検出フィルター時間  $T_{ccopl}$  後、VCC\_OP 低電圧検出信号( $vccopl1$ )=“H”により低電圧状態を検出し、NDIAG=“L”となります。

ただし、レジスター:uvccop\_op = “000”的場合、VCC\_OP 低電圧検出時でも NDIAG=“H”を出力し、各回路も通常動作を継続します。

検出後の動作は、SPI 通信を介して 6 モードの選択が可能です。

VCC\_OP 低電圧検出状態時にモード変更しても、設定が有効になりません。VCC\_OP 低電圧が解除されレジスター:uvccop\_op をクリア後に設定が有効になります。

## ➤ ③ VCC\_OP 電圧復帰(低電圧解除)

VCC\_OP 電圧が  $V_{thccopl1}$  を上回ると、VCC\_OP 低電圧検出信号( $vccopl1$ )=“L”となり低電圧が解除されます。

レジスター:uvccop\_op = “101”的場合、低電圧が解除されてもチャージポンプ、プリドライバーはオフを保持し、NDIAG=“L”も保持します。

レジスター:uvccop\_op = “001”, “010”, “011”, “100”的場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG=“L”を保持します。

SPI 通信によりレジスター:uvccop がクリアされると、各回路は通常動作となり、NDIAG=“H”となります。

高電圧検出中は、レジスター:uvccop をクリアできず、NDIAG=“L”を出力します。

Fig. 7.5.5-b VCC\_OP 低電圧検出タイミングチャート

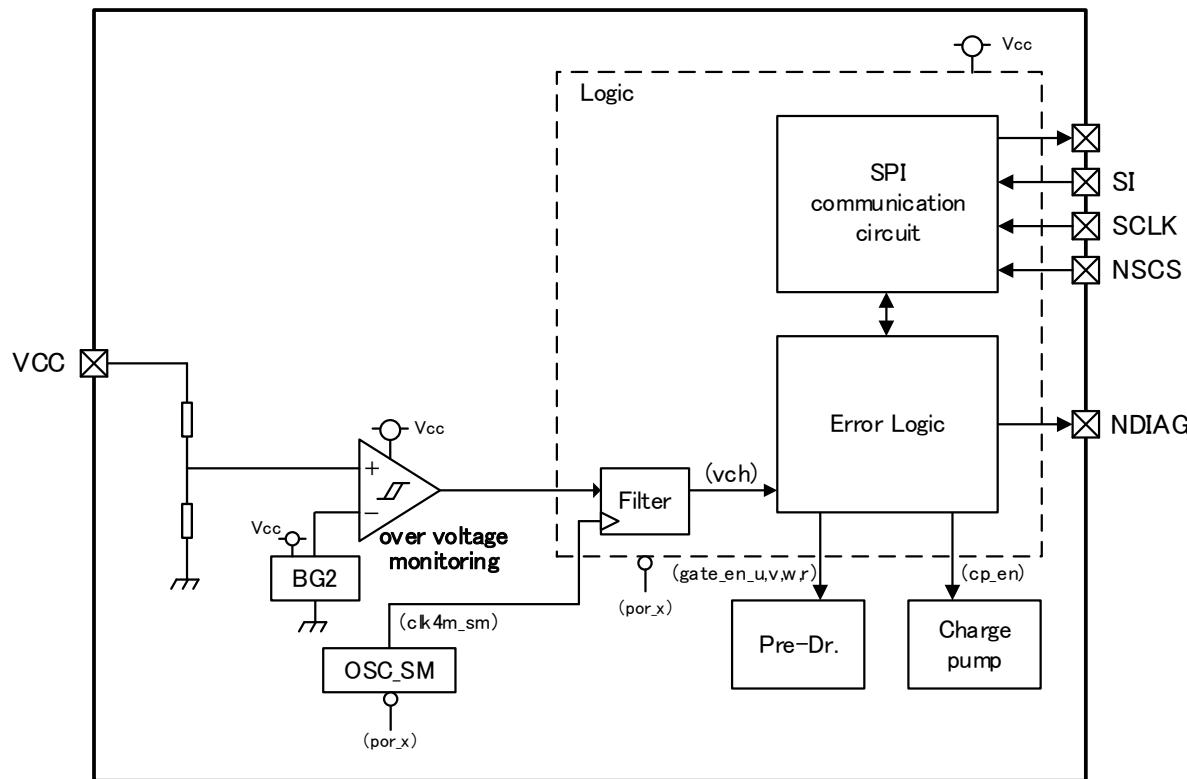

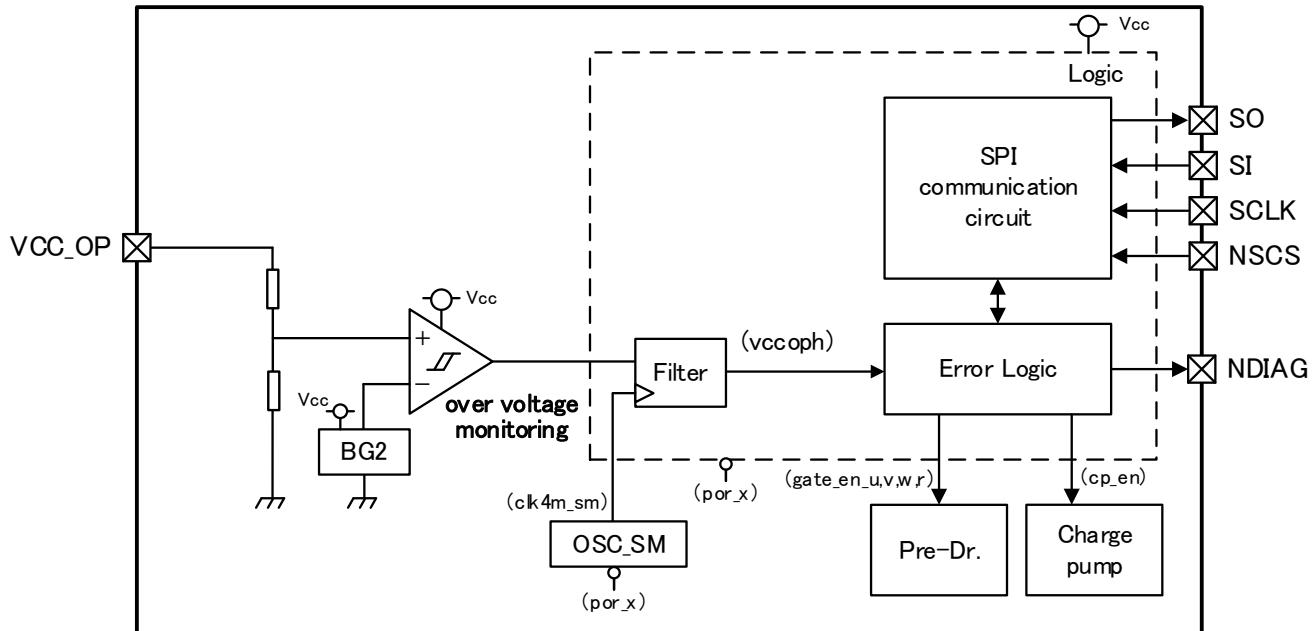

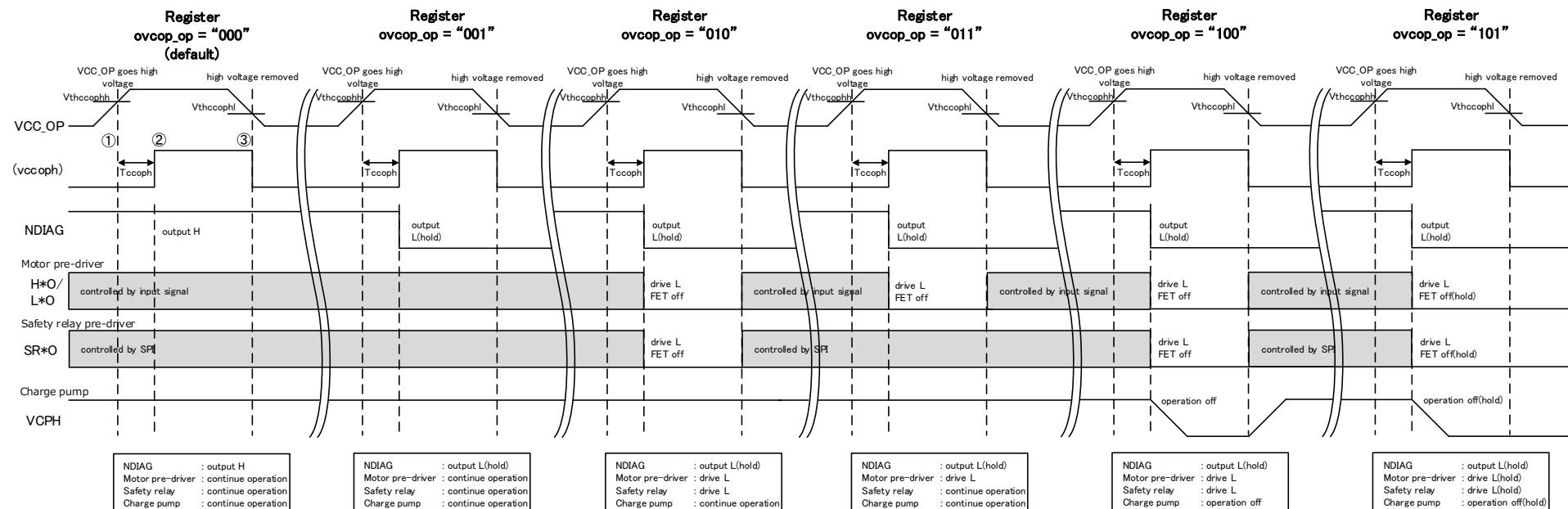

### 7.5.6. VCC\_OP 高電圧検出機能

VCC\_OP の高電圧検出を行います。検出コンパレーターおよびフィルターを内蔵しており、各フィルター出力が“H”となれば、高電圧検出が検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は、バンドギャップ回路(BG2)から生成します。

Fig. 7.5.6-a VCC\_OP 高電圧検出ブロック図

### ➤ ① VCC\_OP 電圧上昇

VCC\_OP 電圧が高電圧検出電圧  $V_{thccophh}$  を上回ると、VCC\_OP の H 検出コンパレーター出力が“H”となります。

### ➤ ② VCC\_OP 高電圧検出

検出フィルター時間  $T_{ccoph}$  後、VCC\_OP 高電圧検出信号( $vccoph$ )=“H”により高電圧状態を検出し、NDIAG=“L”となります。

ただし、レジスター:ovcop\_op =“000”的場合、VCC\_OP 高電圧検出時でも NDIAG=“H”を出力し、各回路も通常動作を継続します。

検出後の動作は、SPI 通信を介して 6 モードの選択が可能です。

VCC\_OP 高電圧検出状態時にモード変更しても、設定が有効になりません。VCC\_OP 高電圧が解除されレジスター:ovccop をクリア後に設定が有効になります。

### ➤ ③ VCC\_OP 電圧復帰(高電圧解除)

VCC\_OP 電圧が  $V_{thccophl}$  を下回ると、VCC\_OP 高電圧検出信号( $vccoph$ )=“L”となり高電圧が解除されます。

レジスター:ovcop\_op =“101”的場合、高電圧が解除されてもチャージポンプ、プリドライバーはオフを保持し、NDIAG=“L”も保持します。

レジスター:ovcop\_op =“001”, “010”, “011”, “100”的場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG=“L”を保持します。

SPI 通信によりレジスター:ovccop がクリアされると、各回路は通常動作となり、NDIAG=“H”となります。

高電圧検出中は、レジスター:ovccop をクリアできず、NDIAG=“L”を出力します。

Fig. 7.5.6-b VCC\_OP 高電圧検出タイミングチャート

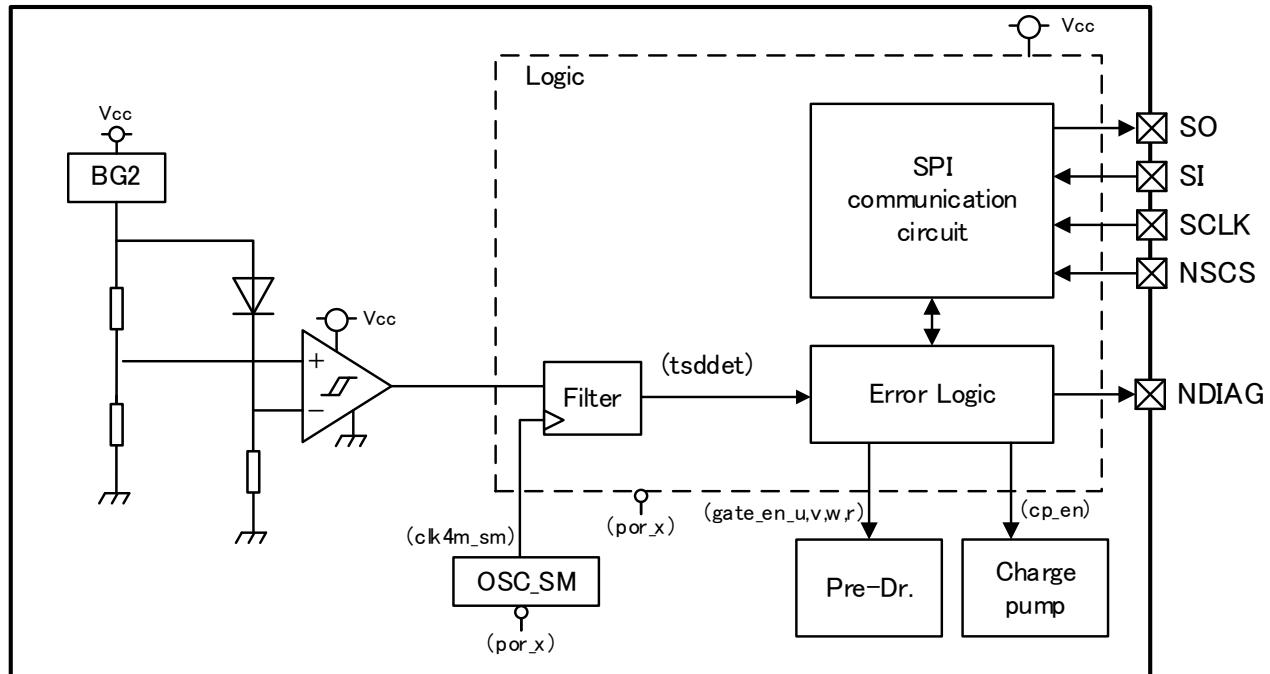

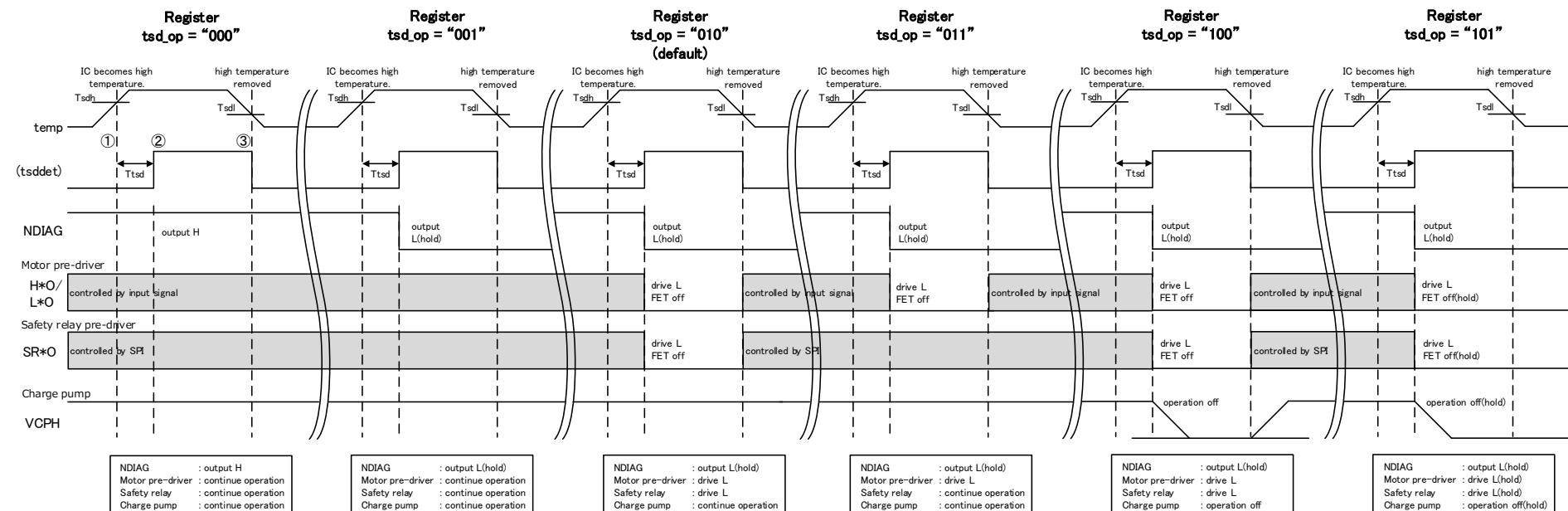

### 7.5.7. 過熱検出機能

過熱検出機能を内蔵しています。検出コンパレーターおよびフィルターを内蔵し、フィルターの出力が“H”となれば、過熱検出機能は検出状態となります。検出コンパレーターの基準となるバンドギャップ電圧は BG2 から生成します。

過熱検出コンパレーターではチップ温度が  $T_{sdh}$  を超えると過熱を検出します。また、内部温度が  $T_{sdl}$  を下回ると、過熱検出が解除されます。各検出後の動作は SPI 通信を介して 6 モードの選択が可能です。

Fig. 7.5.7-a 過熱検出ブロック図

### ➤ ①② 過熱検出

温度が  $T_{sdh}$  を上回ると、検出フィルター時間  $T_{tsd}$  後、過熱検出信号( $tsddet$ )="H"となり過熱状態を検出し、NDIAG="L"となります。

ただし、レジスター:tsd\_op="000"の場合、過熱検出時でも NDIAG="H"を継続、各回路も通常動作を継続します。

検出後の動作は、SPI通信を介して 6 モードの選択が可能です。

過熱検出状態時にモード変更しても、設定が有効になりません。過熱状態が解除されレジスター:tsd をクリア後に設定が有効になります。

### ➤ ③ 過熱検出解除

温度が  $T_{sdl}$  を下回ると、過熱検出信号( $tsddet$ )="L"となり過熱検出が解除されます。

ただし、レジスター:tsd\_op="101"の場合、過熱検出が解除されてもチャージポンプ、プリドライバーはオフを継続し、NDIAG="L"を保持します。

レジスター:tsd\_op="001", "010", "011", "100"の場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG="L"を保持します。

SPI通信によりレジスター:tsd がクリアされると、各回路は通常動作となり、NDIAG="H"となります。

過熱検出中は、レジスター:tsd をクリアできず、NDIAG="L"を出力します。

Fig. 7.5.7-b 過熱検出タイミングチャート

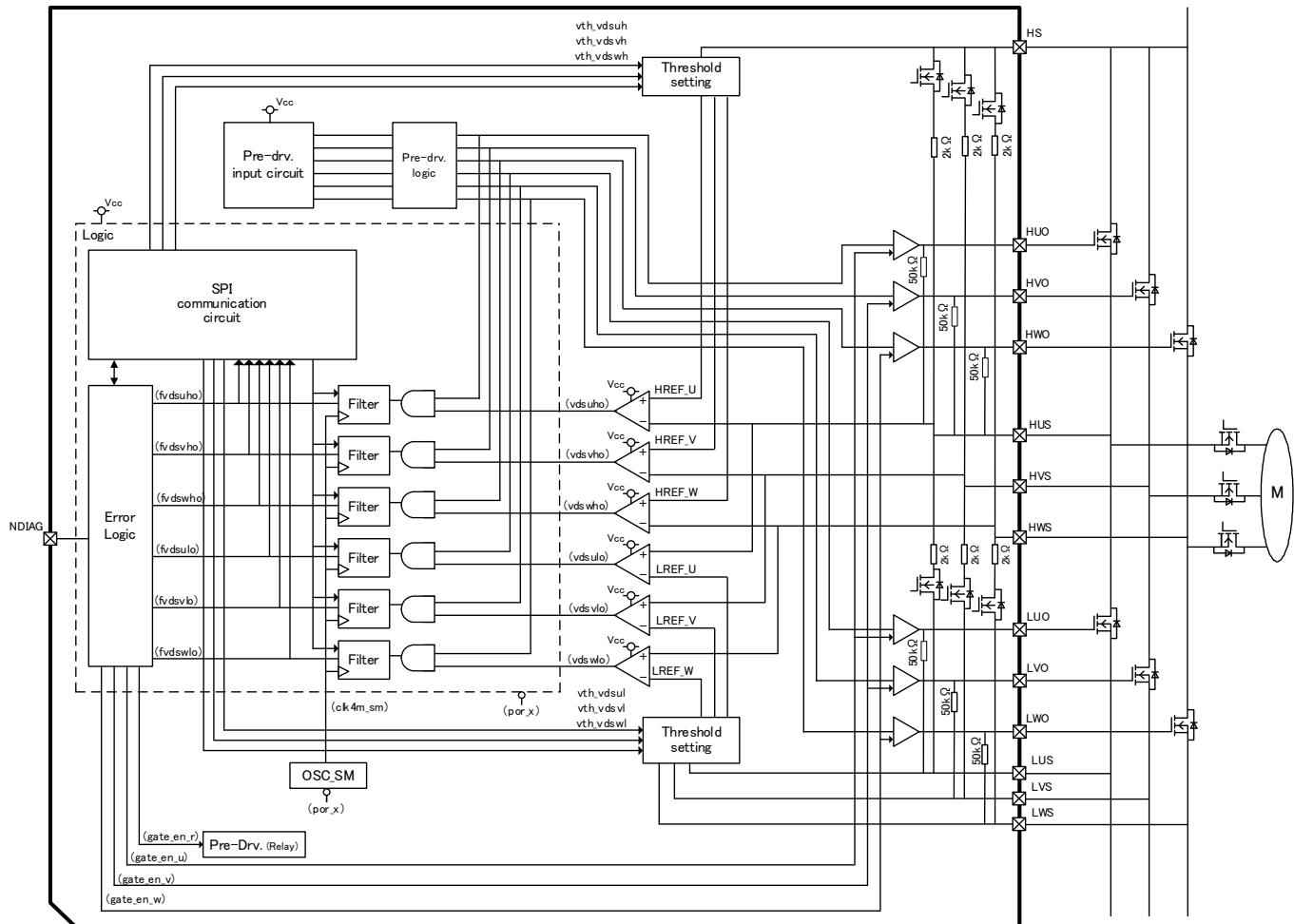

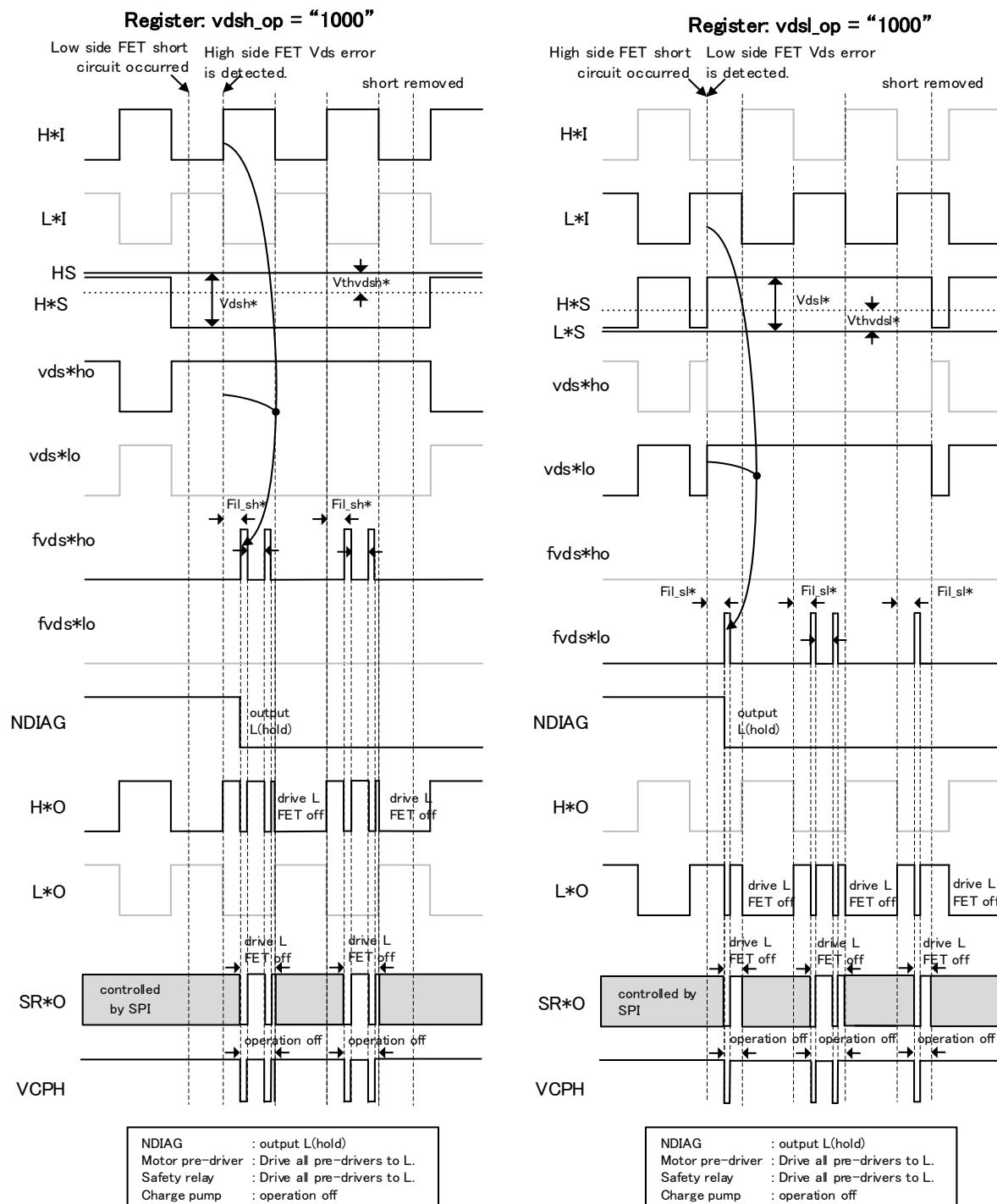

### 7.5.8. 外部 MOSFET の VDS 検出機能

外部 MOSFET の VDS 検出は外付け MOSFET のドレイン端子、ソース端子をモニターします。VDS 電圧異常を検出した場合、検出後の動作は FET\_OPSEL レジスターにより選択が可能です。詳細は表 7.5-a を参照してください。また、12 値の検出しきい値電圧および 4 値の検出時間についても HS\_VDS\_SEL, LS\_VDS\_SEL レジスターにより設定を変更できます。HUS, HVS, HWS 端子にはプルアップ、プルダウン抵抗を内蔵していますが通常はオフされています。詳細は 7.8 を参照してください。何らかの要因の異常検出によってプリドライバーが Disable されている相は VDS 検出がオフとなり、それ以上 VDS 検出要因がラッ奇されません。VDS 検出は FET\_DET\_SEL レジスターによりチャンネルごとに個別に無効にすることができます。

Fig. 7.5.8-a 外部 MOSFET の VDS 検出ブロック図

表 7.5.8-a VDS 検出シナリオ

| コンパレーター比較式                        | コンパレーター出力        | 入力信号        | 異常状態                  |

|-----------------------------------|------------------|-------------|-----------------------|

| $V_{HUS} - V_{LUS} > V_{thvdsul}$ | $(vdsulo) = "H"$ | $LUI = "H"$ | LUO の外部 MOSFET VDS 異常 |

| $V_{HVS} - V_{LVS} > V_{thvdsvl}$ | $(vdsvlo) = "H"$ | $LVI = "H"$ | LVO の外部 MOSFET VDS 異常 |

| $V_{HWS} - V_{LWS} > V_{thvdswh}$ | $(vdswo) = "H"$  | $LWI = "H"$ | LWO の外部 MOSFET VDS 異常 |

| $V_{HUS} - V_{HUS} > V_{thvdsuh}$ | $(vdsuho) = "H"$ | $HUI = "H"$ | HUO の外部 MOSFET VDS 異常 |

| $V_{HVS} - V_{HVS} > V_{thvdsvh}$ | $(vdsvho) = "H"$ | $HVI = "H"$ | HVO の外部 MOSFET VDS 異常 |

| $V_{HWS} - V_{HWS} > V_{thvdswh}$ | $(vdswho) = "H"$ | $HWI = "H"$ | HWO の外部 MOSFET VDS 異常 |

- ハイサイドの検出しきい値電圧は、IC 端子の HS-H\*S 間電圧で規定しています。

ハイサイド MOSFET のドレイン-ソース間電圧を考慮し、しきい値を設定してください。

- ローサイドの検出しきい値電圧は、IC 端子の H\*S-L\*S 間電圧で規定しています。

ローサイド MOSFET のドレイン-ソース間電圧を考慮し、しきい値を設定してください。

- \*は U, V, W。

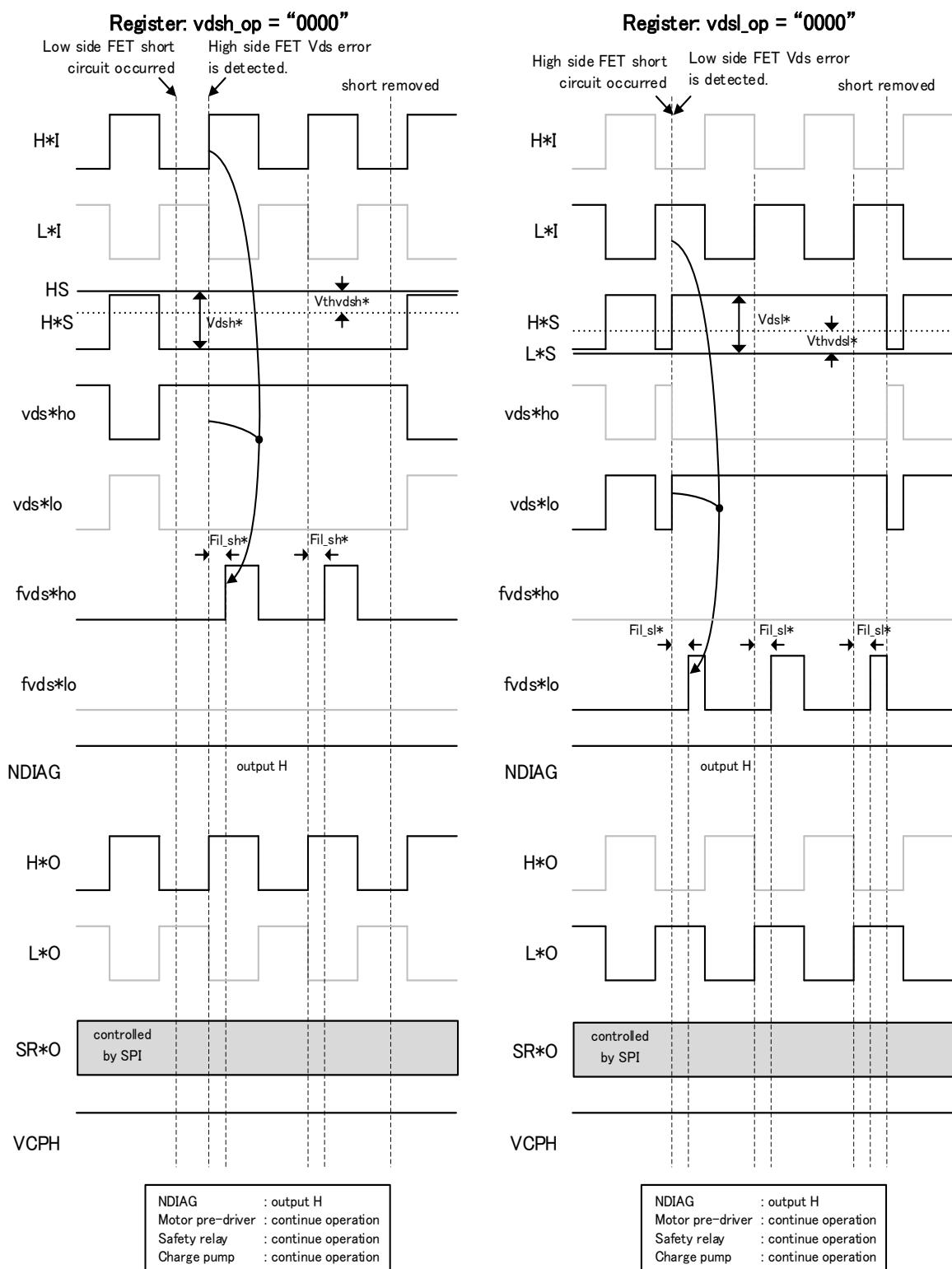

Fig. 7.5.8-b ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "0000"時)

Fig. 7.5.8-c ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "0001"時)

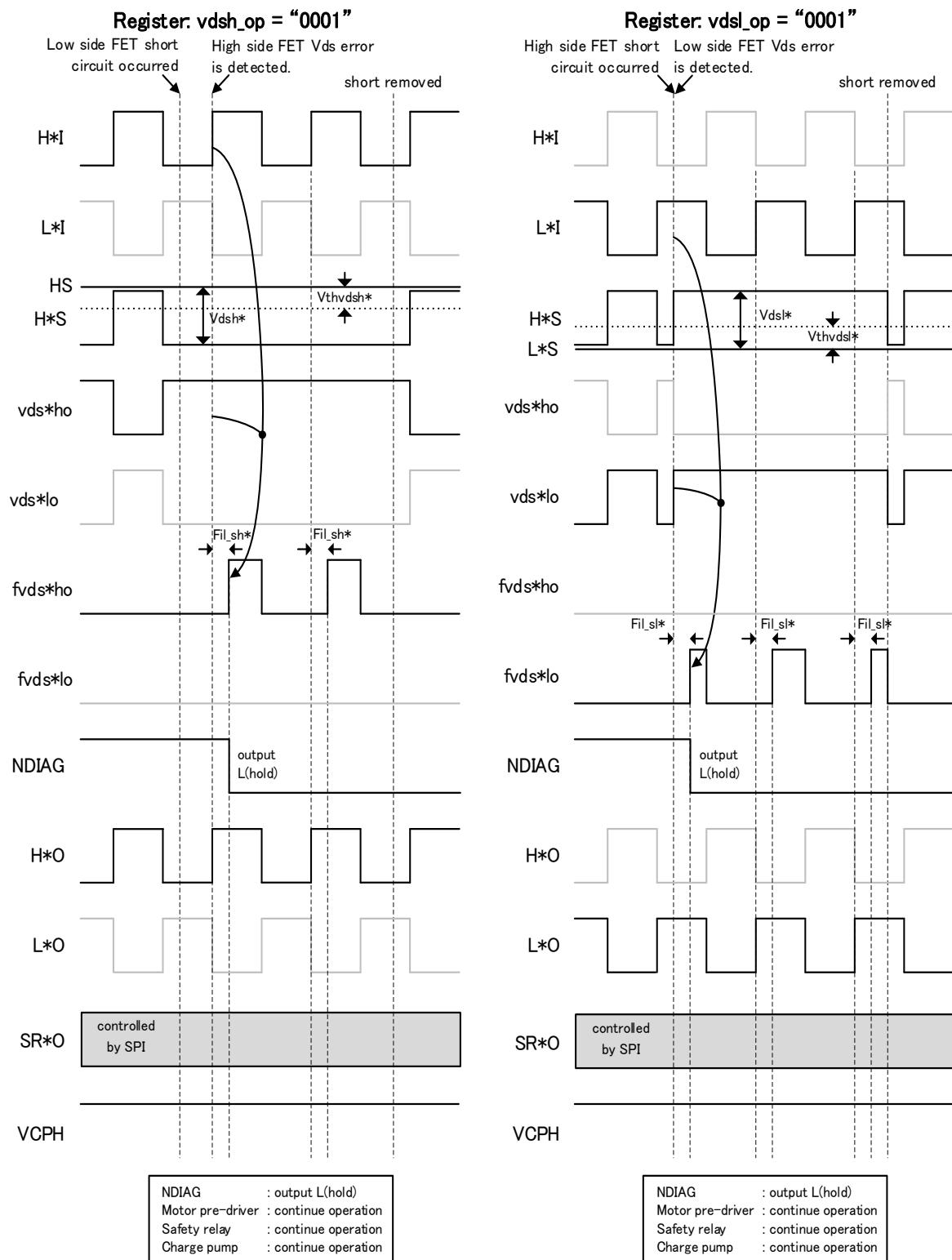

Fig. 7.5.8-d ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "0010"時)

Fig. 7.5.8-e ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "0011"時)

Fig. 7.5.8-f ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "0100" 時)

Fig. 7.5.8-g ショート検出タイミングチャート (レジスター: vdsi\_op = vdsh\_op "0101" 時)

Fig. 7.5.8-h ショート検出タイミングチャート（レジスター: vdsl\_op = vdsh\_op “0110”時）

Fig. 7.5.8-i ショート検出タイミングチャート (レジスター: vds\_l\_op = vdsh\_op "0111"時)

Fig. 7.5.8-j ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "1000"時)

Fig. 7.5.8-k ショート検出タイミングチャート (レジスター: vdsl\_op = vdsh\_op "1001"時)

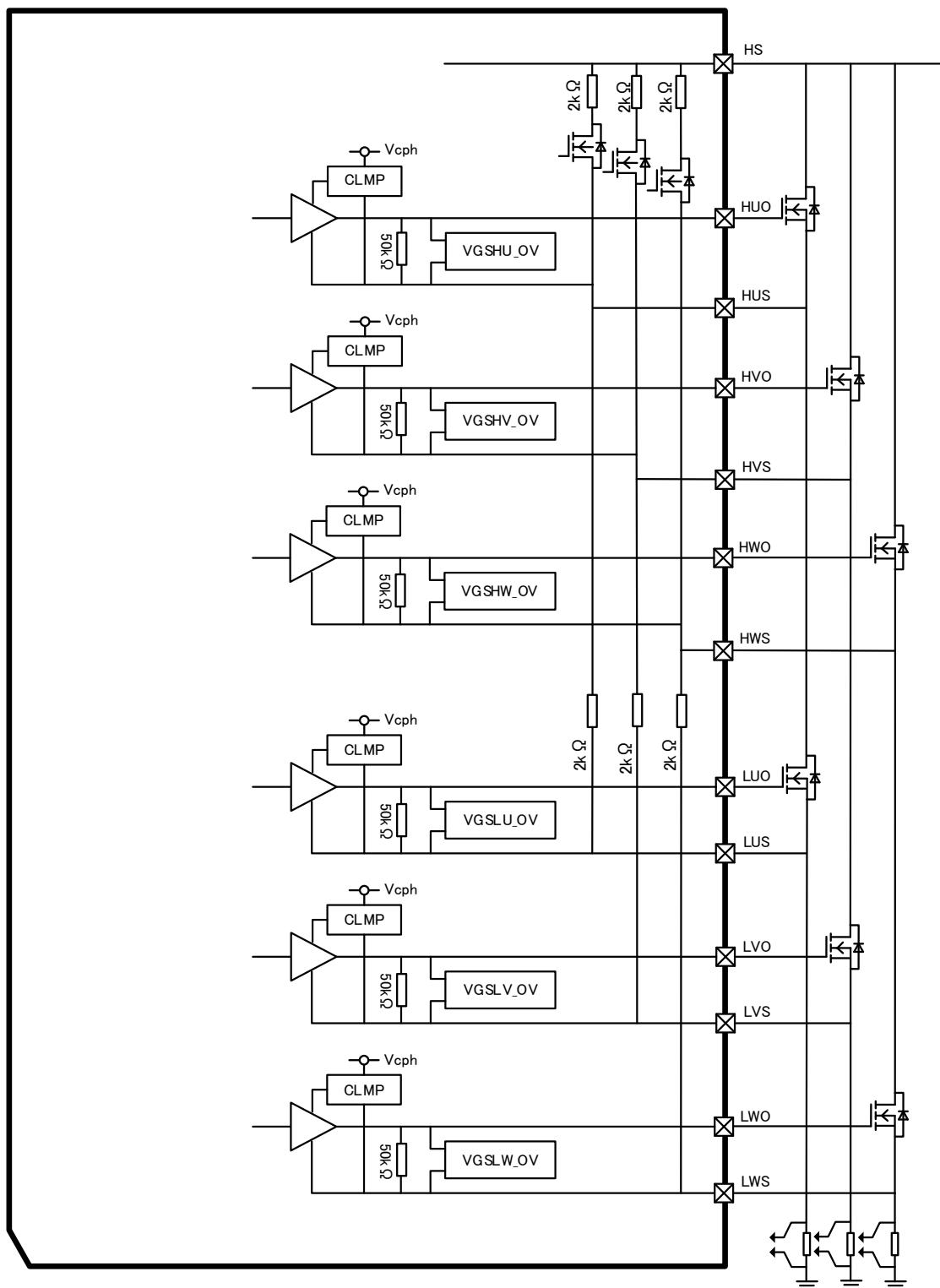

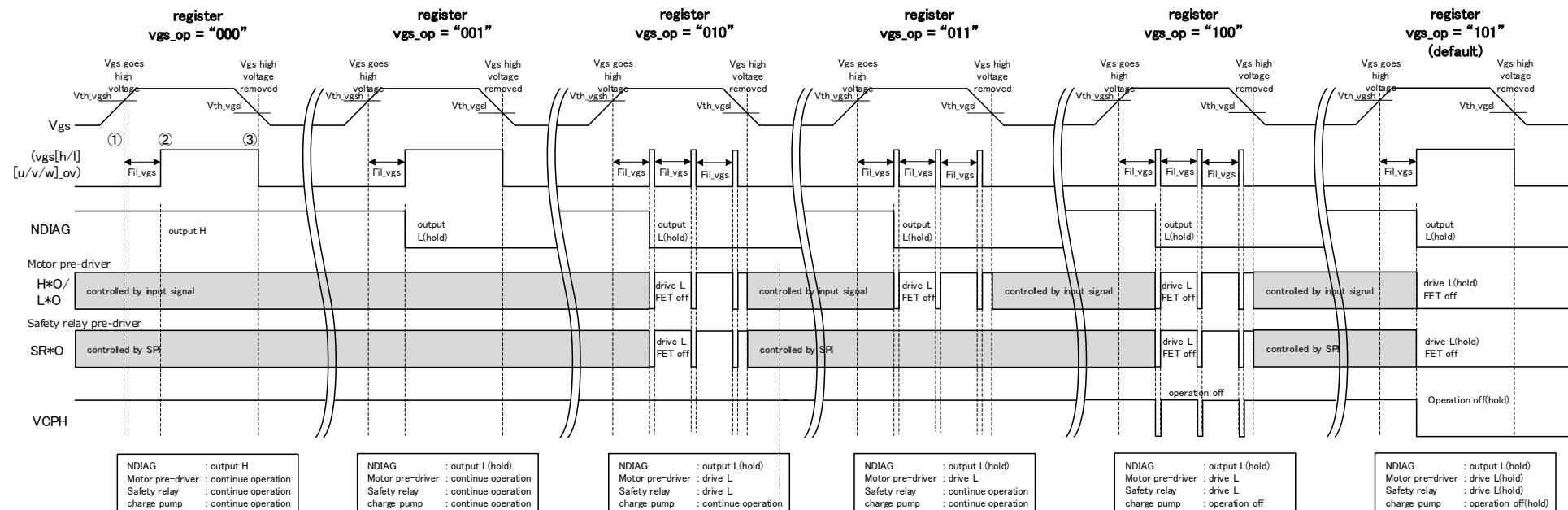

### 7.5.9. 外部 MOSFET の VGS 過電圧検出機能

外部 MOSFET の VGS が規定の電圧を超えたことを検出します。外付け MOSFET のゲート端子、ソース端子をモニターすることで検出します。VGS 過電圧は外部 MOSFET それぞれに独立に検出します。

Fig. 7.5.9-a VGS 過電圧検出ブロック図

VGS 過電圧を検出した場合、検出後の動作は [FET\\_OPSEL](#) レジスターにより選択が可能です。チャンネルごとにプリドライバーへの給電を停止することはできません。プリドライバーへの給電を停止する場合はチャージポンプをオフにしてください。過電圧の検出しきい値は VBG1, VBG2 とは別の基準電圧をチャンネルごとに独立に備えます。6 個の VGS 過電圧検出結果は [STAT2](#) レジスターにより確認することができます。チャンネルごとの VGS 過電圧検出の有効/無効は [FET\\_DET\\_SEL](#) レジスターにより設定することができます。

Fig. 7.5.9-b VGS 過電圧検出回路図

### ➤ ①② VGS 過電圧検出

VGS 電圧が  $V_{th\_vgsh}$  を上回ると、検出フィルター時間  $Fil\_vgs$  後、VGS 過電圧信号( $vgs[h/l][u/v/w]_{ov}$ )="H"となり VGS 過電圧検出状態となりし、NDIAG="L"となります。ただし、レジスター: $vgs\_op$ ="000"の場合、VGS 過電圧検出は無視され、NDIAG="H"を継続、各回路も通常動作を継続します。検出後の動作は、SPI 通信を介して 6 モードの選択が可能ですが、VGS 過電圧検出状態で検出時動作モードレジスターを変更しても、検出時の動作には即座に反映されません。VGS 過電圧状態が解除されレジスター: $vgs\_u/v/w[h/l]$ をクリアすると新たな設定が動作に反映されます。

### ➤ ③ VGS 過電圧検出解除

VGS 電圧が  $V_{th\_vgsl}$  を下回ると、VGS 過電圧信号( $tvgs[h/l][u/v/w]$ )="L"となり VGS 過電圧検出が解除されます。

ただし、レジスター: $vgs\_op$ ="101"の場合、VGS 過電圧検出が解除されてもチャージポンプ、プリドライバーはオフを継続し、NDIAG="L"を保持します。

レジスター: $vgs\_op$ ="001", "010", "011", "100"の場合、チャージポンプ、プリドライバーは通常動作となりますが、ステータスレジスターが保持されており、NDIAG="L"を保持します。

SPI 通信によりレジスター: $vgs[h/l][u/v/w]_{ov}$ がクリアされると、各回路は通常動作となり、NDIAG="H"となります。

VGS 過電圧検出中は、レジスター: $vgs[h/l][u/v/w]_{ov}$ をクリアできず、NDIAG="L"を出力します。

Fig. 7.5.9-c VGS 過電圧検出動作図

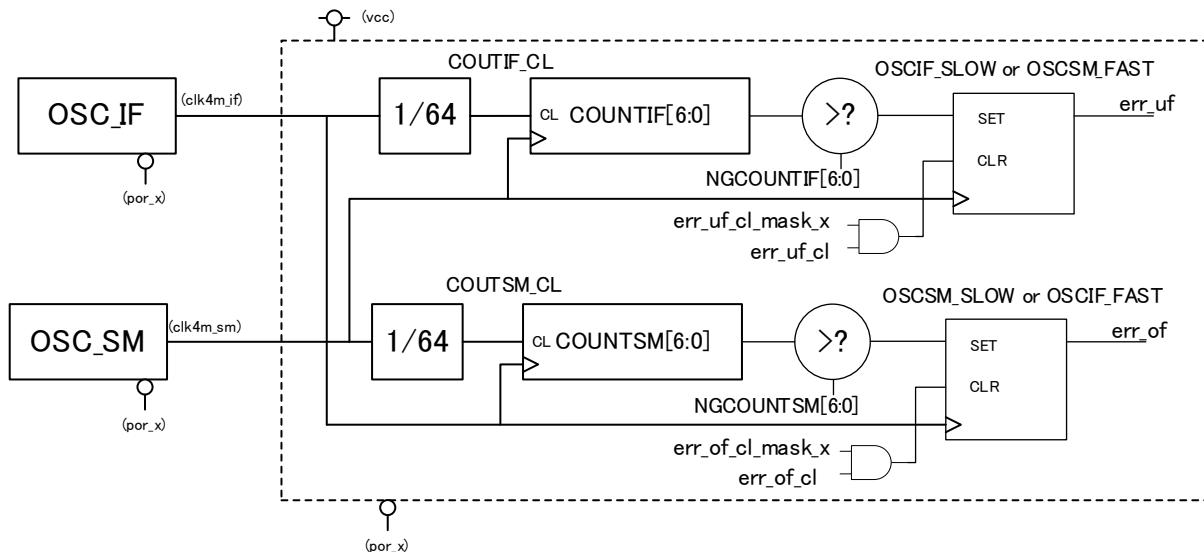

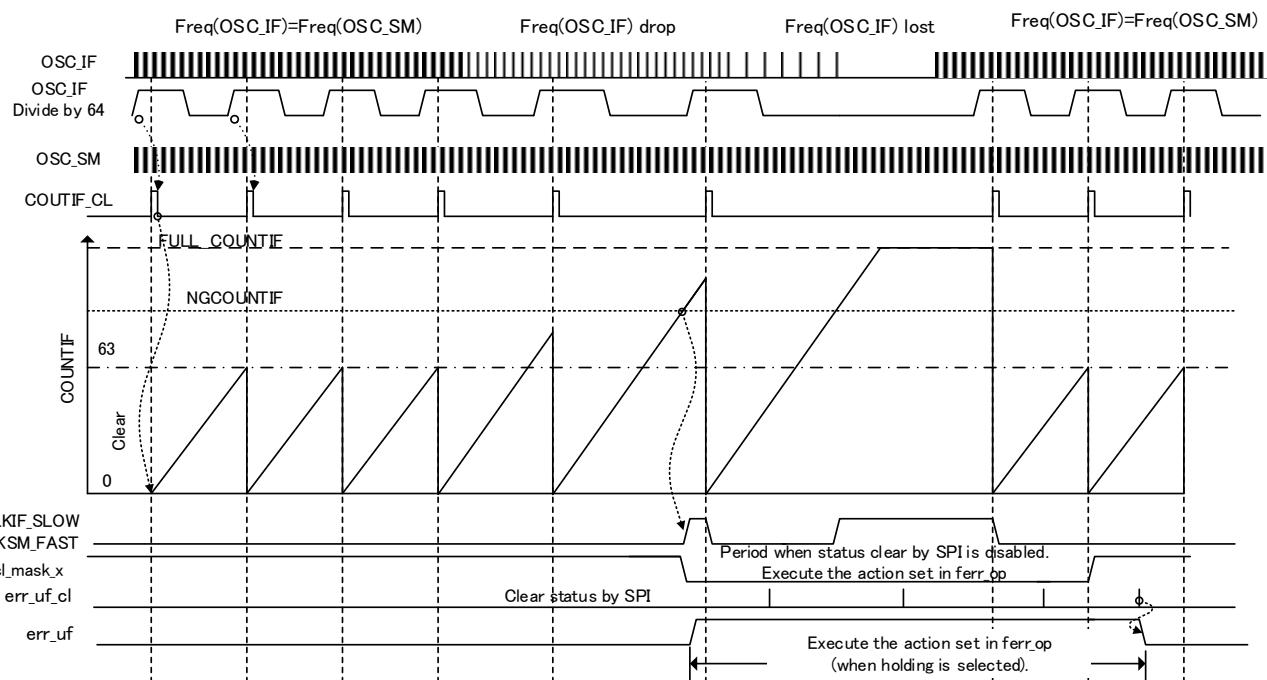

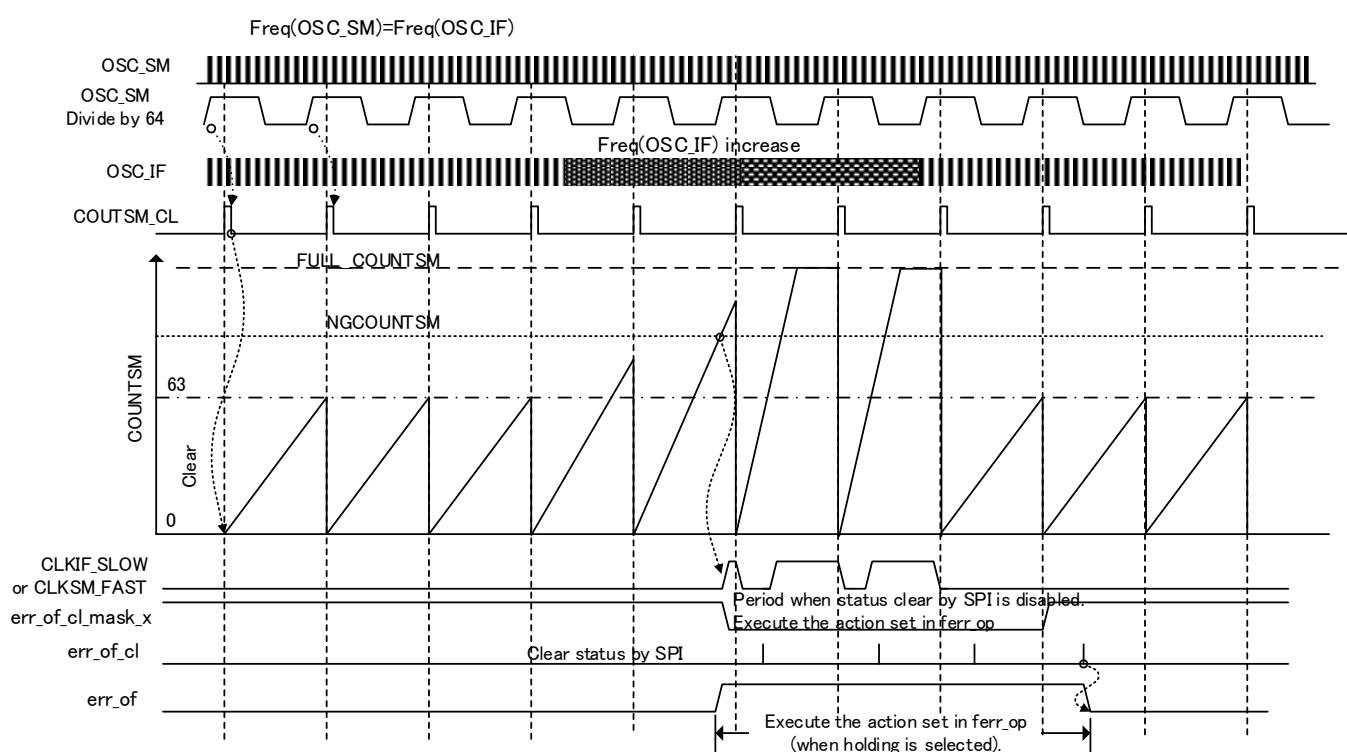

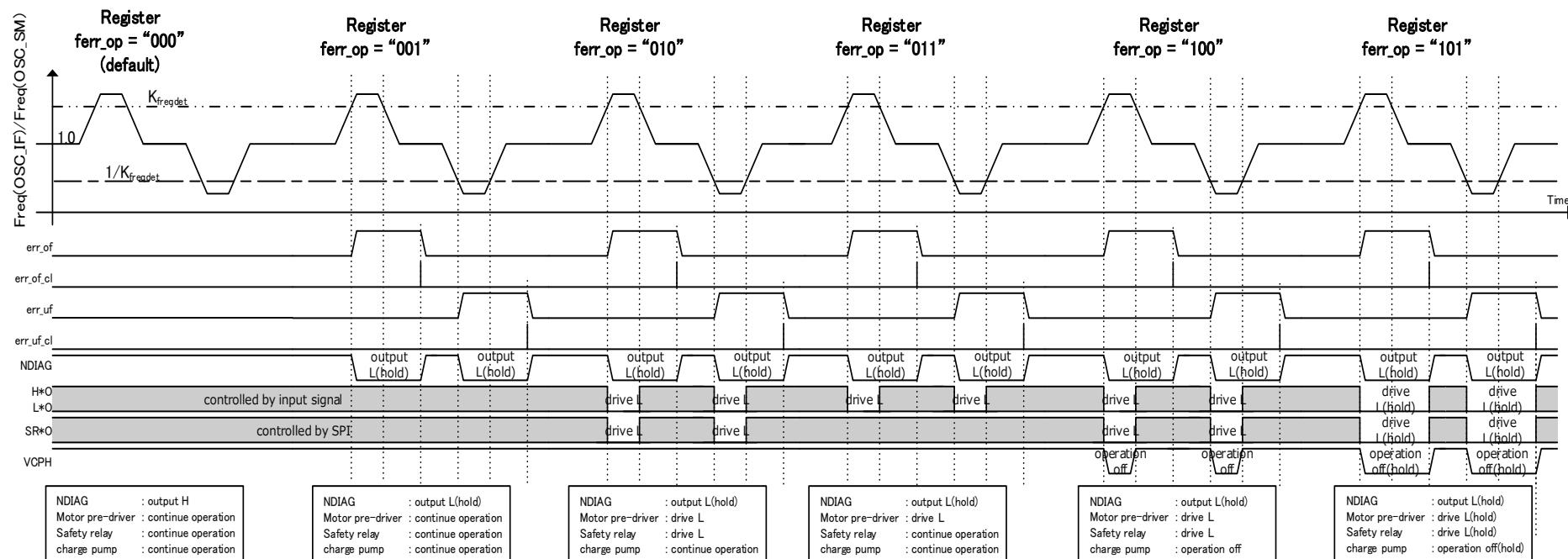

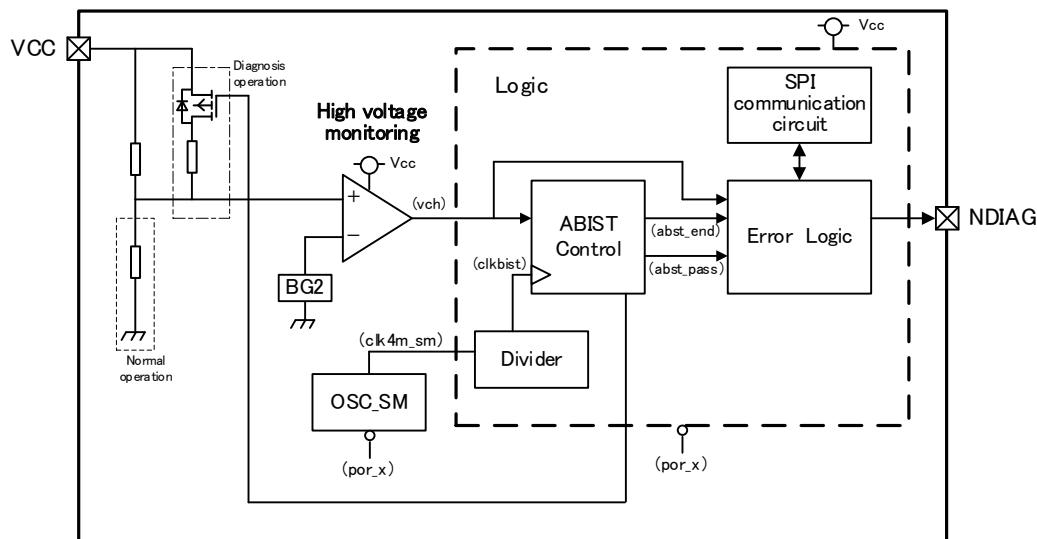

### 7.5.10. 発振周波数相互監視機能

2つの発振器 OSC\_IF と OSC\_SM が内蔵されており、その発振周波数を相互に監視する機能を備えています。OSC\_IF と OSC\_SM の発振周波数を相互に比較し OSC\_IF の発振周波数が OSC\_SM の発振周波数の(1/K<sub>freqdet</sub>)倍以下の場合に err\_uf レジスターがセットされ、OSC\_IF の発振周波数が OSC\_SM の発振周波数の K<sub>freqdet</sub> 倍以上である場合に err\_of レジスターがセットされます。OSC\_IF と OSC\_SM の発振周波数は BIST 期間以外常時比較しています。

周波数異常検出時の動作は ferr\_op レジスター設定により 6 モードの選択が可能です。詳細は表 7.5-a を参照してください。周波数異常検出状態時に ferr\_op レジスターの設定を変更した場合、ferr\_op レジスターには書き込まれますが、書き込まれた設定は有効になりません。周波数異常が解除され、レジスター:err\_of, err\_uf がクリアされると ferr\_op に書き込まれた

新たな設定が有効になります。

Fig. 7.5.10-a 発振周波数相互監視回路図

Fig. 7.5.10-b 発振周波数相互監視タイミングチャート（その 1）

Fig. 7.5.10-c 発振周波数相互監視タイミングチャート（その2）

ferr\_op=000 の場合は発振器の周波数検出は無効となります。

ferr\_op=000 以外では、OSC\_IF の周波数と OSC\_SM の周波数比が Kfreqdet 以上である場合は err\_of ステータスがセットされます。OSC\_IF の周波数と OSC\_SM の周波数比が 1/Kfreqdet 以下である場合は err\_uf ステータスがセットされます。NDIAG 端子は err\_uf, err\_of ステータスのどちらかがセットされていると "L" となります。NDIAG を "H" に復帰させる場合は、ステータスレジスターをクリアしてください。ステータスレジスターは最新の周波数比較結果が規定の範囲内(Kfreqdet 以下、1/Kreqdet 以上)に入っている場合しかクリアできません。

ferr\_op=010 の場合は、最新の周波数比較結果が規定の範囲に入っていない期間はプリドライバーおよび、リレー出力がオフに制御されます。

ferr\_op=011 の場合は、最新の周波数比較結果が規定の範囲に入っていない期間はプリドライバーの出力がオフに制御されます。

ferr\_op=100 の場合は、最新の周波数比較結果が規定の範囲に入っていない期間はプリドライバー、リレーとチャージポンプがオフに制御されます。

ferr\_op=101 の場合は、ステータスレジスターがセットされている期間は、プリドライバー、リレーとチャージポンプがオフに制御されます。

Fig. 7.5.10-d 発振周波数相互比較異常件出時の動作モード

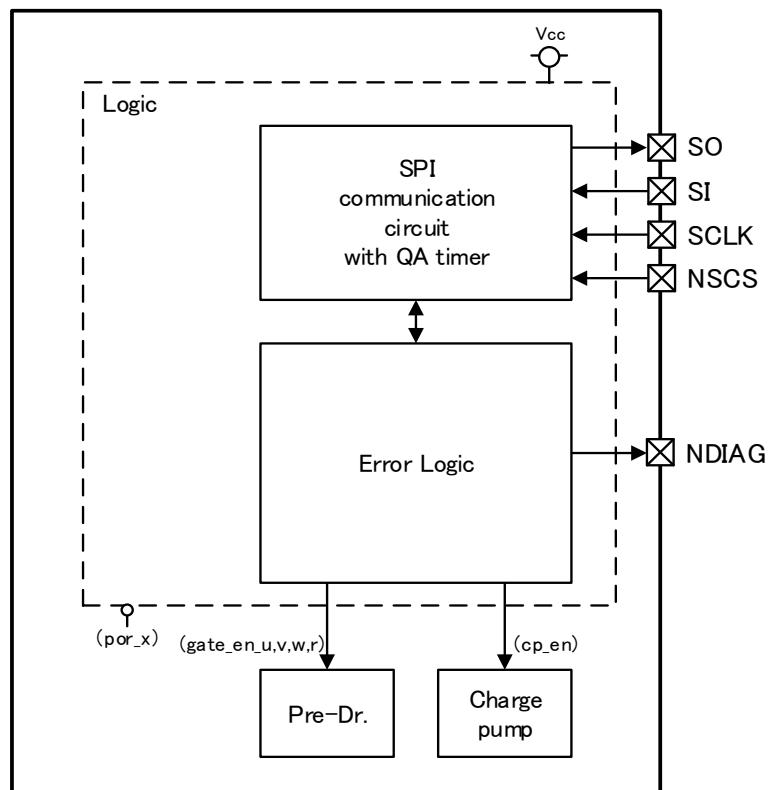

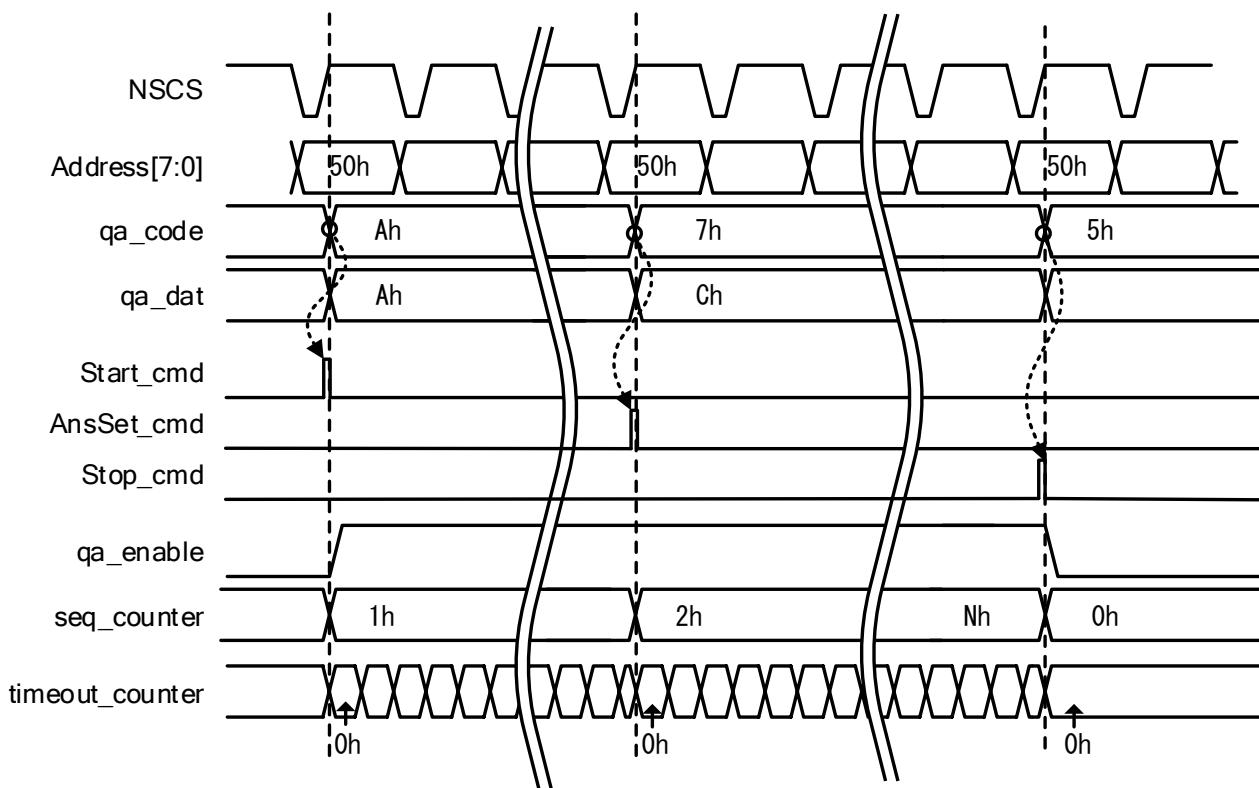

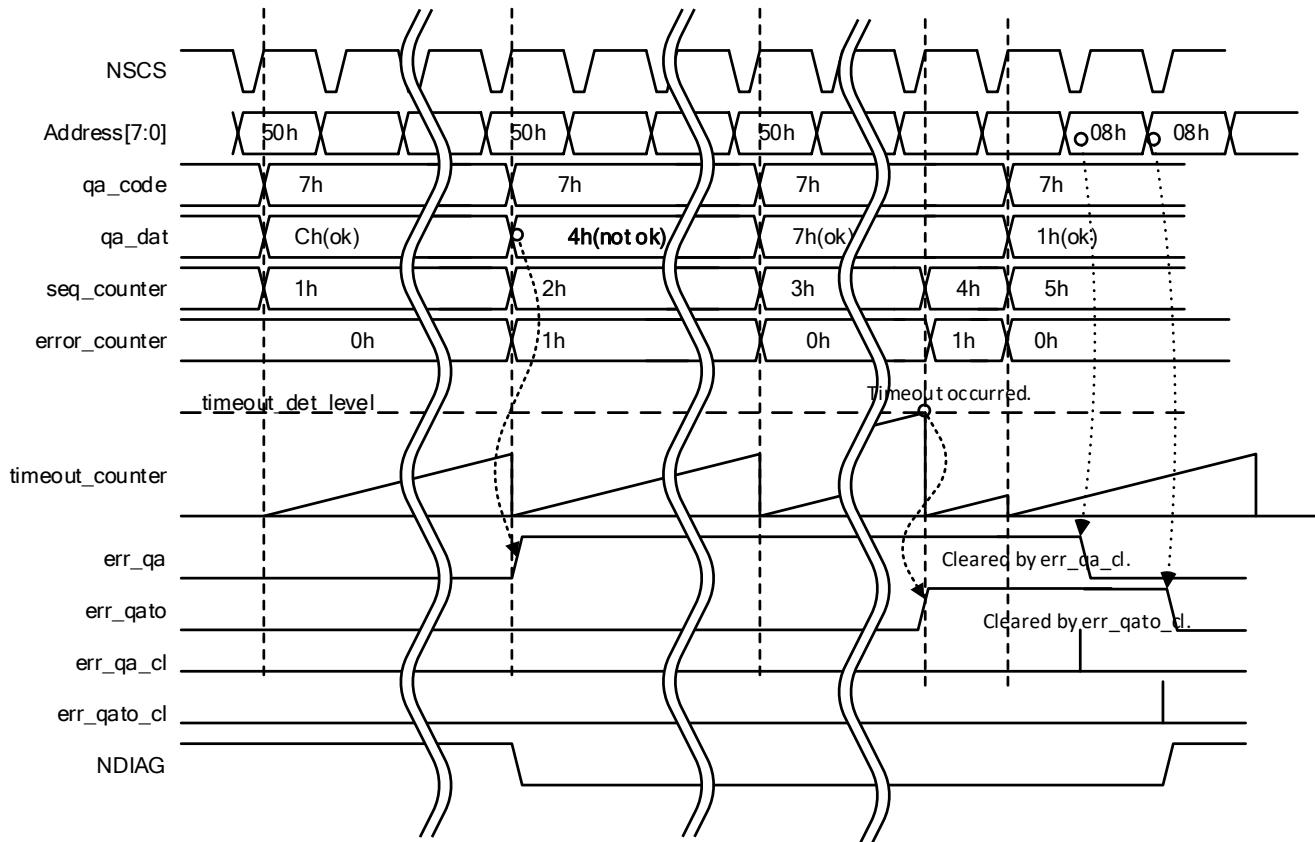

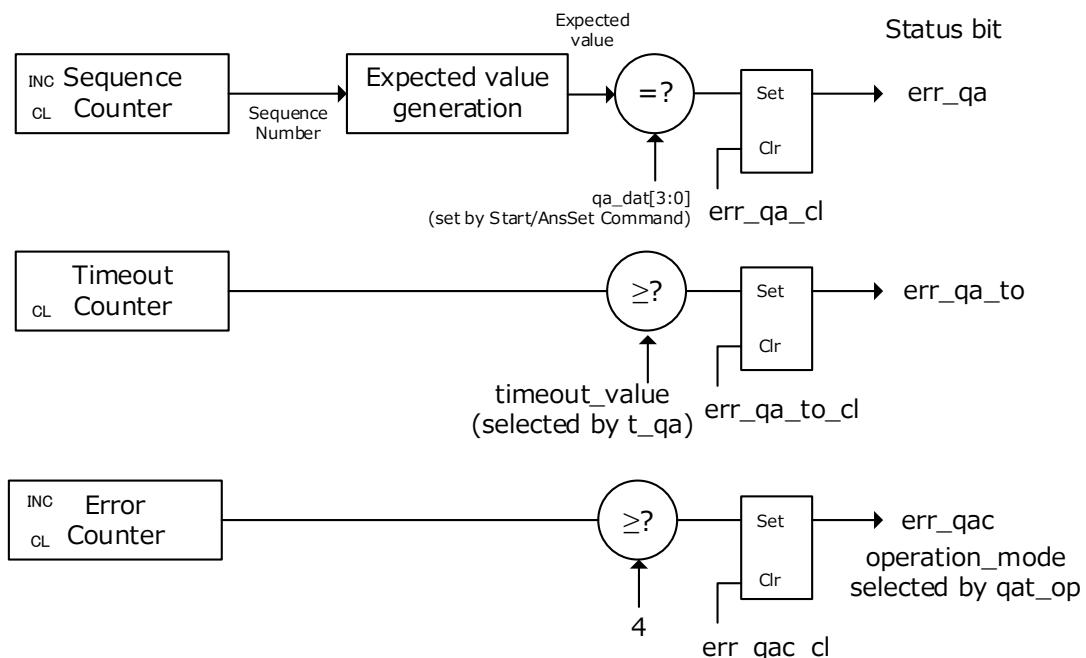

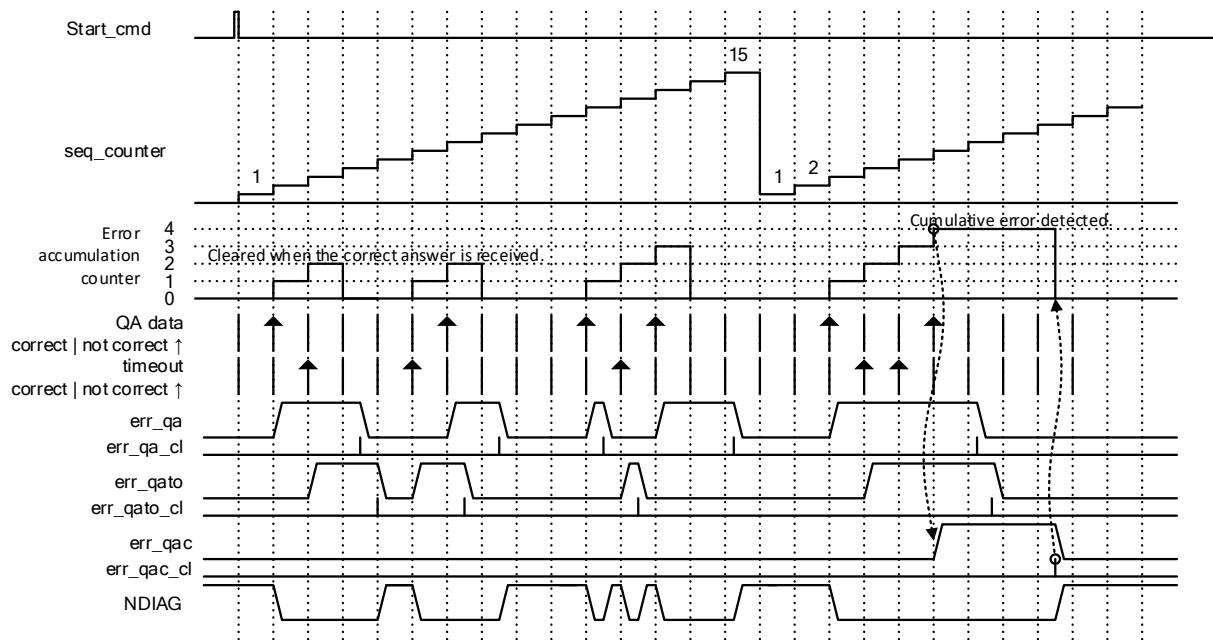

### 7.5.11. QA 演算検出機能

SPI 通信ブロックは QA 演算検出機能を備えています。詳細は表 7.5-a と 7.9.2 を参照ください。

Fig. 7.5.11-a QA 演算検出ブロック図

## ➤ ① QA 演算エラー検出

QA 演算エラーを検出すると、レジスター:err\_qa="H"となり、NDIAG="L"となります。QA タイムアウトを検出すると、レジスター:err\_qato="H"となり、NDIAG="L"となります。

## ➤ ② QA 演算エラー累積検出

QA 演算エラー累積を検出すると、レジスター:err\_qac="H"となり、レジスターqat\_op の設定に従って動作します。

検出後の動作は、SPI 通信を介して 4 モードの選択が可能です。

Fig. 7.5.11-b QA 演算エラー検出タイミングチャート

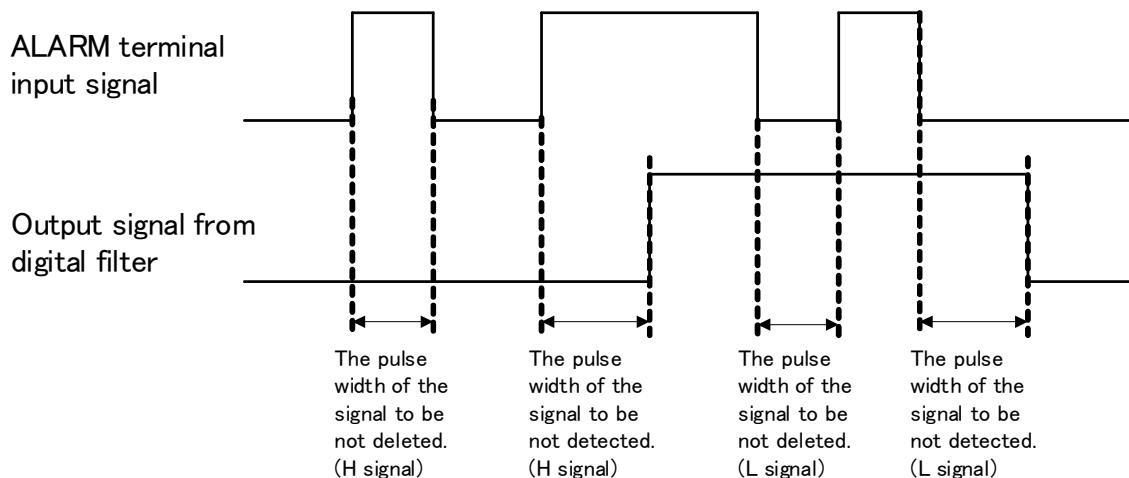

## 7.6. ALARM 入力回路

マイコンからプリドライバーを停止させるための信号入力として、ALARM 端子があります。ALARM 信号は OSC\_SM を使用する内部信号と OSC\_IF を使用する内部信号があります。ALARM 信号はプリドライバ回路(モーター駆動、セーフティーリレー)の Enable/Disable 制御を行います。

- ALARM="L"の場合 [ALM\\_CTRL](#) レジスターで設定したプリドライバー回路が Disable となります。

- ALARM="H"の場合プリドライバ回路の入力と内部信号によって Enable/Disable が決まります。

- ALARM 端子の入力側にはノイズ除去のためのデジタルフィルター(D.F.)を内蔵しています。

- デジタルフィルター時間は [ALM\\_CTRL](#) レジスターで設定可能です。

- SPI 通信によりリードできる ALARM 検出ステータス [STAT1](#) レジスターの alm\_det は OSC\_SM を使用した信号のみとなります。

Fig. 7.6-a MOSFET 駆動回路制御ブロック図

表 7.6-a MOSFET 駆動回路制御真理値表

| por_x | alr_op | almdet_if_x | almdet_sm_x | gate_en_u   | gate_en_v   | gate_en_w   | gate_en_r   |

|-------|--------|-------------|-------------|-------------|-------------|-------------|-------------|

| L     | *      | *           | *           | L           | L           | L           | L           |

| H     | L      | L           | *           | L           | L           | L           | L           |

|       |        | *           | L           | L           | L           | L           | L           |

|       |        | H           | H           | ~gate_off_u | ~gate_off_v | ~gate_off_w | ~gate_off_r |

|       | H      | L           | *           | L           | L           | L           | ~gate_off_r |

|       |        | *           | L           | L           | L           | L           | ~gate_off_r |

|       |        | H           | H           | ~gate_off_u | ~gate_off_v | ~gate_off_w | ~gate_off_r |

- \*:Don't care

- gate\_off\_u, gate\_off\_v, gate\_off\_w, gate\_off\_r は Alarm 要因以外のプリドライバー停止指示信号

- gate\_off\_if, gate\_off\_rif は Alarm 要因以外のプリドライバー停止指示信号(OSC\_IF を使用した周波数異常検出)

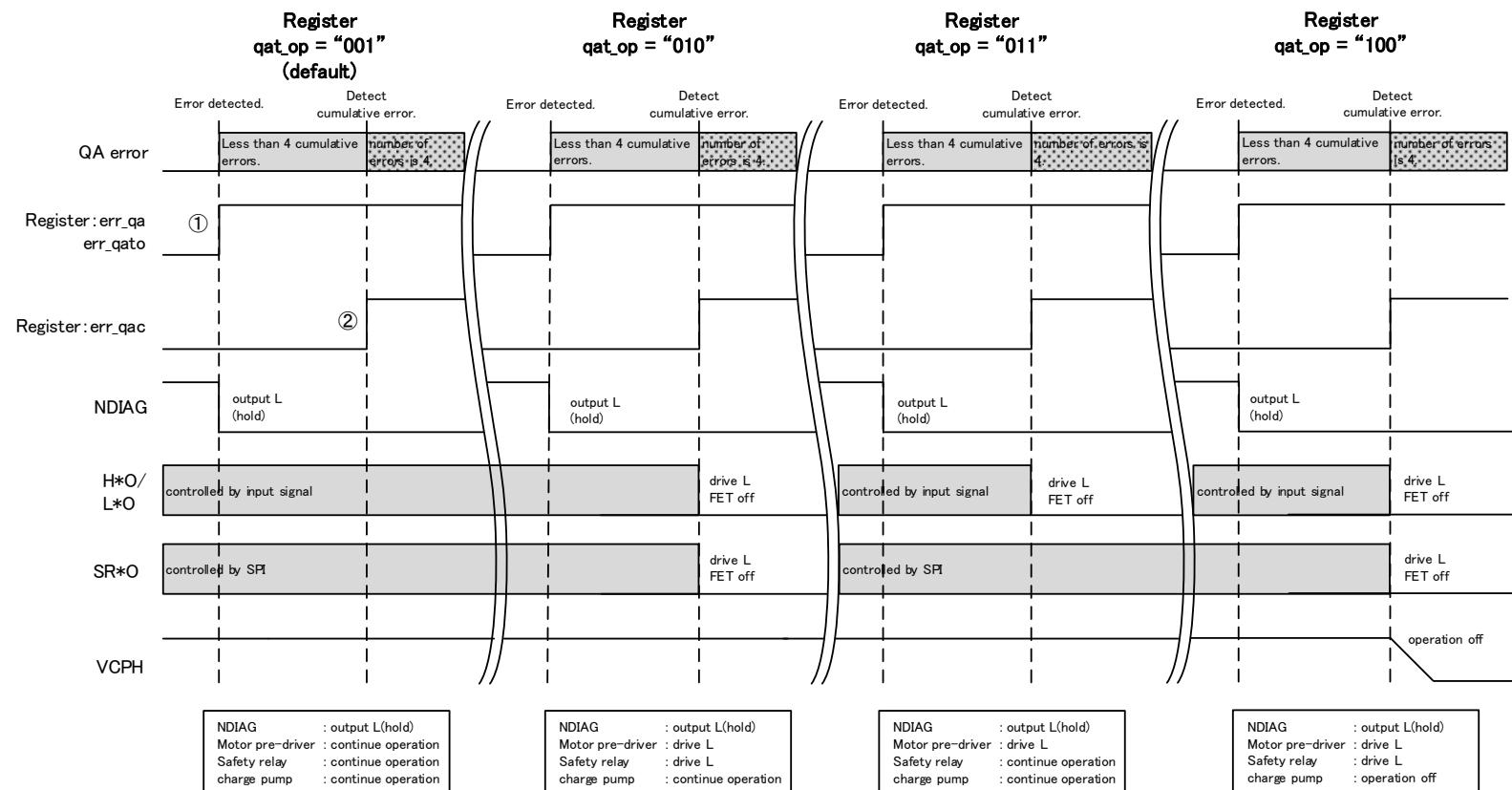

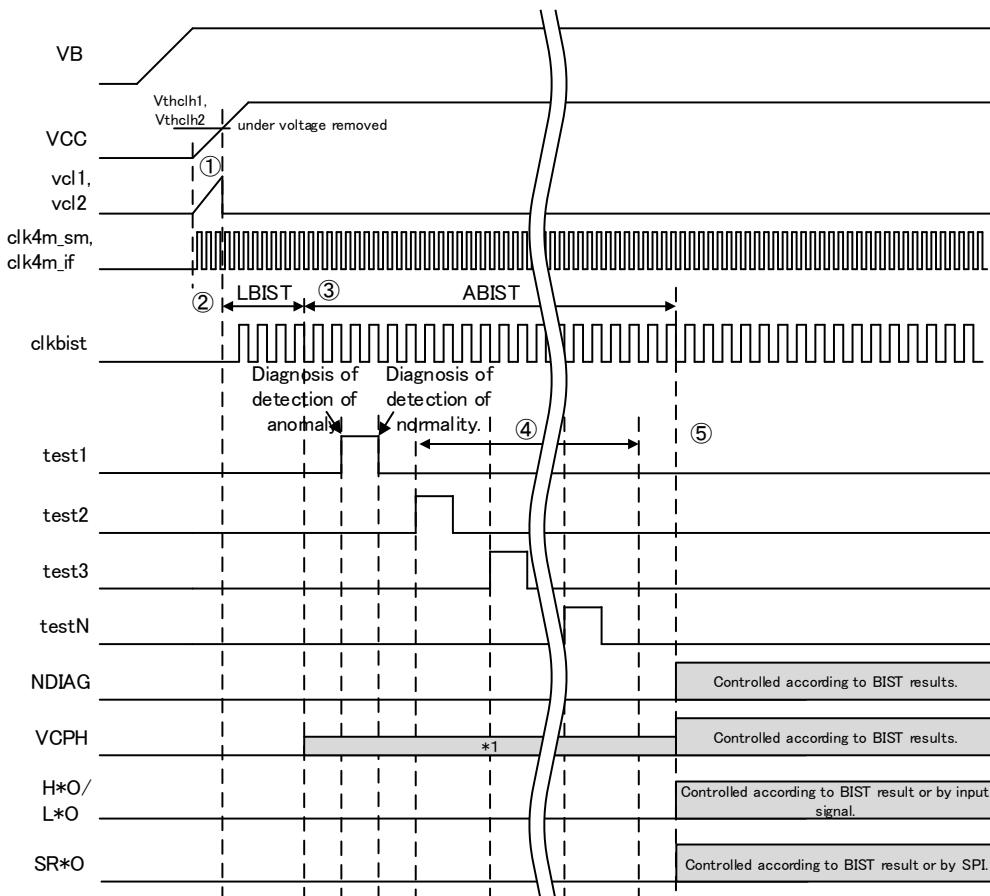

## 7.7. ABIST / LBIST 機能

IC 起動時に、各種異常検出が正常に機能しているかを診断します。

- IC 起動時、VCC 低電圧解除後に発振回路が動作を開始し、LBIST 完了後に ABIST の診断を開始します。

- LBIST が NG の場合は ABIST の診断はキャンセルされます。チャージポンプもプリドライバーも Disable 状態となるよう制御します。

- ABIST が開始すると、診断用スイッチをオンすることでコンパレーターの入力電圧を切り替え、各検出コンパレーターを反転させて診断を行います。

- 診断はクロックに同期して順次行われ、診断情報は ABIST 判定回路に入力されます。また、診断期間中は NDIAG="L"に保持されます。

- 全ての診断終了後、IC は通常動作に切り替わります。

- 診断で異常が検出されない場合、NDIAG="H"となります。

- 診断で異常が検出された場合、NDIAG="L"となり、診断情報を保持し続けます。

- 診断箇所は表 7.5-a を参照してください。

Fig. 7.7-a ABIST ブロック図(VCC 高電圧検出)

- CP\_RLY\_CTRL レジスターの en\_cp ビットの初期値は 1 であるため、ABIST が正常に終了した時点で、チャージポンプは有効となります。

表 7.7-a 回路動作真理値表(チャージポンプ回路)

| ABIST | ABSIT 結果 | ABSIT 以外の異常検出による停止 | en_cp [SPI] | 内部信号 cp_en | チャージポンプ回路 |

|-------|----------|--------------------|-------------|------------|-----------|

| 実行前   | *        | *                  | *           | L          | Disable   |

| 実行中   |          |                    |             |            |           |

| 実行後   | NG       | TRUE               | L           |            |           |

|       | OK       | FALSE              |             |            |           |

|       |          |                    | H           | H          | Enable    |

- ABIST / LBIST 実行中は内部プルアップ/ダウン抵抗に依存し  $V_{cph}=V_b$  となります。

表 7.7-b 回路動作真理値表(プリドライバー回路)

| ABIST | ABSIT 結果 | ABSIT 以外の異常検出による停止 | 内部信号 gete_en_u/v/w | プリドライバー回路 |

|-------|----------|--------------------|--------------------|-----------|

| 実行前   | *        | *                  |                    |           |

| 実行中   |          |                    |                    |           |

| 実行後   | NG       | TRUE               | L                  | Disable   |

|       | OK       | FALSE              |                    |           |

|       |          |                    | H                  | Enable    |

<ABIST 全体動作/立ち上がり動作>

> ① IC 起動

IC 起動時、Vcc の低電圧解除により、分周回路が動作開始します。

> ② LBIST 実行

分周回路が動作を開始し、LBIST を開始します。

> ③ ABIST 開始

LBIST 後、ABIST を開始します。一定時間ごとに検出コンパレーターを切り替え、検出コンパレーターが故障検出信号を正しく出力しているか診断します。

> ④ 診断

以下の各コンパレーターの診断を実施します。

VB 低電圧、VCPH 高電圧、VCC 高電圧、VCC\_OP 低電圧、VCC\_OP 高電圧、過熱。

> ⑤ ABIST 終了

全ての検出コンパレーターの診断が終了すると、IC は通常動作モードに切り替わり、チャージポンプ回路が動作を開始し、プリドライバー回路をオンすることが可能になります。また、診断結果を NDIAG へ出力します。また、診断 NG 時は、チャージポンプ回路、プリドライバー回路がオフを継続します。

Fig. 7.7-b ABIST タイミングチャート

- ABIST / LBIST 実行中は内部プルアップ/ダウン抵抗に依存し  $V_{CPH}=V_b$  となります。

- VB と VCC の立ち上げ順序はありませんが、ABIST スタート時に VB 低電圧検出及び VCC\_OP 低電圧検出が解除されておりませんと ABIST の結果が異常となります。

- また、 $V_b$  および  $V_{CC}$  のスルーレートは以下の範囲で使用してください。

- $V_b=8V/\mu s$  未満

- $V_{CC}=0.3V/\mu s$  未満

- LBIST と ABIST を合わせた実行期間は、約 2.6ms(typ.), 4.0ms(max)となります。SPI による通信は LBIST, ABIST 終了後に開始してください。

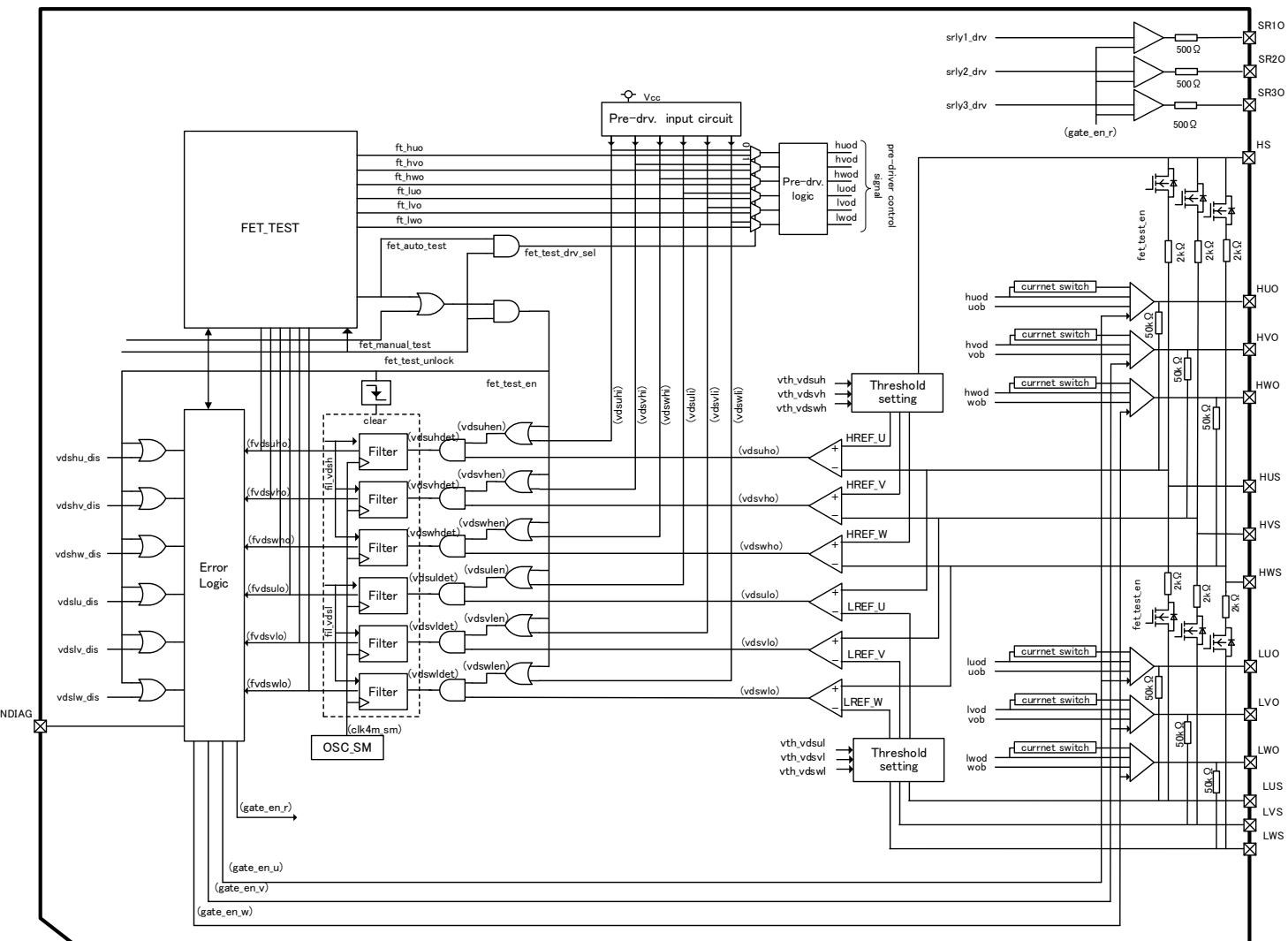

## 7.8. 外部 FET、リレーの初期診断回路

### 7.8.1. ブロック図

Fig. 7.8-a にブロック図を示します (概念図であり実際の回路を示すものではありません)。外部 FET やリレーの初期診断を実行するための検査用回路(FET\_TEST ブロック)を備えています。検査動作中は VDS 異常検出が無効となり、VDS 異常検出用の回路が外部 FET やリレーの検査(以降 FET\_TEST)に利用されます。FET\_TEST 中でも VDS 異常検出以外の要因でプリドライバーのオフ指示が到来した場合(gate\_en\_\*="L" となった場合)はプリドライバーがオフとなります。FET\_TEST 期間中モーター制御用プリドライバーの制御信号は FET\_TEST ブロックによって制御されます。リレーは常に CP\_RLY\_CTRL レジスター設定に従います。

プリドライバーがオフのときに HUS, HVS, HWS 端子を中点電位に保つための抵抗は FET\_TEST による検査が実行されているときに接続されます。

Fig. 7.8-a 外部 FET、リレーの診断回路ブロック図

## 7.8.2. 検査モード分類

表 7.8-a に検査モードの一覧を示します。fet\_test\_unlock=0 では通常動作となります。

fet\_test\_unlock=1 の期間中に fet\_manual\_test=1 とすることで、外部 FET をマニュアル操作で検査することができます。このモードではリレー駆動信号はレジスターによる制御、FET 駆動信号は入力端子による制御であり、通常動作時と同様の制御方法となります。通常動作では FET 制御用の入力端子が "H" に制御されたチャンネルだけ VDS 検出用のコンパレーター出力がノイズフィルターへ入力されますが、マニュアルテストモードでは FET 制御用の入力端子の状態とは無関係に VDS 検出用のコンパレーター出力がノイズフィルターへ入力されます。マニュアルテストモードでは VDS 検出用の回路が FET 検査に使用されるため、VDS 異常検出は無効となります。fet\_rmidonU, fet\_rmidonV, fet\_rmidonW はそれぞれ中点電圧生成用の抵抗のうち U 相、V 相、W 相を ON する制御ビットとなります。ユーザーの想定する検査方法に応じて各ビットを ON してください。同時に複数ビットを ON した場合は該当する相の抵抗が同時に ON となります。VDS 検出用のコンパレーター(フィルター後)出力を VDS COMP STAT からマイコンが読み出して期待値比較することで検査を行います。

fet\_test\_unlock=1 の期間中に fet\_test\_start ビットをセットすることで検査シーケンスが開始され fet\_auto\_test="H" となると、FET 駆動のタイミング制御と、VDS 検出コンパレーター出力結果の保存が本 IC により自動的に行われます。FET の駆動パターンは Type A, B, C ではあらかじめ想定されている規定の駆動パターンとなります、Type D ではレジスターにより任意のパターンを設定できます。VDS 異常検出用の回路が FET 検査に使用されるため、VDS 異常検出は無効となります。自動シーケンス起動中は中点電圧生成用の抵抗が全相 ON となります。Type A, B, C ではあらかじめ想定されている規定の駆動パターンで FET を駆動するため、コンパレーター出力は IC 内部で自動的に期待値比較されますが、Type D では駆動パターンがユーザーにより任意に設定できるため期待値比較もマイコンが実施します。

fet\_manual\_test と fet\_auto\_test が同時に成立した場合は fet\_auto\_test が優先されます。fet\_rmidon[U,V,W] は多ビットを同時に設定した場合は、1 に設定された相の中点電圧生成抵抗が同時に ON します。表 7.8-a における "\*" は Don't care を意味します。

表 7.8-a 検査モード一覧

| レジスター設定<br>または状態フラグ |               |                 |             |             |             |                 | 各回路要素の動作                 |                   |                    |                      |                       | 結果の<br>判定方法           | 概要   |

|---------------------|---------------|-----------------|-------------|-------------|-------------|-----------------|--------------------------|-------------------|--------------------|----------------------|-----------------------|-----------------------|------|

| fet_test_unlock     | fet_auto_test | fet_manual_test | fet_rmidonU | fet_rmidonV | fet_rmidonW | fet_test_type   | リレー<br>駆動信号              | FET<br>駆動信号       | VDS 検<br>出異常<br>検出 | 中点<br>電圧<br>生成<br>抵抗 |                       |                       |      |

| 0                   | *             | *               | *           | *           | *           | *               | *<br>マインコンによるレジスタ設定により制御 | 入力端子により制御される      | 有効                 | VDS 検出               | OFF                   | -                     | 通常動作 |

| 0                   | 0             | 0               | 0           | 0           | 0           | FET テストのロック解除状態 |                          |                   |                    |                      |                       |                       |      |

|                     |               | 1               | 0           | 0           | 0           | マインコンで<br>判断    |                          |                   |                    |                      |                       |                       |      |

|                     |               | 1               | 0           | 1           | 0           |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               | 0               | 0           | 1           | 0           |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               | *               | *           | *           | *           |                 |                          |                   |                    |                      |                       |                       |      |

| 1                   | 1             | *               | *           | *           | *           |                 |                          | 外部<br>FET の<br>診断 | U 相<br>ON          | マインコンで<br>判断         | マニュアル操作による<br>FET テスト | マニュアル操作による<br>FET テスト |      |

|                     |               |                 |             |             |             |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               |                 |             |             |             |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               |                 |             |             |             |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               |                 |             |             |             |                 |                          |                   |                    |                      |                       |                       |      |

|                     |               |                 |             |             |             |                 |                          |                   |                    |                      |                       |                       |      |

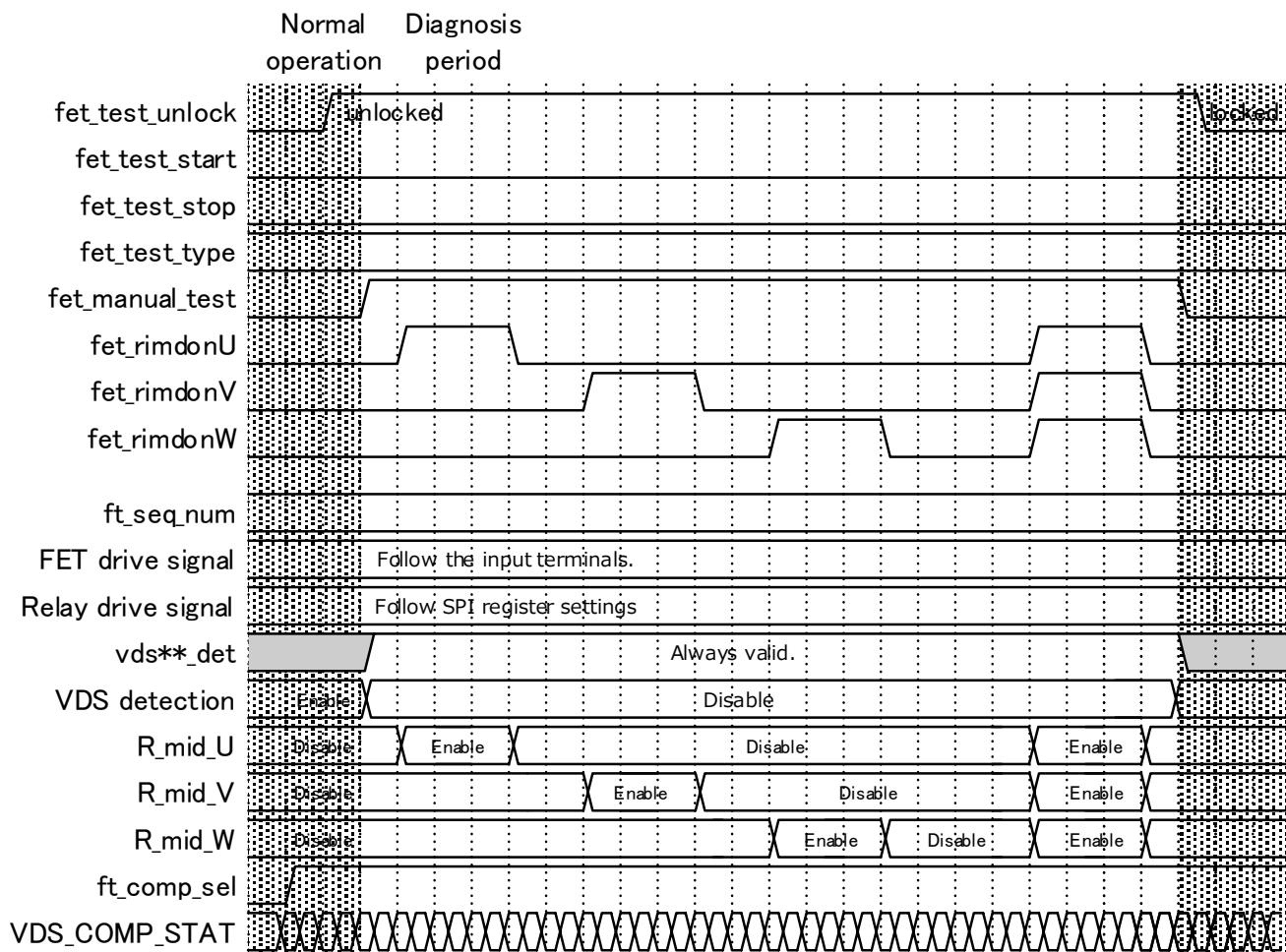

### 7.8.3. FET のマニュアル検査

FET\_TEST\_CNT2 レジスターの `fet_test_unlock="H"` を設定後に FET\_TEST\_CNT1 レジスターの `fet_manual_test="H"` とすることで FET のマニュアル検査が実行できます。FET のマニュアル検査モードでは FET の制御信号は通常動作と同じで入力端子から制御します。VDS 異常検出用の回路が FET の診断モードに変更され、FET の制御入力信号とは無関係に VDS コンパレーターの出力信号がノイズフィルターへ入力されます。VDS 検出回路が FET の診断モードに変更されるため、VDS 異常検出は無効となります。また、`fet_rmidonU`, `fet_rmidonV`, `fet_rmidonW` の 3 ビットの設定に応じて U 相、V 相、W 相の中点電圧生成用抵抗を個別に ON することができます。同時に複数ビットを ON した場合は該当する相の抵抗が同時に ON となります。`ft_comp_sel="H"` とすることで VDS\_COMP\_STAT からは VDS 検出コンパレーター(フィルター後)出力がリード可能です。マイコンでこの値を検査期間中にリードすることで期待した動作となっているかどうかを確認してください。

`fet_manual_test` と `fet_auto_test` が同時に成立した場合は `fet_auto_test` が優先され自動検査のシーケンスが開始されます。また、Fig. 7.8-b では”Normal operation”と記載してある期間がありますが、これは IC の動作が FET\_TEST のモードから抜けたという意味合いで記載となります。システムレベルで「実際にモーターを駆動する意図のある通常動作」の期間では、FET\_TEST 誤発動防止のために `fet_test_unlock="L"` としてください。

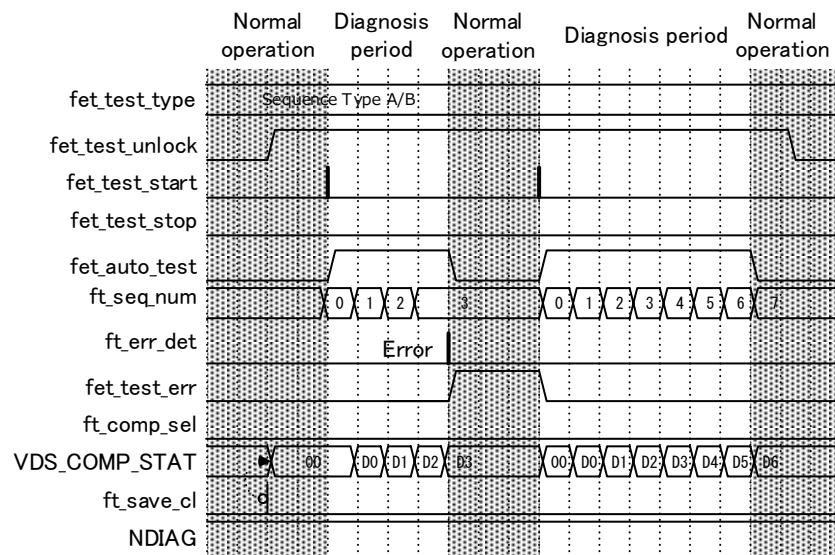

Fig. 7.8-b マニュアル検査モードでの動作波形

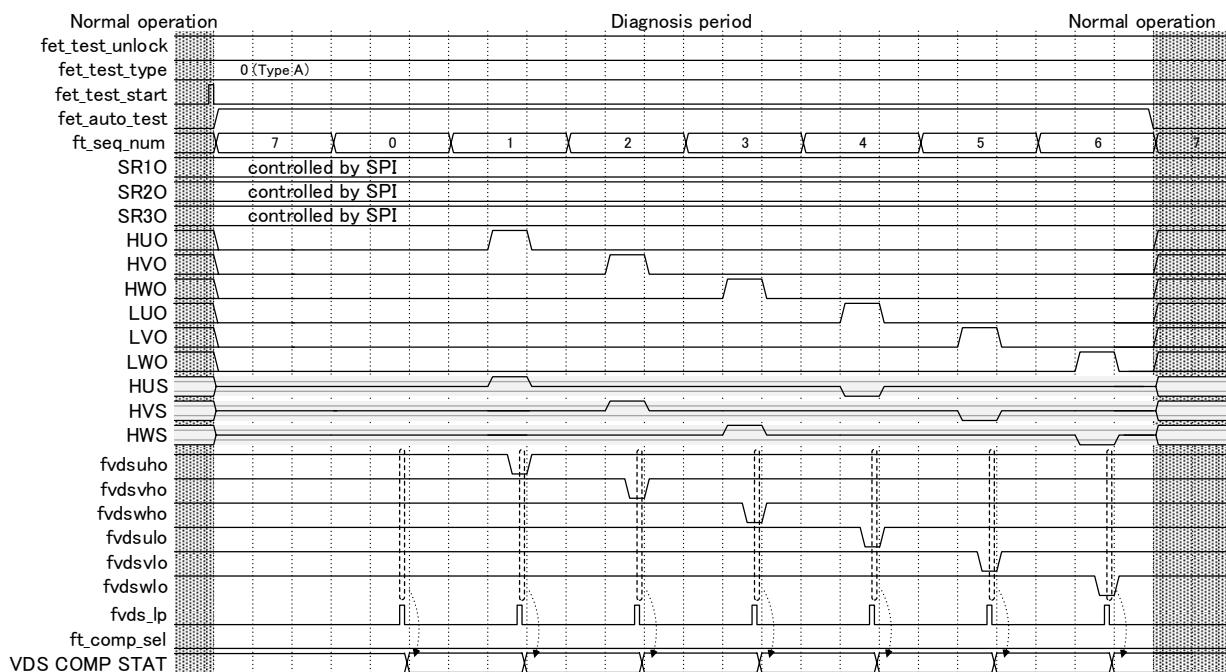

#### 7.8.4. 検査方法 Type A

モーターリレーがオフのときに検査を実行する想定です。検査を開始する前に [CP\\_RLY\\_CTRL](#) レジスターによりモーターリレーをオフに設定してから実行してください。fet\_test\_type=A を選択し、fet\_test\_unlock="H"の期間中に fet\_test\_start を設定することで Type A の検査シーケンスが開始されます。TypeA の検査シーケンスを開始すると本 IC が中点電圧生成抵抗を ON にして一定時間待機します。待機終了後本 IC がモーター制御用の全プリドライバーをオフとして期待値比較を行います。その後本 IC がモーター制御用のプリドライバーを 1 つずつ ON しながらコンパレーター出力(ノイズフィルター後)信号を期待値と比較します。検査シーケンス実行中はプリドライバーがオフのときに HUS, HVS, HWS を中点電圧に保つための抵抗が ON となります。検査シーケンス中は VDS コンパレーター(フィルター後)出力を規定のタイミングでレジスターに格納します。マイコンによって fet\_auto\_test="L"でシーケンスが終了したことを確認後に検査結果を確認してください。期待値不一致がなかった場合は fet\_test\_err="L"となります。期待値不一致があった場合は、不一致を検出した段階でシーケンスが停止しますので ft\_seq\_num をリードすることで、どの段階で不一致が発生したかを確認できます。不一致が検出されたときに保存されたコンパレーター(ノイズフィルター後)出力は ft\_comp\_sel="L"として [VDS\\_COMP\\_STAT](#) をリードすることで確認できます。期待値不一致の発生したシーケンス番号、表 7.8-b の期待値と保存されたコンパレーター出力を比較することで故障箇所を推定することができます。

Fig. 7.8-c 検査方法 Type A の動作波形

表 7.8-b 検査方法 Type A での期待値

| ft_seq_num | VDS_COMP_STAT |            |            |            |            |            |      |

|------------|---------------|------------|------------|------------|------------|------------|------|

|            | D10           | D8         | D6         | D4         | D2         | D0         | HEX  |

|            | compout_uh    | compout_ul | compout_vh | compout_vl | compout_wh | compout_wl |      |

| 0          | 1             | 1          | 1          | 1          | 1          | 1          | 0555 |

| 1          | 0             | 1          | 1          | 1          | 1          | 1          | 0155 |

| 2          | 1             | 1          | 0          | 1          | 1          | 1          | 0515 |

| 3          | 1             | 1          | 1          | 1          | 0          | 1          | 0551 |

| 4          | 1             | 0          | 1          | 1          | 1          | 1          | 0455 |

| 5          | 1             | 1          | 1          | 0          | 1          | 1          | 0545 |

| 6          | 1             | 1          | 1          | 1          | 1          | 0          | 0554 |

### 7.8.5. 検査方法 Type B

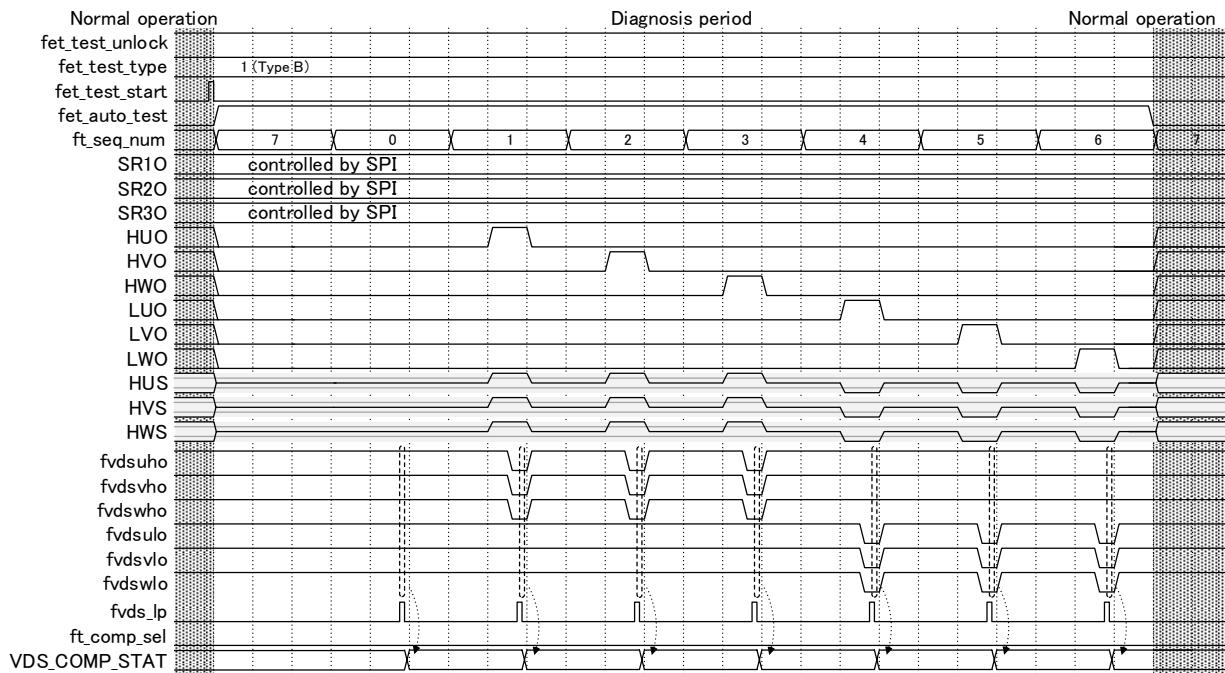

モーターリレーがオンのときに検査を実行する想定です。検査を開始する前に [CP\\_RLY\\_CTRL](#) レジスターによりモーターリレーをオンに設定してから実行してください。fet\_test\_type=B を選択し、fet\_test\_unlock="H"の期間中に fet\_test\_start を設定することで Type B の検査シーケンスが開始されます。TypeB の検査シーケンスを開始すると本 IC が中点電圧生成抵抗を ON にして一定時間待機します。待機終了後、本 IC がモーター制御用の全プリドライバーをオフとして期待値比較を行います。その後本 IC がモーター制御用のプリドライバーを 1 つずつ ON しながらコンパレーター出力(ノイズフィルター後)信号を期待値と比較します。検査シーケンス実行中はプリドライバーがオフのときに HUS, HVS, HWS を中点電圧に保つための抵抗が ON となります。検査シーケンス中は VDS コンパレーター(フィルター後)出力を規定のタイミングでレジスターに格納します。マイコンによって fet\_auto\_test="L"でシーケンスが終了したことを確認後に検査結果を確認してください。期待値不一致がなかった場合は fet\_test\_err="L"となります。期待値不一致があった場合は、不一致を検出した段階でシーケンスが停止しますので ft\_seq\_num をリードすることで、どの段階で不一致が発生したかを確認できます。不一致が検出されたときに保存されたコンパレーター(ノイズフィルター後)出力は ft\_comp\_sel="L"として [VDS\\_COMP\\_STAT](#) をリードすることで確認できます。期待値不一致の発生したシーケンス番号、表 7.8-c の期待値と保存されたコンパレーター出力を比較することで故障箇所を推定することができます。

Fig. 7.8-d 検査方法 Type B の動作波形

表 7.8-c 検査方法 Type B での期待値

|            |   | VDS_COMP_STAT |            |            |            |            |            | HEX  |

|------------|---|---------------|------------|------------|------------|------------|------------|------|

|            |   | D10           | D8         | D6         | D4         | D2         | D0         |      |

|            |   | compout_uh    | compout_ul | compout_vh | compout_vl | compout_wh | compout_wl |      |

| ft_seq_num | 0 | 1             | 1          | 1          | 1          | 1          | 1          | 0555 |

|            | 1 | 0             | 1          | 0          | 1          | 0          | 1          | 0111 |

|            | 2 | 0             | 1          | 0          | 1          | 0          | 1          | 0111 |

|            | 3 | 0             | 1          | 0          | 1          | 0          | 1          | 0111 |

|            | 4 | 1             | 0          | 1          | 0          | 1          | 0          | 0444 |

|            | 5 | 1             | 0          | 1          | 0          | 1          | 0          | 0444 |

|            | 6 | 1             | 0          | 1          | 0          | 1          | 0          | 0444 |

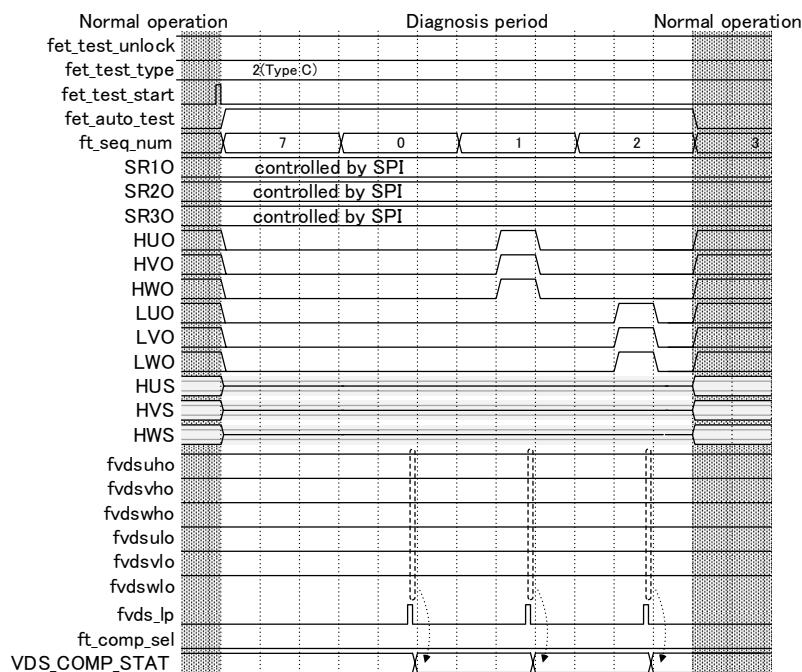

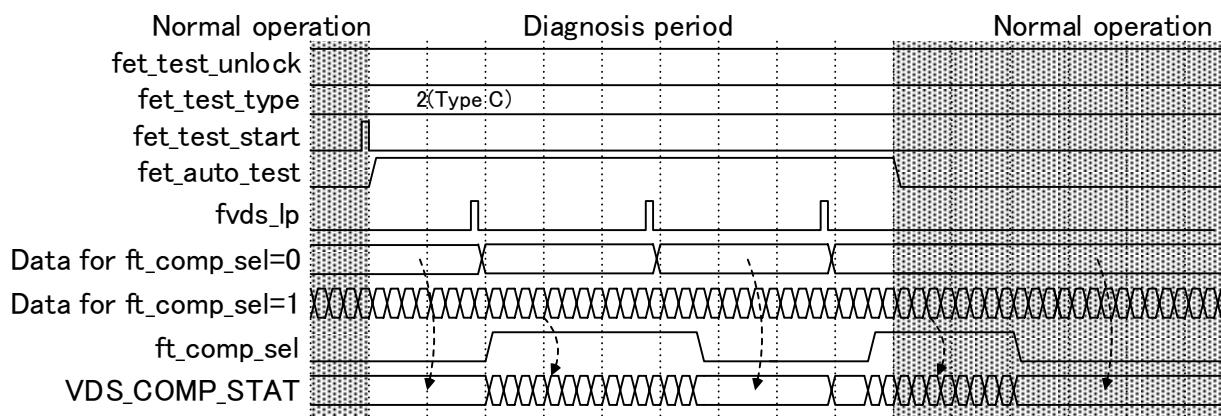

### 7.8.6. 檢査方法 Type C

モーター制御用のプリドライバーが異常検出時に停止できることを検査するときに使用する想定です。モータリレーや電源リレーを使用している場合はモーター制御用の FET が通常動作するように CP\_RLY\_CTRL レジスターでリレーの動作を設定した上で、マイコンから ALARM 端子="L"にするなどしてプリドライバーを停止させてから検査を実行させてください。この時 ALM\_CTRL の alr\_op="H"として ALARM 検出時にモーター制御用のプリドライバーのみ停止する設定とし、リレーは停止しない設定にしておきます。

`fet_test_type=C` を選択し、`fet_test_unlock="H"` の期間中に `fet_test_start` を設定することで Type C の検査シーケンスが開始されます。TypeC の検査シーケンスを開始すると本 IC が中点電圧生成抵抗を ON にして一定時間待機します。待機終了後、本 IC がモーター制御用の全プリドライバーをオフとして期待値比較を行います。その後、本 IC がモーター制御用のプリドライバーのうちハイサイド側の 3 チャンネルを同時に ON した場合と、ローサイド側の 3 チャンネルを同時に ON した場合のコンパレーター出力(ノイズフィルター後)信号を期待値と比較します。検査シーケンス実行中はプリドライバーがオフのときに HUS, HVS, HWS を中点電圧に保つための抵抗が ON となります。検査シーケンス中は VDS コンパレーター(フィルター後)出力を規定のタイミングでレジスターに格納します。マイコンによって `fet_auto_test="L"` でシーケンスが終了したことを確認後に検査結果を確認してください。期待値不一致がなかった場合は `fet_test_err="L"` となります。期待値不一致があった場合は、不一致を検出した段階でシーケンスが停止しますので `ft_seq_num` をリードすることで、どの段階で不一致が発生したかを確認できます。不一致が検出されたときに保存されたコンパレーター(ノイズフィルター後)出力は `ft_comp_sel="L"` として VDS\_COMP\_STAT をリードすることで確認できます。期待値不一致の発生したシーケンス番号、表 7.8-d の期待値と保存されたコンパレーター出力を比較することで故障箇所を推定することができます。

Fig. 7.8-e 検査方法 Type C の動作波形

表 7.8-d 検査方法 Type C での期待値

|            |   | VDS_COMP_STAT |            |            |            |            |            | HEX  |

|------------|---|---------------|------------|------------|------------|------------|------------|------|

|            |   | D10           | D8         | D6         | D4         | D2         | D0         |      |

|            |   | compout_uh    | compout_ul | compout_vh | compout_vl | compout_wh | compout_wl |      |

| ft_seq_num | 0 | 1             | 1          | 1          | 1          | 1          | 1          | 0555 |

|            | 1 | 1             | 1          | 1          | 1          | 1          | 1          | 0555 |

|            | 2 | 1             | 1          | 1          | 1          | 1          | 1          | 0555 |

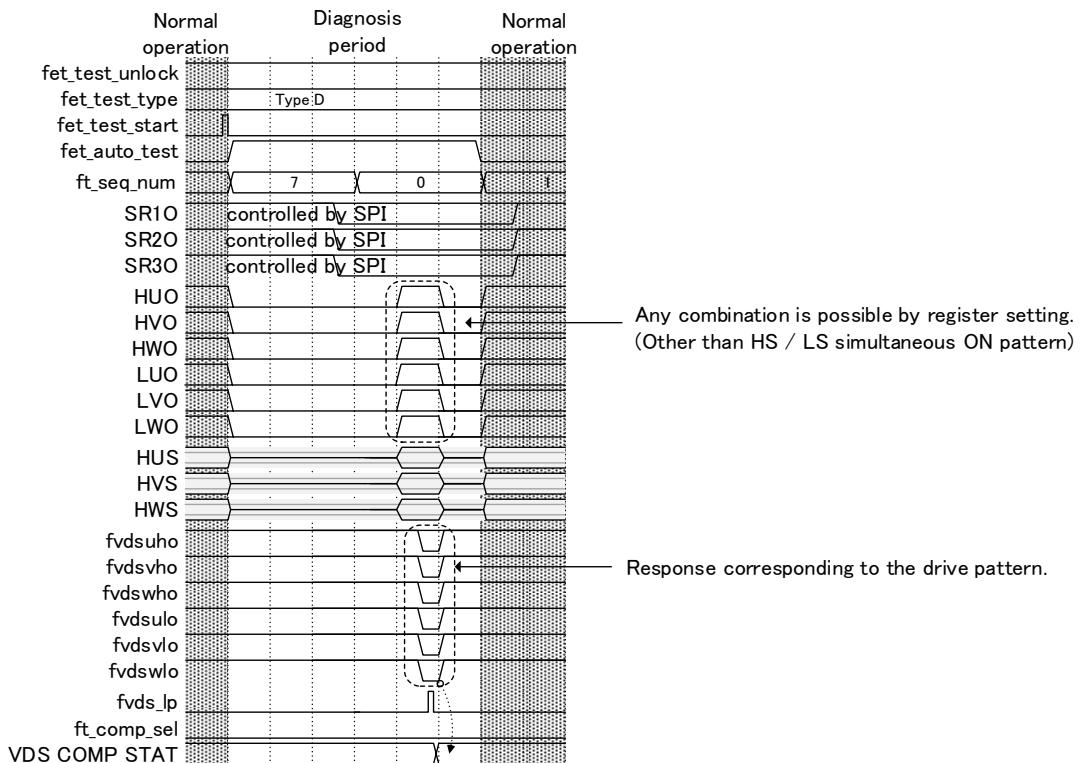

### 7.8.7. 検査方法 Type D

モーターリレーの独立性を検査するときに使用する想定ですが、FET 駆動の組み合わせは [FET\\_TEST\\_CNT2](#) レジスターで任意に設定可能ですので汎用的に使用することもできます。Type D では一度に 1 パターンの検査しか実行しません。FET 駆動の組み合わせは任意に設定可能ですが、Type D の検査シーケンスがスタートしたタイミングでの値を使用しますのでスタート前にあらかじめ所望の値をセットしてください。ハイサイド・ローサイド同時 ON の駆動パターンが設定された場合はハイサイド・ローサイドともにオフとして扱われます。IC では期待値比較を行いませんが検査時のコンパレーター出力(ノイズフィルター後)信号を 6 チャンネル分リード可能です。検査シーケンス実行中はプリドライバーがオフのときに HUS, HVS, HWS を中点電圧に保つための抵抗が ON となります。

`fet_test_type=D` を選択し、`fet_test_unlock="H"` の期間中に `fet_test_start` を設定することで Type D の検査シーケンスが開始されます。Type D の検査シーケンスを開始すると本 IC が中点電圧生成抵抗を ON にして一定時間待機します。待機終了後、`FET_TEST_CNT2` レジスターで設定された駆動パターンで FET を駆動します。検査シーケンス中は VDS コンパレーター(ノイズフィルター後)出力を規定のタイミングでレジスターに格納します。マイコンによって `fet_auto_test="L"` でシーケンスが終了したことを確認後に検査結果を確認してください。検査中に保存されたコンパレーター(ノイズフィルター後)出力は `ft_comp_sel="L"` として [VDS\\_COMP\\_STAT](#) をリードすることで確認できますので、マイコンで期待通りの動作をしているか確認してください。

Fig. 7.8-f 検査方法 Type D の動作波形

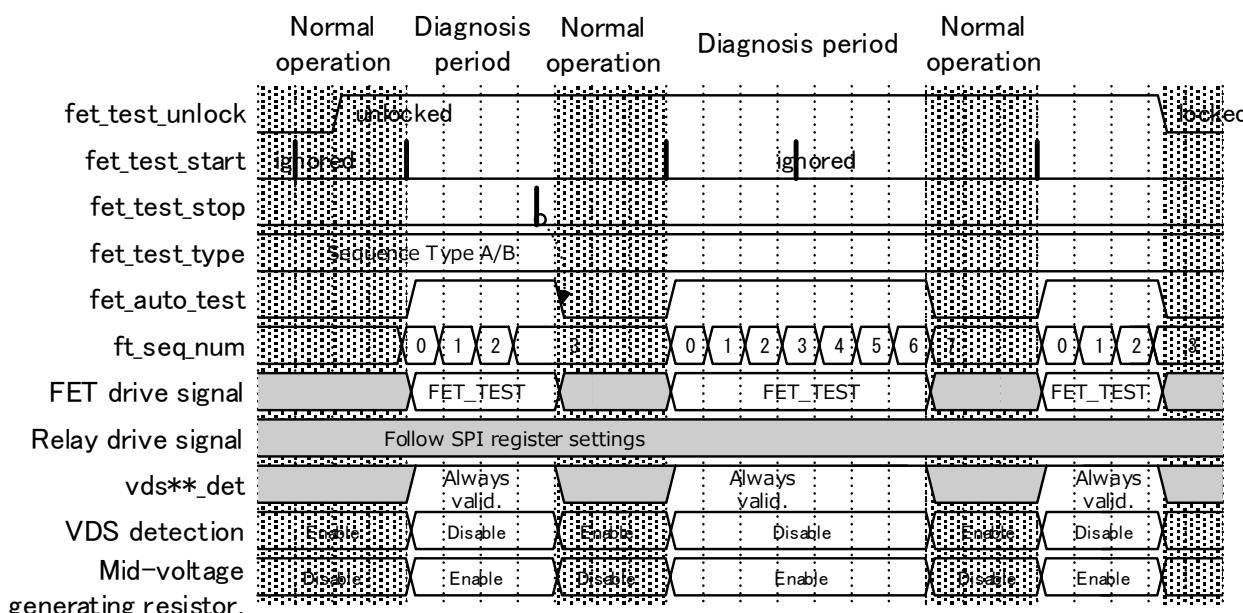

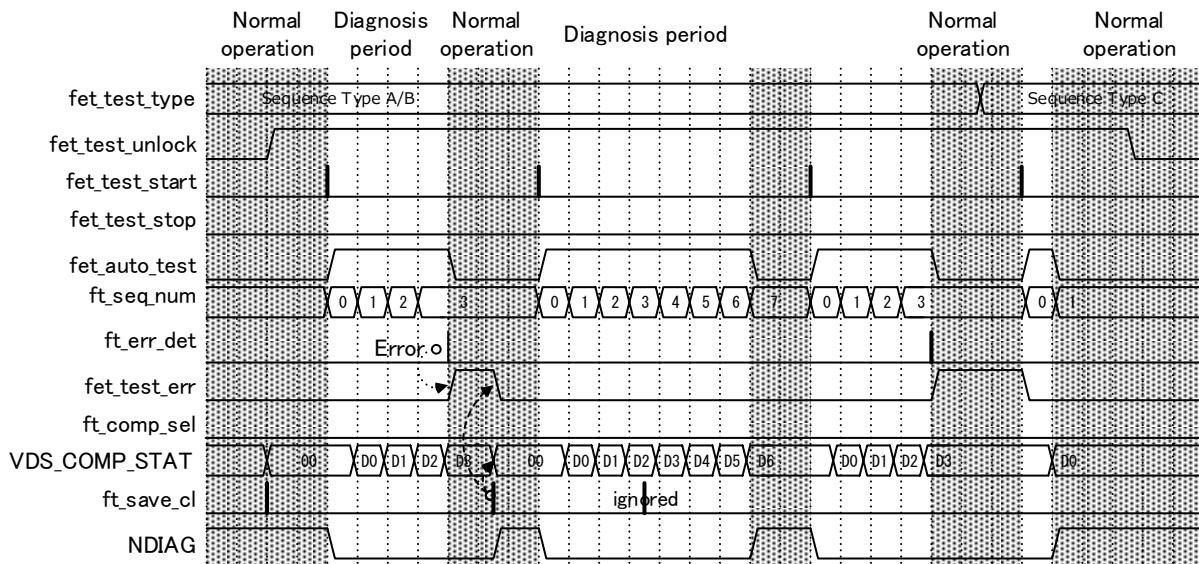

### 7.8.8. 検査シーケンスの開始と終了

`fet_test_unlock="H"`を設定後に `fet_test_start` ビットを設定することで検査が開始されます。Fig. 7.8-g では”Normal operation”と記載してある期間がありますが、これは IC の動作が FET\_TEST のモードから抜けたという意味合いでの記載となります。システムレベルで「実際にモーターを駆動する意図のある通常動作」の期間では、FET\_TEST 誤発動防止のために `fet_test_unlock="L"` としてください。`fet_test_start` は検査実行中に受領しても無視されます。FET\_TEST 実行中、モーター制御用のプリドライバーは FET\_TEST ブロックにより制御されます。FET\_TEST の開始時および終了時に意図しない FET の駆動をさせないように、FET\_TEST を実行する前に各 FET の制御信号(HUI, HVI, HWI, LUI, LVI, LWI 端子入力)を FET がオフとなるようにマイコンから制御しておいてください。

検査の停止は `fet_test_stop` と、`fet_test_unlock="L"` の二通りの方法があります。

`fet_test_stop` で停止させた場合は、実行中のステップが完了したタイミングで停止します(検査終了後の `ft_seq_num` は最後に検査した検査ステップの番号となります)。ただし、各検査シーケンスで最後の検査ステップの段階で `fet_test_stop` が受領された場合は無視されます(Type A, Type B の検査シーケンスでの `ft_seq_num=6h`、Type C の検査シーケンスでの `ft_seq_num=2h`、Type D の検査シーケンス)。

`fet_test_unlock="L"` の場合は実行中の検査ステップが終了したかどうかに関わらず `fet_test_unlock="L"` を受領した時点で強制的に通常動作状態に戻します(`ft_seq_num` と保存されたコンパレーター出力結果の関係性は保証されません)。

VDS 検出用ノイズフィルターへの入力信号 `vds**_det` は通常動作期間では該当のチャンネルが ON に制御された期間だけ有効となり VDS 電圧の異常検出に利用されますが、FET\_TEST 期間中は FET 検査のために常に有効となります。ただし、FET\_TEST 期間中は VDS 異常検出自体が無効となりますので FET\_TEST 期間中に VDS 異常が検出されることはありません。FET\_TEST 実行期間中は中点電圧生成用の抵抗が ON となります。

Type A / Type B の検査方法では、期待値不一致がなければ `ft_seq_num=7h`、Type C の検査方法では `ft_seq_num=3h` で終了します。`fet_auto_test` は FET\_TEST 実行中に”H”となるリード可能なレジスターです。

Fig. 7.8-g FET 検査の開始と終了に関する動作波形

### 7.8.9. 期待値不一致検出時の動作

Type A / Type B / Type C の検査では検査中に期待値との比較を行います。期待値不一致が発生した場合には検査シーケンスが停止し、`ft_test_err="H"`がセットされます。このとき `ft_seq_num` には期待値不一致となった検査シーケンスの番号が保存されています。`ft_comp_save(VDS_COMP_STAT)` の `ft_comp_sel="L"` 時のデーターには最後に実行された検査での(期待値不一致となった)コンパレーター出力(ノイズフィルター後)信号が 6 チャンネル分保存されています。マイコンはこれらの値をリードすることで、どの検査ステップのどの出力が不一致となったかを確認することができます。`ft_test_err` レジスターと `ft_comp_save` レジスターは新たな検査がスタートしたタイミングと `ft_save_cl` ビットが設定されたときにクリアされます。

Fig. 7.8-h 期待値不一致検出時の動作

### 7.8.10. リードデーターの選択

[VDS\\_COMP\\_STAT](#) でリードするデーターは `ft_comp_sel` ビットによって、自動シーケンス時に保存されたデーターと、VDS コンパレーター出力の現在の値から選択可能です。`ft_comp_sel` はどちらのデーターをリードするかを選択するのみの設定ビットであり、自動シーケンスで保存されるデーターには影響を与えません。自動シーケンス中に必ず `ft_comp_sel="L"` にしなければならないという制約はありません。自動シーケンスで保存された結果を確認する時点で `ft_comp_sel="L"` とすれば十分です。

Fig. 7.8-i `ft_comp_sel` によるリードデーターの選択

### 7.8.11. FET 検査時の NDIAG への出力

`ft_ndiag_sel="H"`とすることで、FET\_TEST 実行中(`fet_auto_test="H"`の期間)と、検査中に期待値不一致が検出された場合(`fet_test_err="H"`の期間)に NDIAG="L"とすることができます。`fet_test_err` は新たな検査がスタートしたタイミングと `ft_save_cl` ビットによりクリアされます。

Fig. 7.8 j 検査時に NDIAG へ出力する場合の動作波形

エラーがない場合の FET 検査時間は表 7.8-e のようになります。`ft_ndiag_sel="H"`を設定した場合 NDIAG が"0"の期間の長さと同一です。

表 7.8-e FET 検査時間

| 検査タイプ  | Typ.         | Max          |

|--------|--------------|--------------|

| Type A | $1024 \mu s$ | $1576 \mu s$ |

| Type B | $1024 \mu s$ | $1576 \mu s$ |

| Type C | $512 \mu s$  | $788 \mu s$  |

| Type D | $256 \mu s$  | $394 \mu s$  |

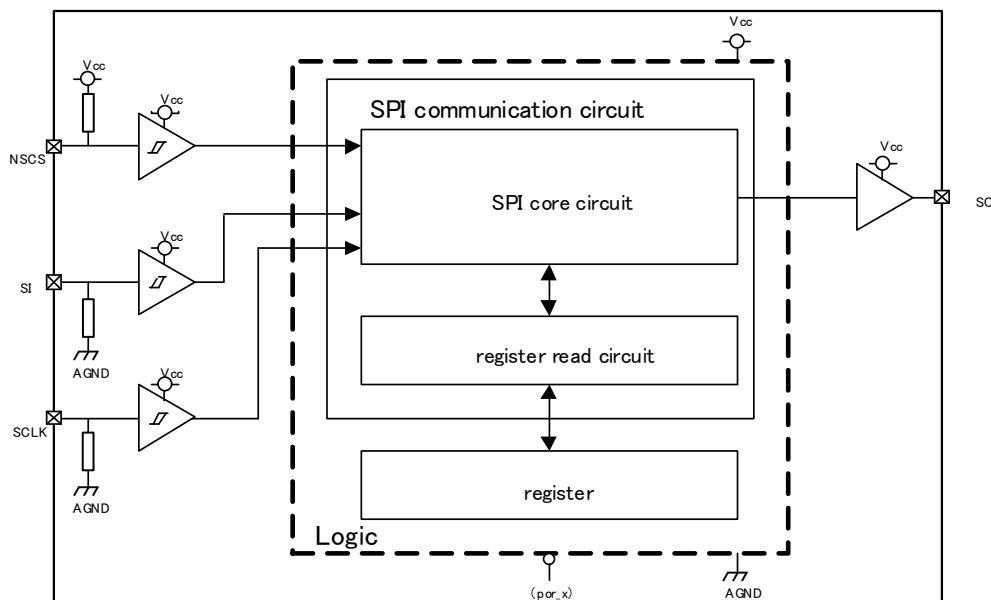

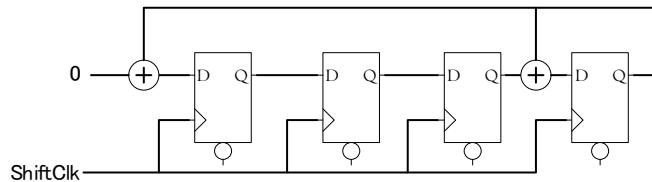

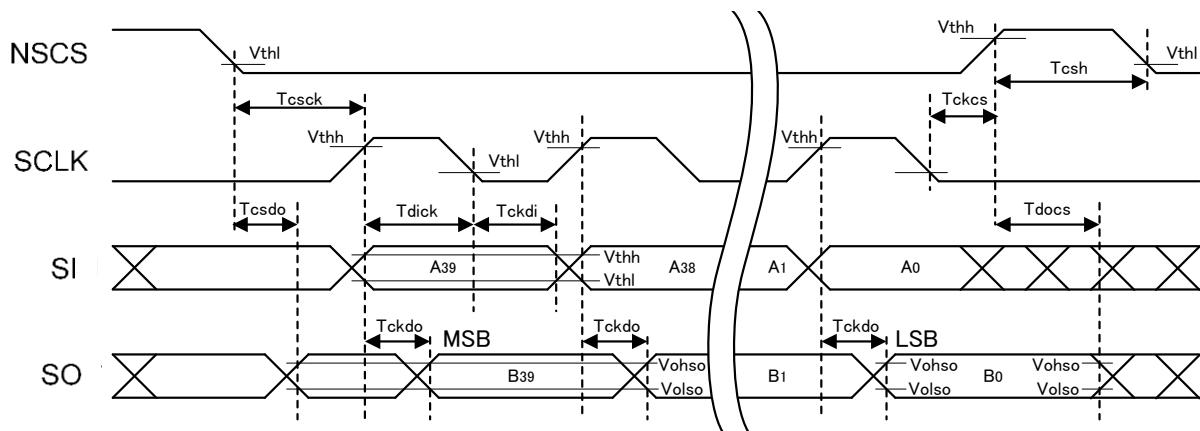

## 7.9. SPI 通信回路

SPI 通信回路は SPI コア回路、レジスタリード回路ブロックで構成されています。

NSCS="L"のときのみマイコンとの通信が可能となります。

クロックの立ち上がりエッジでマイコンは SI にデーターを書き込み、次の立ち下がりエッジで IC がデーターを読み取ります。

また、クロックの立ち上がりエッジで IC は SO にデーターを出力し、次の立ち下がりエッジでマイコンがデーターを読み取ります。

SI はマイコンからのデータビットを MSB から LSB の順に受信します。

SO はマイコンへデータビットを MSB から LSB の順に送信します。

出力はプシュップル構成で、NSCS="H"のときにはハイインピーダンスとなります。

また、IC 内部で NSCS 端子は抵抗プルアップ、SCLK、SI 端子は抵抗プルダウンされています。

Fig. 7.9-a SPI 通信回路ブロック図

### 7.9.1. SPI 通信動作

NSCS="L"の時 SCLK に同期してシリアルデータを送受信します。NSCS="H"の場合 SO 出力はハイインピーダンスとなります。フレーム長は 32bit です。機能としてはリード動作、ライト動作の 2 種類があり、“RW”bit(Address[7])によりライト/リード動作の選択が可能です。Address[0]はアドレス選択には使用されません。“Dummy”bit は動作に影響しません。

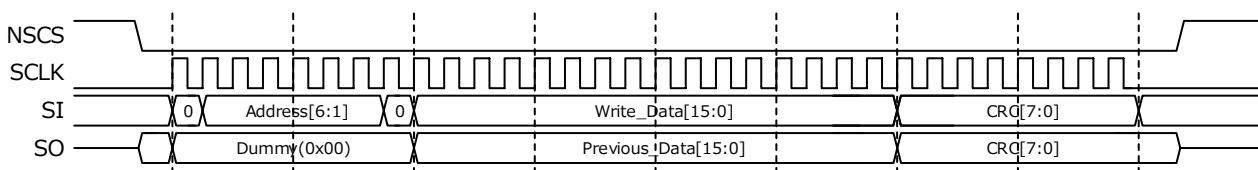

<ライト動作>

ライト動作時のデーターフォーマットを Fig. 7.9-b に示します。

SI はアドレス指定ビット Address[7:0]、書き込みデーター指定ビット Write\_Data[15:0]、データーチェック用ビット CRC[7:0]により構成されます。書き込み時は Address[7]=0 としてアドレス指定します。Address[0]はアドレス選択には使用されません。CRC の対象範囲は Address[7:0]と Write\_Data[15:0]となります。

SO は SI におけるアドレス設定期間 8bit でダミーデーター(0x00)が出力された後、SI によって設定されたアドレスのデーターを Previous\_Data[15:0]に出力します。このとき SO 出力に使用されるアドレスデーターは CRC によるチェックが実施されていません。ライトオンリーのレジスターの場合は SO からの出力データーはゼロとなります。Previous\_Data[15:0]は Address[7:0]によって書き込みが指示されたレジスターの Write\_Data[15:0]が書き込まれる直前のデーターとなります。CRC の対象範囲は Previous\_Data[15:0]となります。

ライト後に必ずデーターをリードして正しいデーターがライトされていることを確認してください。また、レジスターの存在しない空きビットはリード時には 0 としてリードされます。

Fig. 7.9-b ライト動作時データーフォーマット

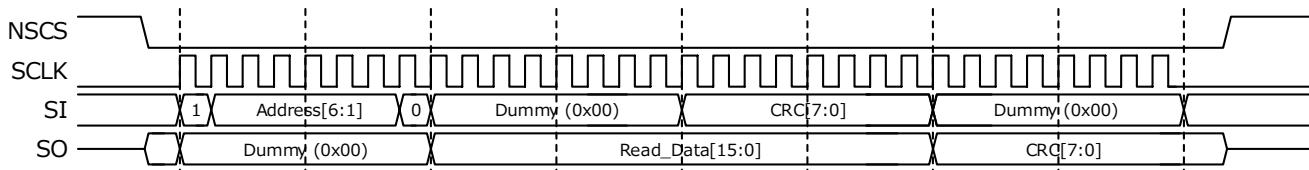

<リード動作>

リード動作時のデーターフォーマットを Fig. 7.9-c に示します。

SI はアドレス指定ビット Address[7:0]、ダミーデーターDummy[7:0]、データーチェック用ビット CRC[7:0]により構成されます。読み出すときは Address[7]=1 としてアドレス指定します。Address[0]はアドレス選択には使用されません。CRC の対象範囲は Address[7:0]となります。

SO は SI におけるアドレス設定期間でダミーデーター(0x00)が出力された後、SI によって設定されたアドレスのデーターを Read\_Data[15:0]に出力します。レジスターの存在しない空きビットはリード時に 0 としてリードされます。CRC の対象範囲は Read\_Data[15:0]となります。

Fig. 7.9-c リード動作時データーフォーマット

### 〈CRC エラー判定〉

データー通信が正しく行われたことを確認するために CRC によるエラー判定を行います。生成多項式は、以下となります。初期値は 0xFF です。

$$x^8 + x^4 + x^3 + x^2 + 1$$

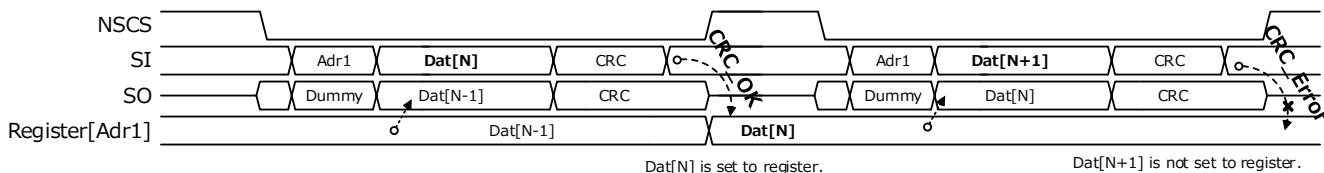

CRC エラーとなった場合は以下動作となります。

### (1) ライト動作時

CRC エラーの場合データーは IC に書き込まれません。

Fig. 7.9-d ライト動作時 CRC エラー

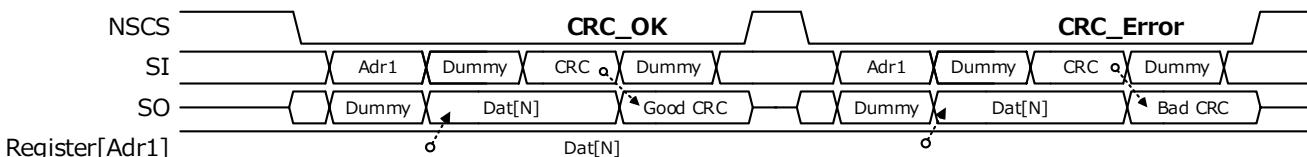

## (2) リード動作時

CRC エラーの場合同フレーム内の SO から故意に誤った CRC を返します。これにより、マイコン側で CRC エラーを検

Fig. 7.9-e リード動作時 CRC エラー

出します。

### <Vcc 低下検出時>

Vcc 低下検出時は SPI 通信ができません

Vcc 低下検出時は SO が“0”に固定されます(ライト動作時、リード動作時共)

<LBIST 中>

SPI 通信ができません

### <Fail 判定>

SPI 通信で次の場合 IC が通信エラーと判定

### (1) レジン

れます(ライトアドレスがアサインされていないレジスターに書き込みした場合は、ICに書き込みされません)。Address[0]

は無視されます。

- ライト時の SO データは Dummy="0", Previous\_Data="0" となります。またレジスターへの書き込みが行われないため、レジスターデータは前の状態(あるいはデフォルト値)を保持します

- リード時の SO データは "0" となります

(2) フレーム長が 32bit 以外の場合は、通信エラーとなります

- ライト時フレーム長が 32bit 以外の場合は、IC に書き込みされません

- リード時フレーム長が 32bit 未満の場合は、NSCS="H" の時点で SO が HiZ となります。

- リード時フレーム長が 33bit 以上の場合は、送信フレーム 33bit 以降は SO が "0" 出力となります

(3) CRC エラーを検出した場合は、通信エラーとなります

- ライト時 CRC エラーを検出した場合は、IC に書き込みされません

- リード時 CRC エラーを検出した場合は、故意に誤った CRC を返します

- 故意に誤った CRC とは、SO から出力される Read Data[15:0]に対する正常な CRC の値を全 bit 反転した値です

## 7.9.2. QA タイマー機能