Toshiba BiCMOS Linear Integrated Circuits — silicon monolithic

# TB9083FTG

Automotive GATE-driver for Brushless motor

## 1. INTRODUCTION

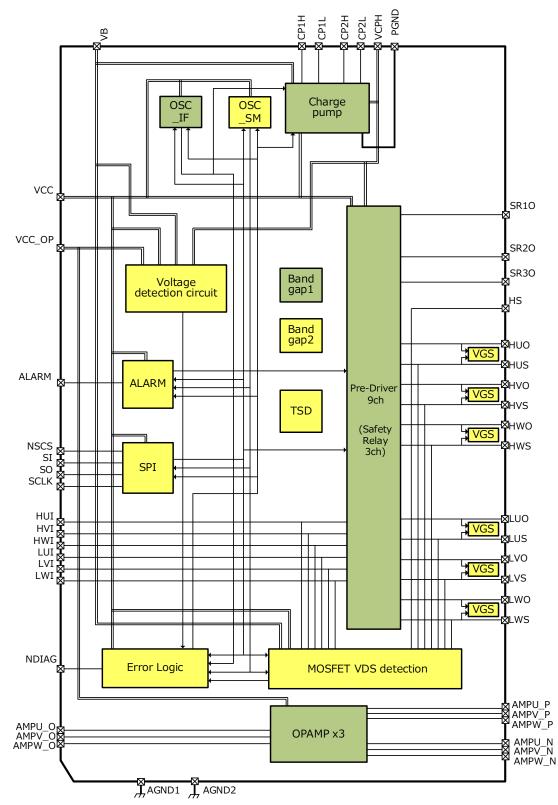

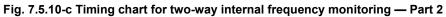

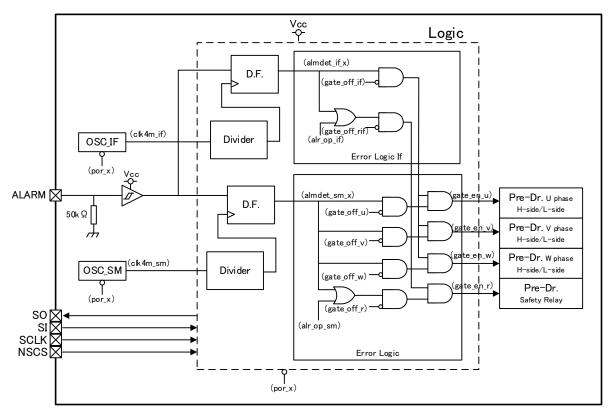

The TB9083FTG is a pre-driver IC for brushless motors in vehicle application.

It features a built-in safety relay pre-driver in addition to the threephase pre-driver.

It also has a charge pump, a motor current detector circuit, an oscillator circuits and an SPI communication circuit.

It has multiple error detection features. Trigger threshold, response action and other settings are modified via the SPI.

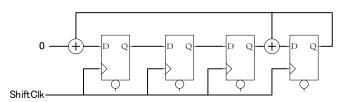

The TB9083FTG is also equipped with ABIST/LBIST for testing and evaluation of the error detection functions.

weight: 137.9 mg (typ.)

## 2. APPLICATIONS

Used mainly on EPS, powered brakes and pumps

## 3. FEATURES AND BENEFITS

- Three-phase pre-driver PWM control up to 20 kHz

- Fail-safe relay pre-driver

- Built-in charge pump circuit

- Built-in current detector circuit

- Error detection functionality: undervoltage (VB, VCC, VCC\_OP), overvoltage (VCC, VCC\_OP, VCPH, external MOSFET VGS), overtemperature, external MOSFET VDS detector

- Built-in ABIST / LBIST

- AEC-Q100 and AEC-Q006 Qualified

- Operating voltage range VB: 4.5 to 28 V, VCC: 3.0 to 5.5 V

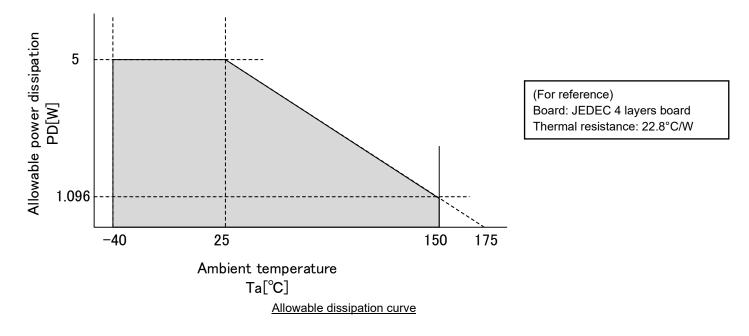

- Operating temperature range Ta: -40°C to 150°C, Tj: -40°C to 175°C

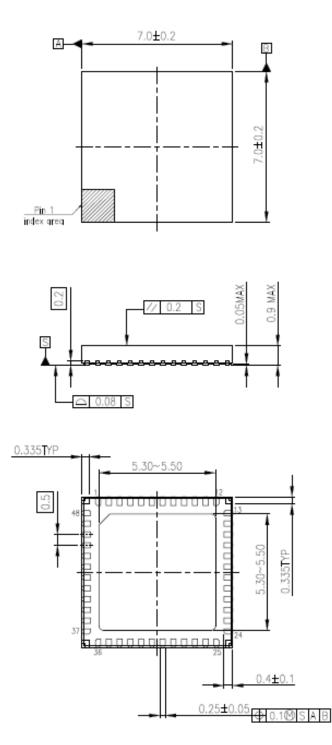

- Package P-VQFN48-0707-0.50-005 (Wettable flank, 0.5 mm pitch)

- Functional safety

•

- Developed according to ISO 26262 2nd Ed. ASIL-D Capable.

- □ Safety manual and safety evaluation report

- □ Redundancy and built-in ABIST/LBIST

- □ SPI interface with CRC check

The product(s) is/are compatible with RoHS regulations (EU directive 2011 / 65 / EU) as indicated, if any, on the packaging label ("[[G]]/RoHS COMPATIBLE", "[[G]]/RoHS [[Chemical symbol(s) of controlled substance(s)]]", "RoHS COMPATIBLE" or "RoHS COMPATIBLE, [[Chemical symbol(s) of controlled substance(s)]]>MCV").

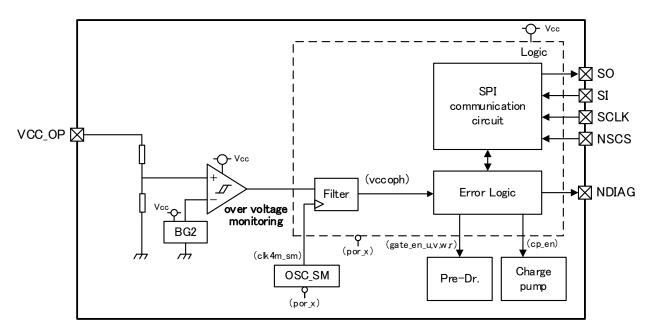

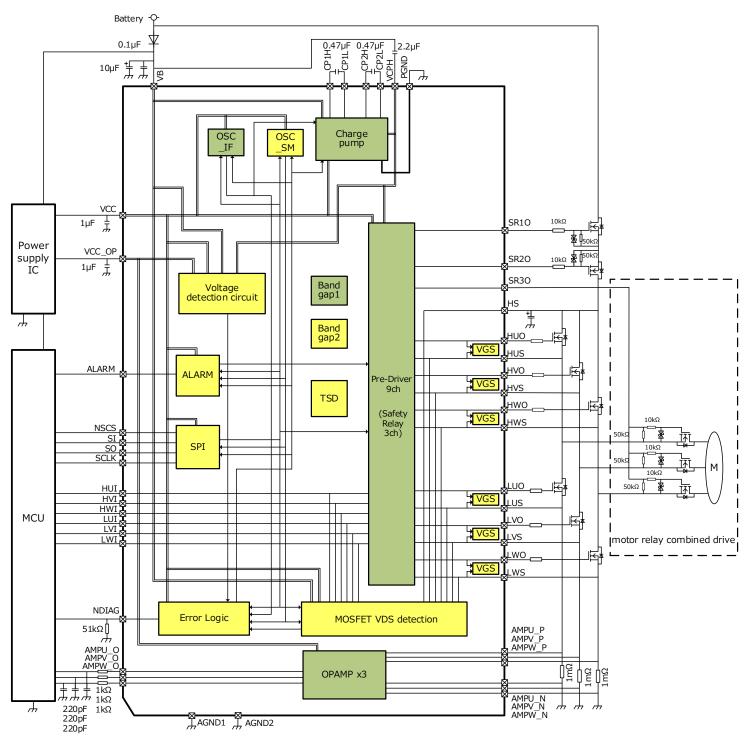

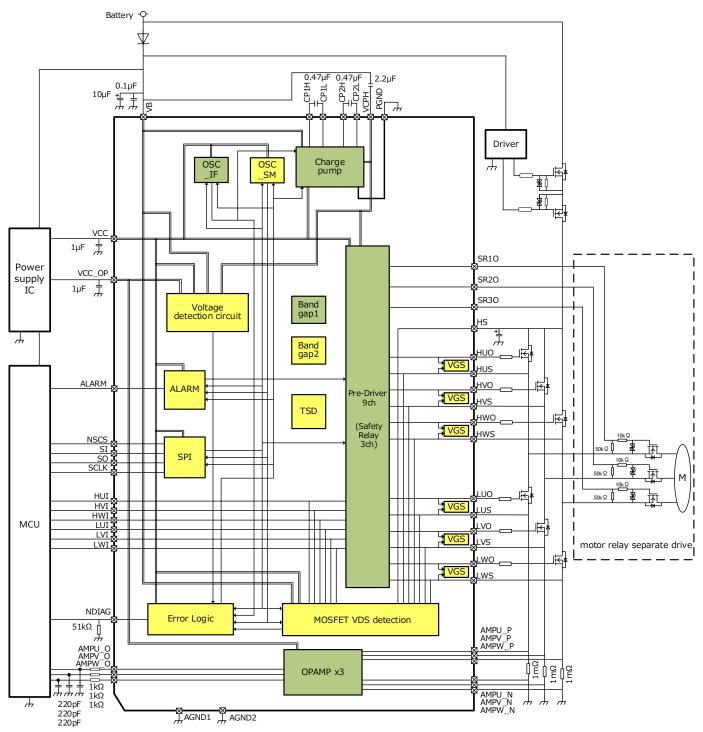

## 4. BLOCK DIAGRAM

Note Functional blocks and wiring scheme have been simplified for the purpose of clarity (including individual block diagrams)

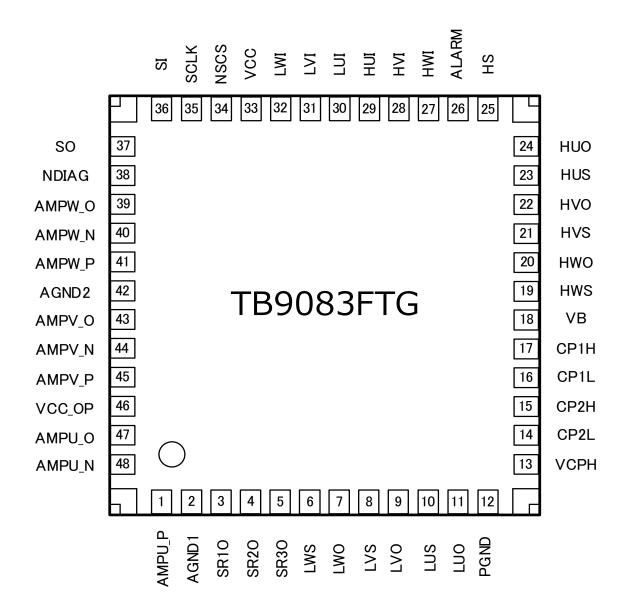

## 5. Terminal layout (top view)

## 6. Terminals

| Pin No         | Name                       | I/O             | Description                                                                                              | Pull-up/down<br>resistor          | Remark                                                                                                      |

|----------------|----------------------------|-----------------|----------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1              | AMPU_P                     | IN              | Current sense amplifier positive input for U phase                                                       | —                                 | -                                                                                                           |

| 2              | AGND1                      | GND             | GND 1 for analog circuits                                                                                | -                                 | _                                                                                                           |

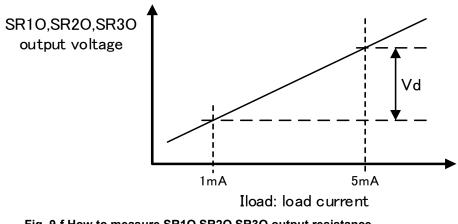

| 3              | SR10                       | OUT             | Safety relay 1 output                                                                                    | -                                 | SPI setting                                                                                                 |

| 4              | SR2O                       | OUT             | Safety relay 2 output                                                                                    | _                                 | SPI setting                                                                                                 |

| 5              | SR3O                       | OUT             | Safety relay 3 output                                                                                    | _                                 | SPI setting                                                                                                 |

| 6              | LWS                        | IN              | Pre-driver reference input for W phase low side (source)                                                 | _                                 | _                                                                                                           |

| 7              | LWO                        | OUT             | Pre-driver output for W phase low side                                                                   | Pull-down to LWS                  | _                                                                                                           |

| 8              | LVS                        | IN              | Pre-driver reference input for V phase low side (source)                                                 | _                                 | _                                                                                                           |

| 9              | LVO                        | OUT             | Pre-driver output for V phase low side                                                                   | Pull-down to LVS                  | _                                                                                                           |

| 10             | LUS                        | IN              | Pre-driver reference input for U phase low side (source)                                                 | _                                 | _                                                                                                           |

| 11             | LUO                        | OUT             | Pre-driver output for U phase low side                                                                   | Pull-down to LUS                  | _                                                                                                           |

| 12             | PGND                       | GND             | Power GND                                                                                                |                                   | _                                                                                                           |

| 13             | VCPH                       | Power supply    | Charge pump output voltage                                                                               | Pull-down to VB                   | _                                                                                                           |

| 14             | CP2L                       | OUT             | Charge pump output 2                                                                                     | -                                 |                                                                                                             |

| 15             | CP2H                       | 1/0             | Charge pump drive output 2                                                                               | _                                 | _                                                                                                           |

| 16             | CP1L                       | OUT             | Charge pump output 1                                                                                     | _                                 |                                                                                                             |

| 17             | CP1H                       | 1/0             | Charge pump drive output 1                                                                               |                                   |                                                                                                             |

|                |                            | Power           |                                                                                                          |                                   |                                                                                                             |

| 18             | VB                         | supply          | VB input                                                                                                 |                                   | _                                                                                                           |

| 19             | HWS                        | IN              | Pre-driver reference input for W phase high side (source)                                                | Pull-up to HS<br>Pull-down to LWS | Pull-up and pull-down<br>resistors can be<br>connected only in the<br>external FET test mode<br>(FET TEST). |

| 20             | HWO                        | OUT             | Pre-driver output for W phase high side                                                                  | Pull-down to HWS                  | -                                                                                                           |

| 21             | HVS                        | IN              | Pre-driver reference input for V phase high side (source)                                                | Pull-up to HS<br>Pull-down to LVS | Pull-up and pull-down<br>resistors can be<br>connected only in the<br>external FET test mode<br>(FET_TEST). |

| 22             | HVO                        | OUT             | Pre-driver output for V phase high side                                                                  | Pull-down to LVS                  | _                                                                                                           |

| 23             | HUS                        | IN              | Pre-driver reference input for U phase high side (source)                                                | Pull-up to HS<br>Pull-down to LUS | Pull-up and pull-down<br>resistors can be<br>connected only in the<br>external FET test mode<br>(FET_TEST). |

| 24             | HUO                        | OUT             | Pre-driver output for U phase high side                                                                  | Pull-down to HUS                  |                                                                                                             |

| 25             | HS                         | IN              | VDS sense input for external high side MOSFET                                                            | -                                 |                                                                                                             |

| 26             | ALARM                      | IN              | Enable input for pre-driver                                                                              | Pull-down to GND                  | _                                                                                                           |

| 27             | HWI                        | IN              | Pre-driver input for W phase high side                                                                   | Pull-down to GND                  | _                                                                                                           |

| 28             | HVI                        | IN              | Pre-driver input for V phase high side                                                                   | Pull-down to GND                  | _                                                                                                           |

| 29             | HUI                        | IN              | Pre-driver input for U phase high side                                                                   | Pull-down to GND                  | _                                                                                                           |

| 30             | LUI                        | IN              | Pre-driver input for U phase low side                                                                    | Pull-down to GND                  | _                                                                                                           |

| 31             | LVI                        | IN              | Pre-driver input for V phase low side                                                                    | Pull-down to GND                  | _                                                                                                           |

| 32             | LWI                        | IN              | Pre-driver input for W phase low side                                                                    | Pull-down to GND                  | -                                                                                                           |

| 33             | VCC                        | Power supply    | 5V/3.3V supply input                                                                                     | _                                 | _                                                                                                           |

| 34             | NSCS                       | IN              | SPI chip select                                                                                          | Pull-up to VCC                    | _                                                                                                           |

| 35             | SCLK                       | IN              | SPI clock input                                                                                          | Pull-down to GND                  | _                                                                                                           |

| 36             | SI                         | IN              | SPI input                                                                                                | Pull-down to GND                  | _                                                                                                           |

| 37             | SO                         | OUT             | SPI output                                                                                               | -                                 | _                                                                                                           |

| 38             | NDIAG                      | OUT             | Diagnosis output                                                                                         | _                                 | _                                                                                                           |

| 39             | AMPW_O                     | OUT             | Current sense amplifier output for W phase                                                               | _                                 | -                                                                                                           |

| 40             | AMPW N                     | IN              | Current sense amplifier negative input for W phase                                                       | _                                 | _                                                                                                           |

| 41             | AMPW_P                     | IN              | Current sense amplifier positive input for W phase                                                       | _                                 | _                                                                                                           |

|                | _                          | GND             | GND 2 for analog circuits                                                                                | _                                 | _                                                                                                           |

| 42             | AGINDZ                     |                 |                                                                                                          |                                   |                                                                                                             |

| 42<br>43       | AGND2<br>AMPV O            | OUT             | Current sense amplifier output for V phase                                                               | —                                 | —                                                                                                           |

| 43             | AMPV_O                     | OUT             |                                                                                                          |                                   |                                                                                                             |

| 43<br>44       | AMPV_O<br>AMPV_N           | OUT<br>IN       | Current sense amplifier negative input for V phase                                                       |                                   |                                                                                                             |

| 43<br>44<br>45 | AMPV_O<br>AMPV_N<br>AMPV_P | OUT<br>IN<br>IN | Current sense amplifier negative input for V phase<br>Current sense amplifier positive input for V phase | -                                 |                                                                                                             |

| 43<br>44       | AMPV_O<br>AMPV_N           | OUT<br>IN       | Current sense amplifier negative input for V phase                                                       | -                                 |                                                                                                             |

#### • Internal signals

|                 |                                                            | St              | State            |  |  |  |

|-----------------|------------------------------------------------------------|-----------------|------------------|--|--|--|

| Internal Signal | Description                                                | Н               | L                |  |  |  |

| (abst_pass)     | ABIST normal signal                                        | ABIST normal    | ABIST abnormal   |  |  |  |

| (abst_end)      | ABIST end signal                                           | ABIST completed | ABIST incomplete |  |  |  |

| (gate_en_u)     | Pre-driver output enabling signal for U Phase              | Enable          | Disable          |  |  |  |

| (gate_en_v)     | Pre-driver output enabling signal for V Phase              | Enable          | Disable          |  |  |  |

| (gate_en_w)     | Pre-driver output enabling signal for W Phase              | Enable          | Disable          |  |  |  |

| (gate_en_r)     | Pre-driver output enabling signal for safety relay         | Enable          | Disable          |  |  |  |

| (gate_off_u)    | Pre-driver off signal other than ALARM factor for U Phase. | -               | _                |  |  |  |

| (gate_off_v)    | Pre-driver off signal other than ALARM factor for V Phase. | -               | _                |  |  |  |

| (gate_off_w)    | Pre-driver off signal other than ALARM factor for W Phase. | _               | _                |  |  |  |

| (gate_off_r)    | Relay off signal other than ALARM factor.                  | _               | _                |  |  |  |

| (cp_en)         | Charge pump enable signal                                  | Enable          | Disable          |  |  |  |

| (cp_off)        | Charge pump off signal                                     |                 | _                |  |  |  |

| (vbl)           | VB under voltage detection signal                          | Detection       | Release          |  |  |  |

| (vcphh)         | VCPH overvoltage detection signal                          | Detection       | Release          |  |  |  |

| (vcl1)          | VCC undervoltage detection signal 1                        | Detection       | Release          |  |  |  |

| (vcl2)          | VCC undervoltage detection signal 2                        | Detection       | Release          |  |  |  |

| (por_x)         | Internal reset signal                                      | Reset release   | Reset            |  |  |  |

| (vccopl)        | VCC_OP undervoltage detection signal                       | Detection       | Release          |  |  |  |

| (vccoph)        | VCC_OP overvoltage detection signal                        | Detection       | Release          |  |  |  |

| (vch)           | VCC overvoltage detection signal                           | Detection       | Release          |  |  |  |

| (tsddet)        | Thermal shutdown detection signal                          | Detection       | Release          |  |  |  |

| (clk4m_if)      | 4MHz clock (oscillation for IF)                            | -               | _                |  |  |  |

| (clk4m_sm)      | 4MHz clock (oscillation for SM)                            | -               | -                |  |  |  |

| (vdsuho)        | External MOSFET Vds detection signal for U phase low side  | Detection       | Release          |  |  |  |

| (vdsvho)        | External MOSFET Vds detection signal for V phase low side  | Detection       | Release          |  |  |  |

| (vdswho)        | External MOSFET Vds detection signal for W phase low side  | Detection       | Release          |  |  |  |

| (vdsulo)        | External MOSFET Vds detection signal for U phase high side | Detection       | Release          |  |  |  |

| (vdsvlo)        | External MOSFET Vds detection signal for V phase high side | Detection       | Release          |  |  |  |

| (vdswlo)        | External MOSFET Vds detection signal for W phase high side | Detection       | Release          |  |  |  |

#### Power/ground terminals

| Symbol | Pin Name    | Description                                      |

|--------|-------------|--------------------------------------------------|

| Vb     | VB          | Battery power supply input                       |

| Vcc    | VCC         | 5V/3.3V supply input                             |

| Vccop  | VCC_OP      | 5V/3.3V supply input for current sense amplifier |

| Vcph   | VCPH        | Charge pump voltage (high side)                  |

| AGND   | AGND1,AGND2 | GND for analog circuits                          |

| PGND   | PGND        | Power GND                                        |

## 7. FUNCTIONS AND FEATURES

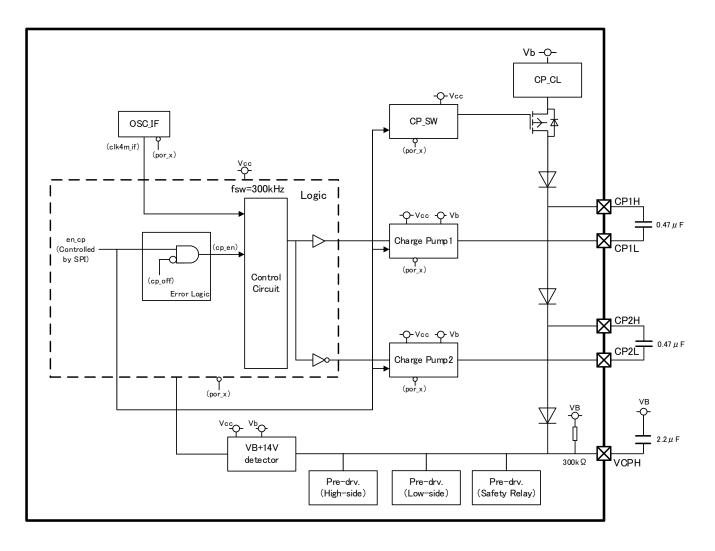

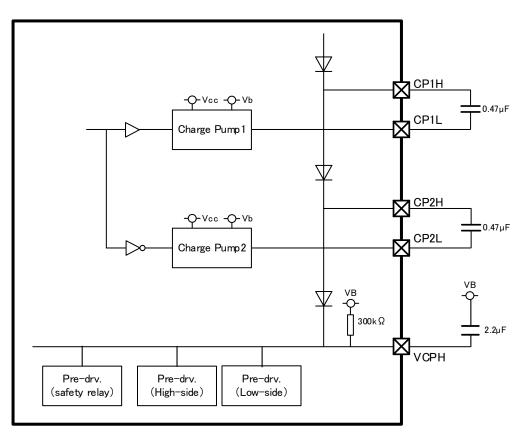

## 7.1. Charge pump circuit

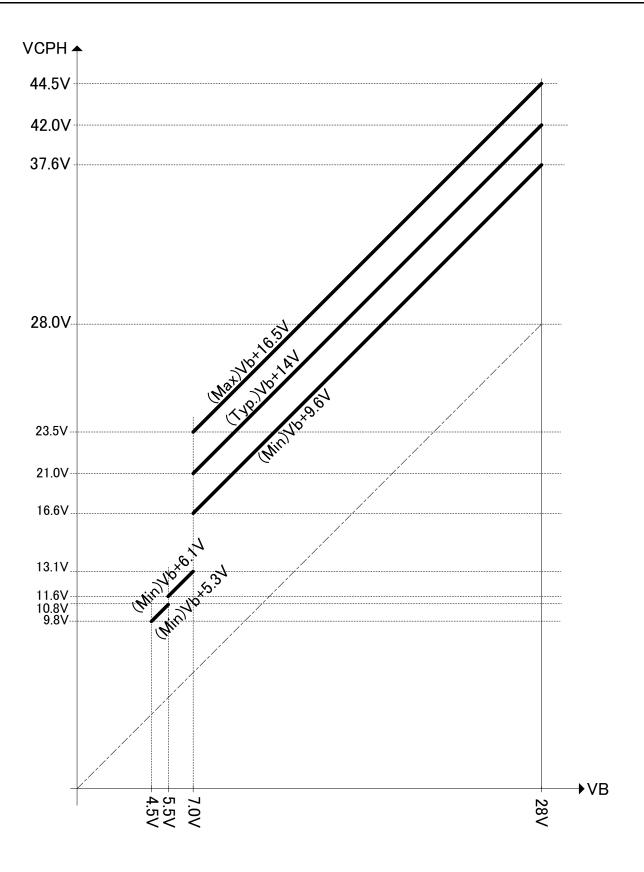

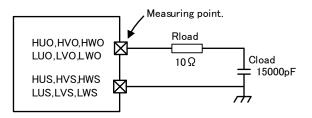

If Vcph for the pre-driver charge pump that drives the external MOSFET reaches Vb + 14 V (Typ.), the charge pump will be shut down by the internal circuit controller.

The switching circuit (CP\_SW) on the Vb side of the charge pump can switch the transistor off and shut off the supply from Vb to Vcph. When CP\_SW switches the transistor off, the charge pump stops and the VCPH terminal output voltage becomes Vb. CP\_SW also switches the transistor off when the VCC voltage falls below the VCC undervoltage detection threshold. It is also possible to make CP\_SW switch the transistor off via the SPI. Meanwhile, the CP\_CL current limiter circuit monitors current on the VB to VCPH supply line to prevent excess current.

Fig. 7.1-a Block diagram for charge pump circuit

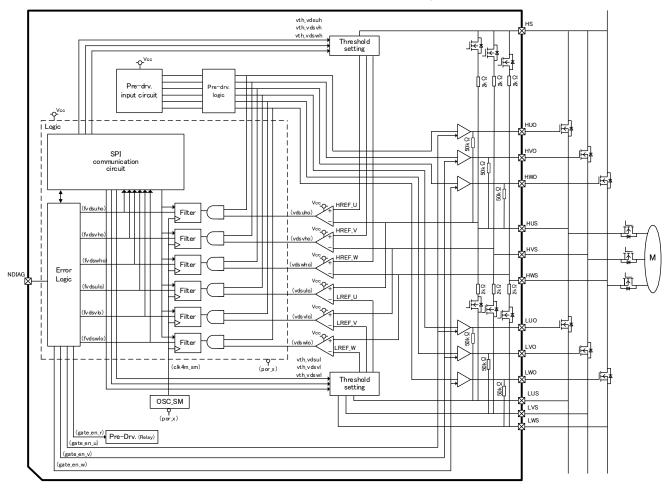

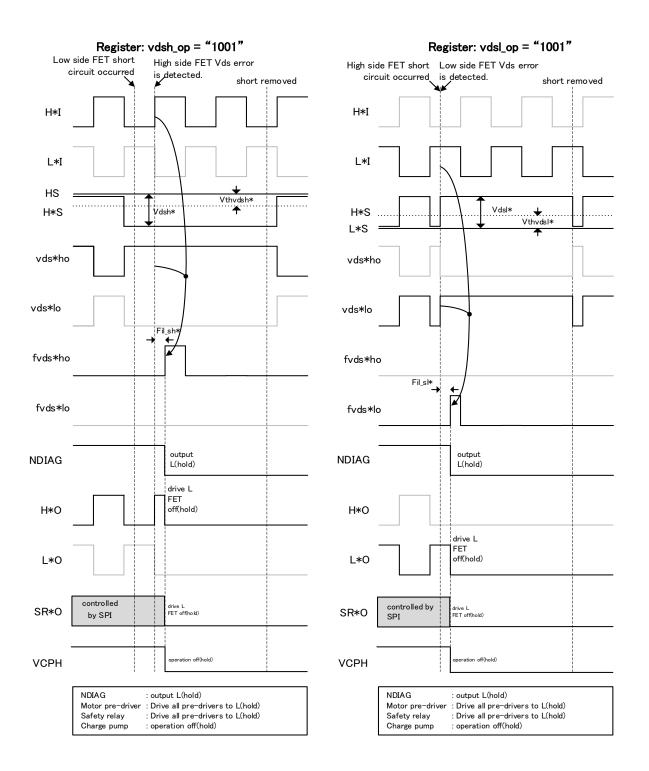

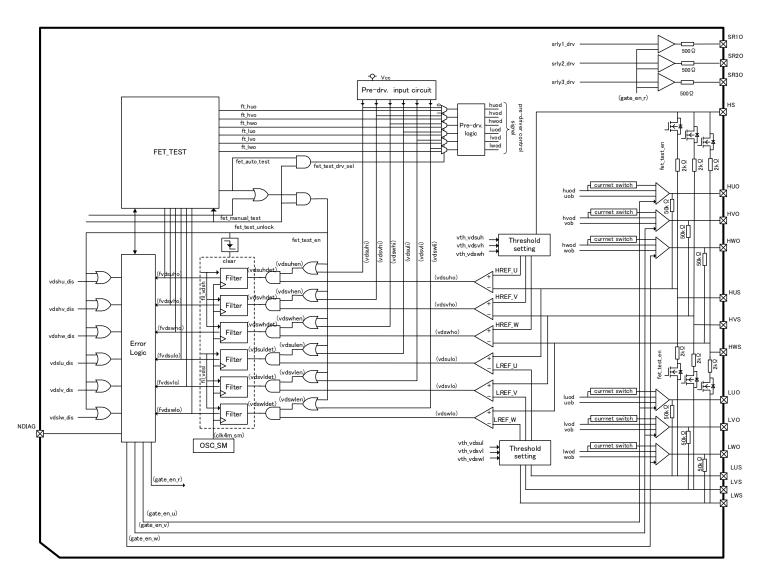

## 7.2. Pre-driver circuit

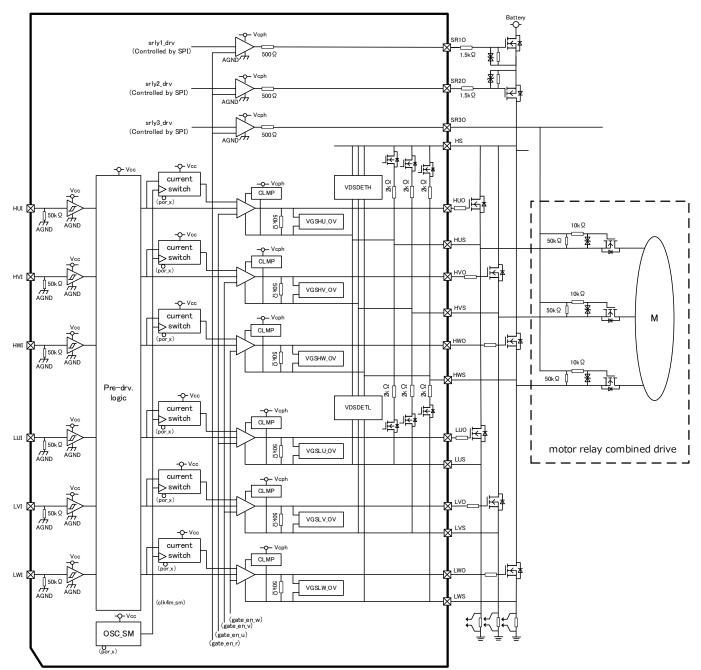

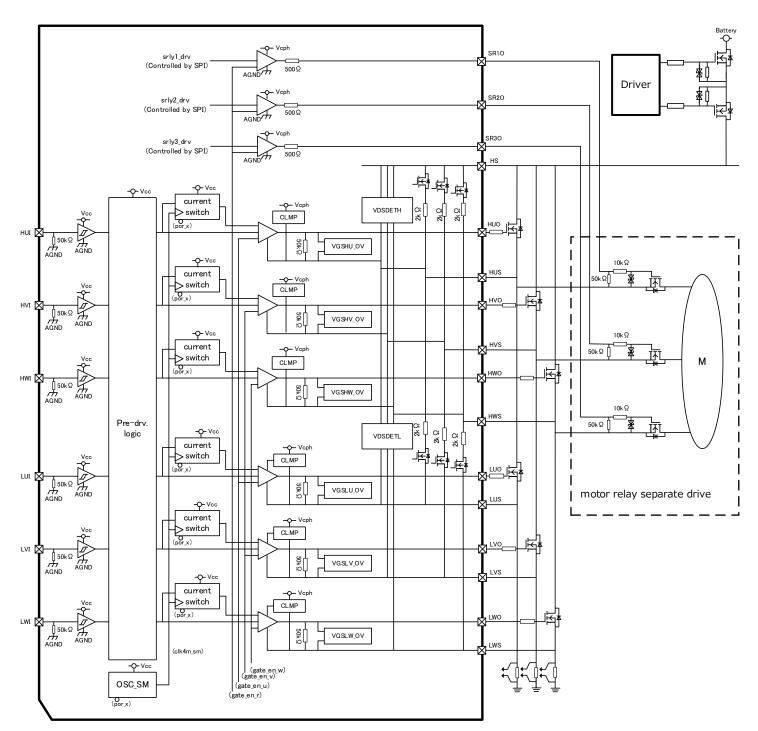

The pre-driver circuit consists of pre-drivers for high side, low side and power/motor safety relay drives.

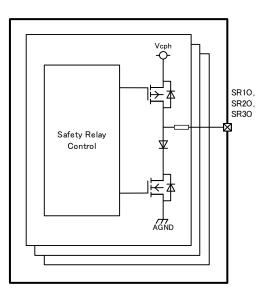

High side and low side pre-drivers have separate input and output terminals and are controlled by signal at the input terminals. The safety relay pre-driver is controlled by the <u>CP\_RLY\_CTRL</u> register. It has a built-in 500 Ω resistor and backflow prevention diode for reverse connection (see Figure 7.2-c). When a pull-down resistor is connected to the motor relay, there may be a voltage differential with the gate voltage. There is no restriction on external series resistance if safety relay outputs SR10, SR20 and/or SR30 are incorporated into the power supply relay.

A resistor for maintaining the HUS, HVS and HWS terminals at the median voltage is used only when performing an initial diagnosis as described in Section 7.8.

Fig. 7.2-a Block diagram for pre-driver circuit (motor relay combined drive)

Fig. 7.2-b Block diagram for pre-driver circuit (motor relay separate drive)

#### Safety relay (power/motor relay) driver

The safety relay driver controls the power or motor relay. The safety relay pre-driver circuit is controlled via the <u>CP\_RLY\_CTRL</u> register. It has a built-in 500  $\Omega$  resistor and backflow prevention diode for reverse connection (see Figure 7.2-c).

Table 7.2-a shows the truth table. Refer to Section 7.6 for details of internal signals (gate\_en\_r) listed in the truth table.

| • Pow | Power/motor relay driver 1 (SR10) |                       |        |        |  |  |  |  |  |  |  |

|-------|-----------------------------------|-----------------------|--------|--------|--|--|--|--|--|--|--|

|       | Internal Signal                   | Input (SPI)           | Output |        |  |  |  |  |  |  |  |

|       | (gate_en_r)                       | Register<br>srly1_drv | SR10   | Remark |  |  |  |  |  |  |  |

|       | "L"                               | *                     | "L"    | —      |  |  |  |  |  |  |  |

|       | "H"                               | "0"                   | "L"    | _      |  |  |  |  |  |  |  |

|       | П                                 | "1"                   | "H"    | _      |  |  |  |  |  |  |  |

#### Table 7.2-a I/O truth table for safety relay driver

•Power/motor relay driver 2 (SR2O)

|                 | /                     |        |        |

|-----------------|-----------------------|--------|--------|

| Internal Signal | Input (SPI)           | Output |        |

| (gate_en_r)     | Register<br>srly2_drv | SR2O   | Remark |

| "L"             | *                     | "L"    | -      |

| "H"             | "0"                   | "L"    | —      |

| п               | "1"                   | "H"    | _      |

#### •Power/motor relay driver 3 (SR3O)

| Internal Signal | Input (SPI)           | Output |        |  |  |

|-----------------|-----------------------|--------|--------|--|--|

| (gate_en_r)     | Register<br>srly3_drv | SR3O   | Remark |  |  |

| "L"             | *                     | "L"    | -      |  |  |

| "H"             | "0"                   | "L"    | _      |  |  |

|                 | "1"                   | "H"    | —      |  |  |

\*:Don't care

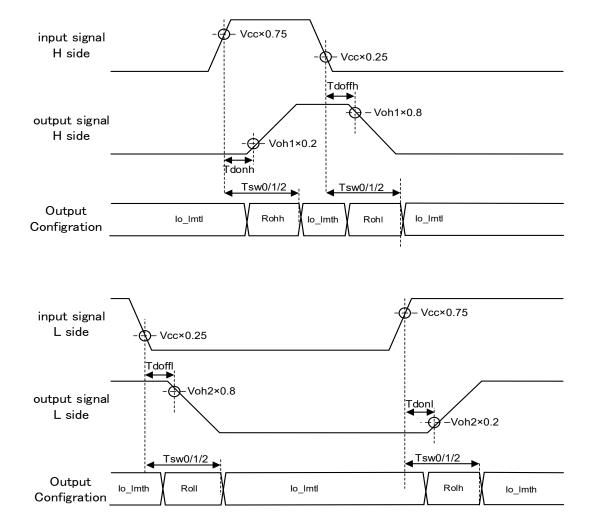

#### High side and low side drivers

The high side driver drives the MOSFET on the high side, while the low side driver drives the MOSFET on the low side. The high and low side drives both have three built-in channels. Input signal (HUI/HVI/HWI, LUI/LVI/LWI) is converted to output signal (HUO/HVO/HWO, LUO/LVO/LWO) by the control block.

#### Current limiter

Depending on the t\_ilim setting in the T\_ILIM register, the high-side and / or low-side driver can limit the current(lo\_Imth/ lo\_Imtl) after a certain period from the on / off drive transition point. A register value of t\_ilim="11" denotes no current limiting (the preset constant current); t\_ilim = "00" to "10" applies current limiting for the specified period.

#### Inhibited input

Table 7.2-b shows the truth table, using U phase as an example. The action for HUI=LUI="H" when the pre-driver is enabled (gate\_en\_u="H") can be selected via the <u>PL\_CTRL</u> register. Input prohibit mode is engaged when the plu\_dis bit is "L," and the output is HUO=LUO="L." At this time, pl\_op can be used to specify whether the status register is set to "H." When pl\_op is "H," err\_pl\_u is set to "H." When pl\_op is "L," err\_pl\_u is not set to "H." The DIAG terminal follows the status register. When plu\_dis is "H," the prohibited input detector itself is disabled and HUO=LUO="H" output is possible. Refer to Section 7.6 for details of internal signals listed in the truth table (gate\_en\_u, gate\_en\_v, gate\_en\_w).

#### Table 7.2-b I/O truth table (high side and low side drivers)

•MOSFET driver 1 (U phase)

| Internal Signal |     | out     | Regis   | ter   | Out | put | status   | Remark                                |     |  |  |       |

|-----------------|-----|---------|---------|-------|-----|-----|----------|---------------------------------------|-----|--|--|-------|

| (gate_en_u)     | HUI | LUI     | plu_dis | pl_op | HUO | LUO | err_pl_u | Remark                                |     |  |  |       |

|                 | "L" | *       | *       | *     |     |     | —        | -                                     |     |  |  |       |

| "L"             | *   | "L"     | *       | *     |     |     |          | _                                     |     |  |  |       |

|                 |     |         | "L"     | "L"   | "L" | "L" | _        | Inhibit input mode without status     |     |  |  |       |

|                 | "H" | "H"     | "H"     | "H"   | "H" | "H" | "H"      | "L"                                   | "H" |  |  | "set" |

|                 |     |         | "H"     | *     |     |     | _        | Inhibit input mode disabled (U phase) |     |  |  |       |

|                 | "L" | "L"     | *       | *     | "L" | "L" | -        | -                                     |     |  |  |       |

|                 | "L" | "H"     | *       | *     | "L" | "H" | 1        | _                                     |     |  |  |       |

| "Н"             | "H" | "L"     | *       | *     | "H" | "L" | -        | _                                     |     |  |  |       |

|                 |     |         | "L"     | "L"   | "L" | "L" | -        | Inhibit input mode without status     |     |  |  |       |

|                 | "H" | "H" "H" | "L"     | "H"   | "L" | "L" | "set"    | Inhibit input mode with status        |     |  |  |       |

|                 |     |         | "H"     | *     | "H" | "H" | _        | Inhibit input mode disabled (U phase) |     |  |  |       |

#### •MOSFET driver 2 (V phase)

| Internal Signal | Inp | out | Regis   | ster  | Out     | put | status   | Remark                                |  |  |

|-----------------|-----|-----|---------|-------|---------|-----|----------|---------------------------------------|--|--|

| (gate_en_v)     | HVI | LVI | plv_dis | pl_op | HVO     | LVO | err_pl_v | I CEITAIN                             |  |  |

|                 | "L" | *   | *       | *     |         |     | —        | —                                     |  |  |

| "L"             | *   | "L" | *       | *     |         |     | _        | -                                     |  |  |

|                 |     |     | "L"     | "L"   | "L" "L" | "L" | _        | Inhibit input mode without status     |  |  |

|                 | "H" | "H" | "L"     | "H"   |         |     | "set"    | Inhibit input mode with status        |  |  |

|                 |     |     | "H"     | *     |         |     | _        | Inhibit input mode disabled (V phase) |  |  |

|                 | "L" | "L" | *       | *     | "L"     | "L" |          | -                                     |  |  |

|                 | "L" | "H" | *       | *     | "L"     | "H" | -        | -                                     |  |  |

| "H"             | "H" | "L" | *       | *     | "H"     | "L" |          | -                                     |  |  |

|                 |     |     | "L"     | "L"   | "L"     | "L" |          | Inhibit input mode without status     |  |  |

|                 | "H" | "H" | "L"     | "H"   | "L"     | "L" | "set"    | Inhibit input mode with status        |  |  |

|                 |     |     | "H"     | *     | "H"     | "H" | _        | Inhibit input mode disabled (V phase) |  |  |

#### •MOSFET driver 3 (W phase)

| Internal Signal | Inp | out | Regis   | ster  | Out | put | status   | Remark                                |  |  |

|-----------------|-----|-----|---------|-------|-----|-----|----------|---------------------------------------|--|--|

| (gate_en_w)     | HWI | LWI | plw_dis | pl_op | HWO | LWO | err_pl_w |                                       |  |  |

|                 | "L" | *   | *       | *     |     |     | —        | -                                     |  |  |

|                 | *   | "L" | *       | *     |     | "L" | _        | _                                     |  |  |

| "L"             |     |     | "L"     | "L"   | "L" |     | _        | Inhibit input mode without status     |  |  |

|                 | "H" | "H" | "L"     | "H"   |     |     | "set"    | Inhibit input mode with status        |  |  |

|                 |     |     | "H"     | *     |     |     | _        | Inhibit input mode disabled (W phase) |  |  |

|                 | "L" | "L" | *       | *     | "L" | "L" |          | _                                     |  |  |

|                 | "L" | "H" | *       | *     | "L" | "H" |          | _                                     |  |  |

| "H"             | "H" | "L" | *       | *     | "H" | "L" | _        | _                                     |  |  |

| 11              |     |     | "L"     | "L"   | "L" | "L" | -        | Inhibit input mode without status     |  |  |

|                 | "H" | "H" | "L"     | "H"   | "L" | "L" | "set"    | Inhibit input mode with status        |  |  |

|                 |     |     | "H"     | *     | "H" | "H" | _        | Inhibit input mode disabled (W phase) |  |  |

#### \*:Don't care

Note: DIAG terminals are linked to status. Use the err\_pl\_\*\_cl bit to clear the status.

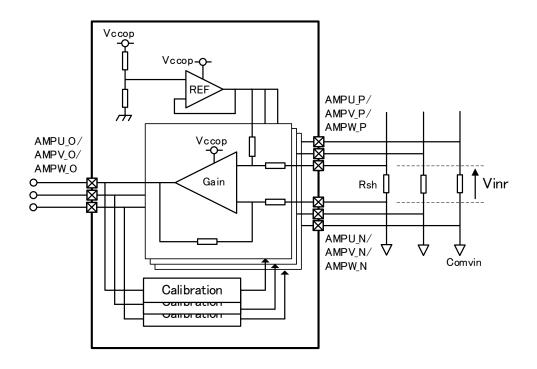

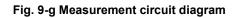

## 7.3. Current detector circuit

### 7.3.1. Circuit structure

The current detector circuit has three motor current detector amps and a reference voltage generator amp (see Figures 7.3a and 7.3-b). The motor current detector amps can amplify the difference voltage attributable to current in the shunt resistor connected to the motor drive. The reference voltage generator amp serves as a reference voltage generator buffer amp. The external composition of the current detector can be single or triple shunt.

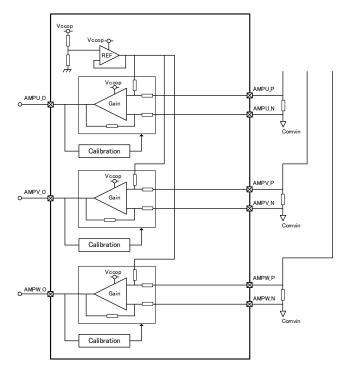

Fig. 7.3-a Block diagram for motor current detector circuit (triple shunt)

Fig. 7.3-b Block diagram for motor current detector circuit (single shunt)

#### 7.3.2. Offset calibration

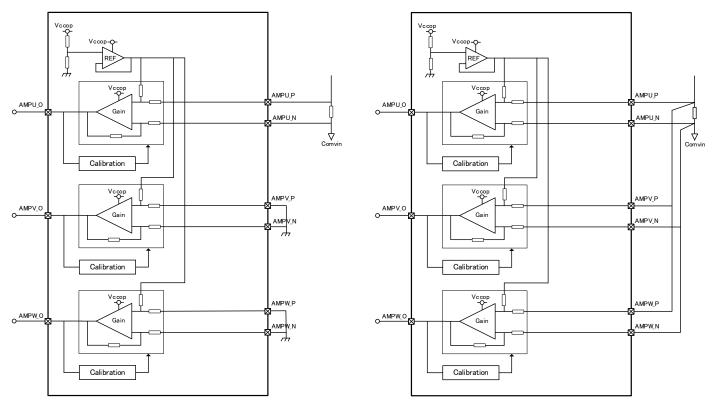

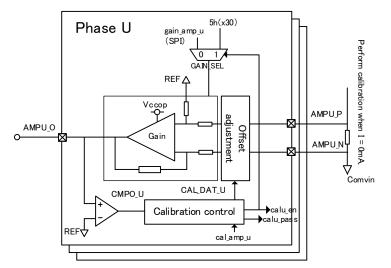

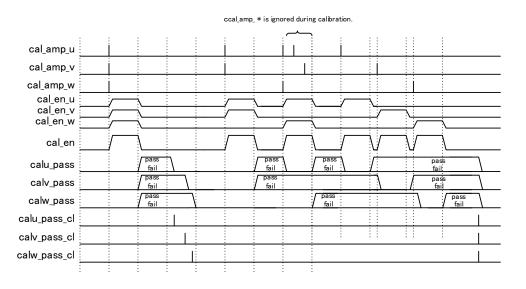

A cal\_amp\_\* (where \* denotes u, v or w) value of "1" in the <u>AMP\_CTRL</u> register is used to perform offset calibration of the current detection amp. To ensure accurate calibration, the input difference voltage must be 0 V (equivalent potential). Figure 7.3-c shows the block diagram. Cal\_amp\_\* initiates the offset calibration procedure and updates the <u>AMP\_STAT</u> register cal en to "H." For the duration of the procedure, GAIN SEL is fixed at 5 h (equivalent to 30 x). The offset calibration value is

Fig. 7.3-c Block diagram for offset calibration

determined by varying CAL\_DAT\_\* and monitoring amp output against REF. When calibration is complete, cal\_en changes to "L" and the calibration result is evaluated and then forwarded to cal\*\_pass. If cal\*\_pass is "H" the calibration result is retained as the adjustment value; if cal\*\_pass is "L" the result is discarded and the default (reset) value is restored.

Where multiple bits have been set simultaneously in cal\_amp\_\* in the <u>AMP\_CTRL</u> register, offset calibrations are performed simultaneously for the corresponding phases. When cal\_en in the <u>AMP\_STAT</u> register changes to "L" and calibration is

### Fig. 7.3-d Offset calibration

complete, cal\*\_pass is registered. The status can be cleared at any time by writing "1" to the cal\*\_pass\_cl bit in the <u>AMP\_STAT\_CLR</u> register. Note that cal\*\_pass automatically updates to "L" when calibration for the corresponding phase begins. During calibration, cal\_en is "H" and cal\_amp\_\* settings will be ignored.

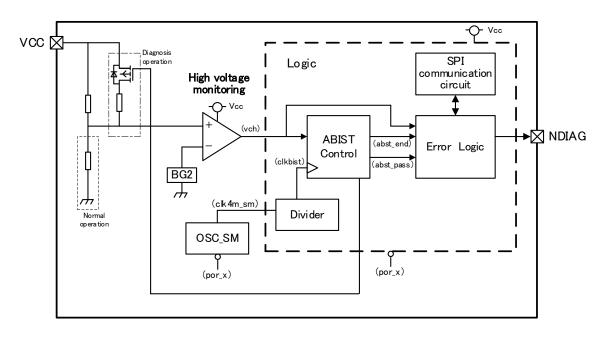

## 7.4. Oscillator circuits

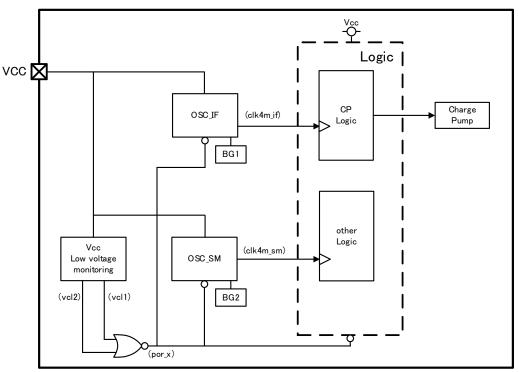

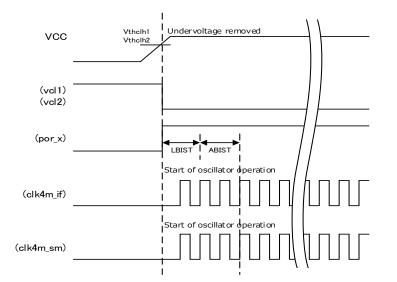

The TB9083FTG has two internal oscillator circuits: OSC\_IF is used by the charge pump, and OSC\_SM is used by the system clock, monitoring and SPI communication. Both oscillators have built-in CR and oscillate at 4 MHz (typ.). The oscillator circuits start up when the internal signal por\_x is cancelled. The reference voltage source used for the two oscillators are independent of each other(BG1,BG2).

Fig. 7.4-a Oscillator block diagram

Fig. 7.4-b Oscillator circuit timing chart

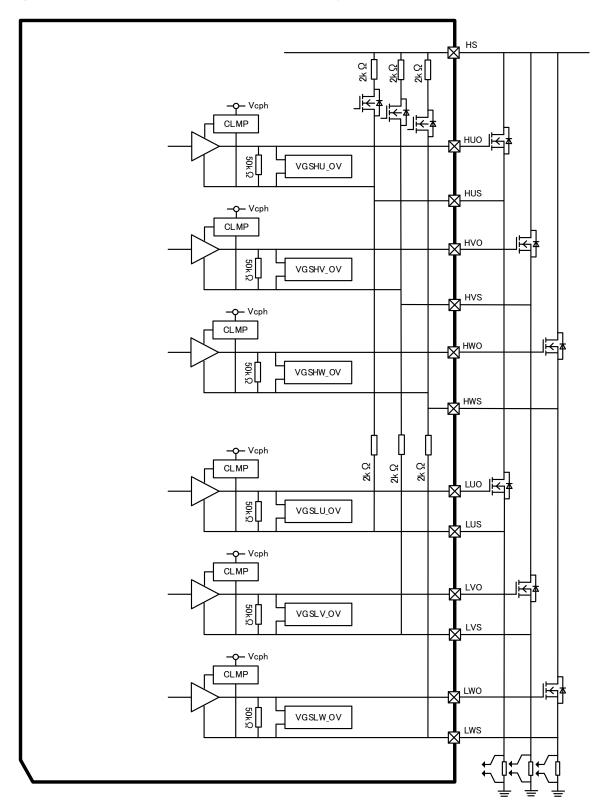

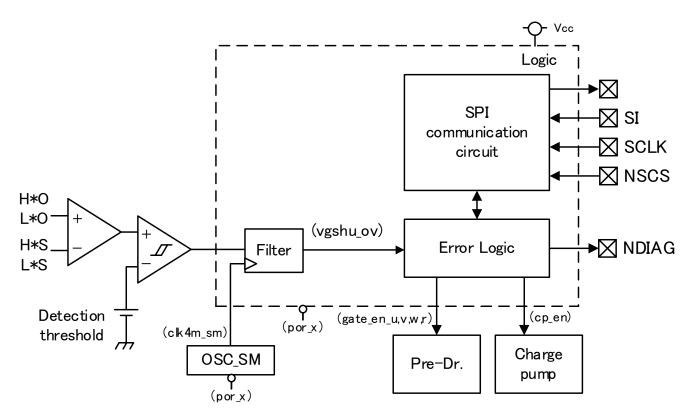

## 7.5. Error detection circuits

The TB9083FTG has error detection circuits for undervoltage (VB, VCC, VCC\_OP), overvoltage (VCPH, VCC, VCC\_OP, external MOSFET VGS), overtemperature, external MOSFET VDS and abnormal frequency. For operational descriptions refer to Section 7.5.1 onwards. When an error is detected and the pre-driver circuit has been switched off, external MOSFET VDS detection is disabled. Once the error has been rectified and the pre-driver circuit is operational, the external MOSFET VDS detection is re-enabled.

| Monitoring<br>features                        | Reg.<br>setting | Bit<br>setting | Operation in detection<br>(Note4,5,6,7)                            | Initi<br>al<br>stat<br>e | BI<br>S<br>T<br>(N<br>ot<br>e8<br>) | Status<br>Reg.<br>(Note2) | Status<br>Clear<br>(Note1) | NDI<br>AG<br>(Not<br>e3) |

|-----------------------------------------------|-----------------|----------------|--------------------------------------------------------------------|--------------------------|-------------------------------------|---------------------------|----------------------------|--------------------------|

| VCC<br>undervoltage1<br>VCC<br>undervoltage 2 | _               | _              | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF,<br>Oscillator: OFF | _                        |                                     | _                         | _                          | "L"                      |

|                                               |                 | "000"          | All(9ch) pre-drivers: OFF                                          | -                        |                                     |                           | uvb_cl                     | "L"                      |

|                                               |                 | "001"          | All(9ch) pre-drivers: OFF                                          | Х                        |                                     |                           | —                          | "L"                      |

| )/D under (elterre                            | uuda ana        | "010"          | All(9ch) pre-drivers: OFF                                          | -                        | ^                                   | unde                      | —                          | "H"                      |

| VB undervoltage                               | uvb_op          | "011"          | Motor (6ch) pre-driver: OFF                                        | -                        | A                                   | uvb                       | uvb_cl                     | "L"                      |

|                                               |                 | "100"          | Motor (6ch) pre-driver: OFF                                        | -                        |                                     |                           | —                          | "L"                      |

|                                               |                 | "101"          | Motor (6ch) pre-driver: OFF                                        | -                        |                                     |                           | _                          | "H"                      |

|                                               |                 | "000"          | Detection disabled                                                 | Х                        |                                     | _                         | —                          | "H"                      |

|                                               |                 | "001"          | Continued operation                                                | -                        |                                     |                           |                            |                          |

|                                               | ocph            | "010"          | All(9ch) pre-drivers: OFF                                          | _                        |                                     |                           |                            |                          |

| VCPH                                          |                 | "011"          | Motor (6ch) pre-driver: OFF                                        | _                        |                                     |                           |                            |                          |

| overvoltage                                   | _op             |                | All(9ch) pre-drivers: OFF,                                         |                          | A                                   | ocph                      | ocph_cl                    | "L"                      |

| -                                             |                 | "100"          | Charge pump: OFF                                                   | _                        |                                     | -                         |                            |                          |

|                                               |                 | "404"          | All(9ch) pre-drivers: OFF,                                         |                          |                                     |                           |                            |                          |

|                                               |                 | "101"          | Charge pump: OFF                                                   | _                        |                                     |                           |                            |                          |

|                                               |                 | "000"          | Detection disabled                                                 | —                        |                                     | _                         | —                          | "H"                      |

|                                               |                 | "001"          | Continued operation                                                | —                        |                                     | ovcc                      | ovcc_cl                    |                          |

|                                               |                 | "010"          | All(9ch) pre-drivers: OFF                                          | Х                        |                                     |                           |                            | "L"                      |

| VCC                                           | 01/0 00         | "011"          | Motor (6ch) pre-driver: OFF                                        | -                        | ^                                   |                           |                            |                          |

| overvoltage                                   | ovc_op          | "100"          | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF                     | -                        | A                                   |                           |                            |                          |

|                                               |                 | "101"          | All(9ch) pre-drivers: OFF (hold),<br>Charge pump: OFF (hold)       | _                        |                                     |                           |                            |                          |

| VCC OP                                        |                 | "000"          | Detection disabled                                                 | Х                        |                                     | _                         | _                          | "Н"                      |

| undervoltage                                  |                 | "001"          | Continued operation                                                | _                        |                                     |                           |                            |                          |

| 0                                             |                 | "010"          | All(9ch) pre-drivers: OFF                                          | _                        |                                     |                           |                            |                          |

|                                               | uvccop          | "011"          | Motor (6ch) pre-driver: OFF                                        | _                        |                                     |                           |                            |                          |

|                                               | _op             |                | All(9ch) pre-drivers: OFF,                                         |                          | A                                   | uvccop                    | uvccop_cl                  | "L"                      |

|                                               |                 | "100"          | Charge pump: OFF                                                   | _                        |                                     |                           | '-                         |                          |

|                                               |                 |                | All(9ch) pre-drivers: "L"(hold),                                   |                          | -                                   |                           |                            |                          |

|                                               |                 | "101"          | Charge pump: OFF (hold)                                            | _                        |                                     |                           |                            |                          |

| VCC_OP                                        | ovccop          | "000"          | Detection disabled                                                 | Х                        |                                     | _                         | —                          | "H"                      |

| overvoltage                                   | _op             | "001"          | Continued operation                                                | -                        |                                     |                           |                            |                          |

| -                                             |                 | "010"          | All(9ch) pre-drivers: OFF                                          | -                        |                                     |                           |                            |                          |

|                                               |                 | "011"          | Motor (6ch) pre-driver: OFF                                        | _                        | А                                   | A ovccop                  |                            |                          |

|                                               |                 | "100"          | All(9ch) pre-drivers: OFF,                                         | -                        |                                     |                           | ovvccop_cl                 | "L"                      |

|                                               |                 |                | Charge pump: OFF                                                   |                          |                                     |                           |                            |                          |

|                                               |                 | "101"          | All(9ch) pre-drivers: "L"(hold),                                   |                          |                                     |                           |                            |                          |

#### Table 7.5-a Monitoring functions

## TB9083FTG

| Monitoring<br>features    | Reg.<br>setting | Bit<br>setting                                              | Operation in detection<br>(Note4,5,6,7)                     | Initi<br>al<br>stat<br>e | BI<br>S<br>T<br>(N<br>ot<br>e8<br>) | Status<br>Reg.<br>(Note2)                                | Status<br>Clear<br>(Note1)                       | NDI<br>AG<br>(Not<br>e3) |

|---------------------------|-----------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------------|-------------------------------------|----------------------------------------------------------|--------------------------------------------------|--------------------------|

|                           |                 |                                                             | Charge pump: OFF (hold)                                     |                          |                                     |                                                          |                                                  |                          |

|                           |                 | "000"                                                       | Detection disabled                                          | _                        | Α                                   | _                                                        | _                                                | "H"                      |

|                           |                 | "001"                                                       | Continued operation                                         | -                        | -                                   |                                                          |                                                  |                          |

|                           |                 | "010"                                                       | All(9ch) pre-drivers: OFF                                   | Х                        | -                                   |                                                          |                                                  |                          |

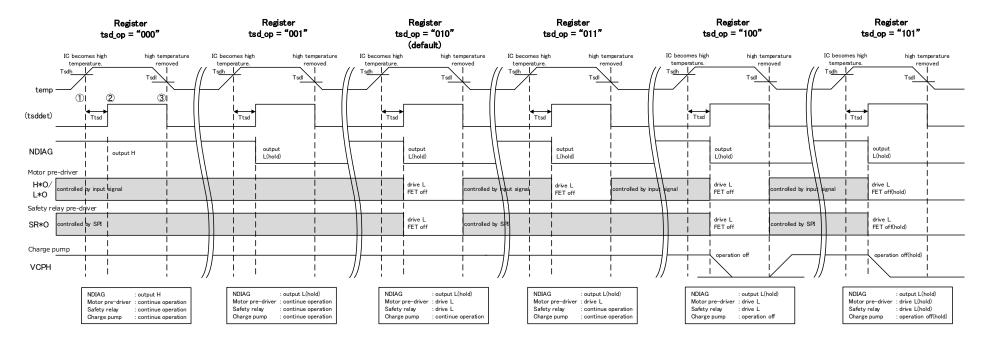

| Over                      | tsd_op          | "011"                                                       | Motor (6ch) pre-driver: OFF                                 | _                        | -                                   |                                                          |                                                  |                          |

| temperature               |                 | "100"                                                       | All(9ch) pre-drivers: OFF<br>Charge pump: OFF               | -                        |                                     | tsd                                                      | tsd_cl                                           | "L"                      |

|                           |                 | "101"                                                       | All(9ch) pre-drivers: OFF (hold)<br>Charge pump: OFF (hold) | _                        |                                     |                                                          |                                                  |                          |

|                           | alr on          | "0"                                                         | All(9ch) pre-drivers: OFF                                   | Х                        | _                                   | alm_det                                                  | —                                                | "L"                      |

|                           | all_op          | "1"                                                         | Motor (6ch) pre-driver: OFF                                 | —                        |                                     | ann_uer                                                  |                                                  |                          |

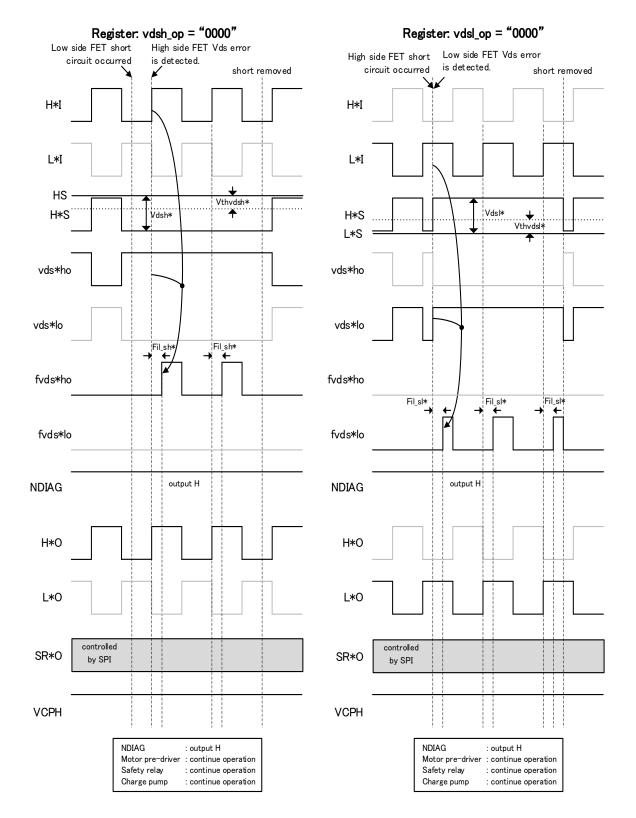

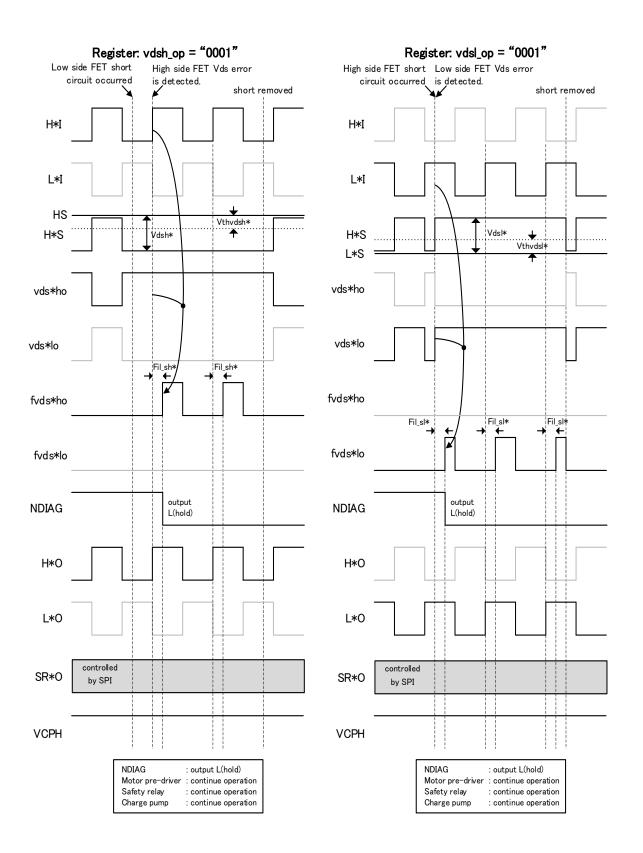

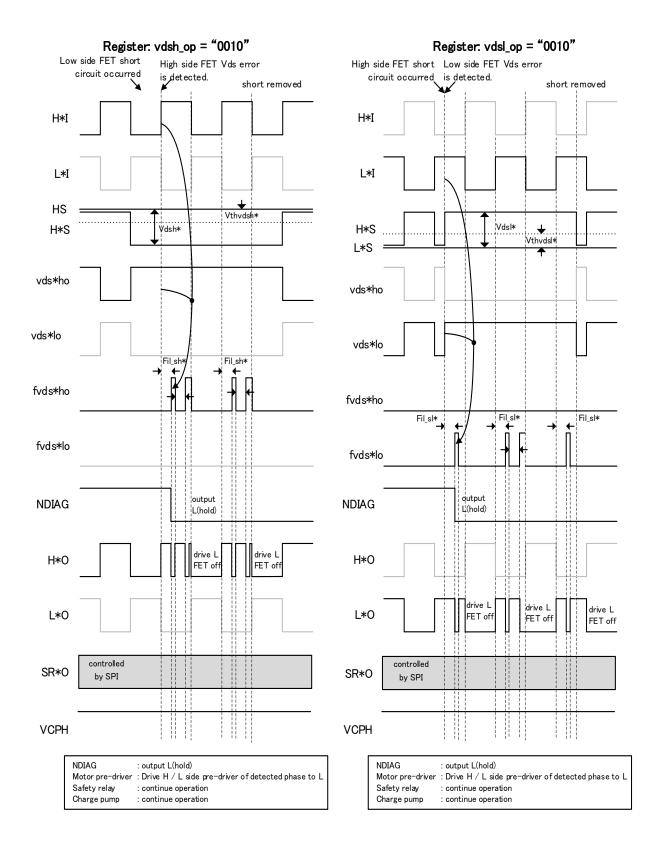

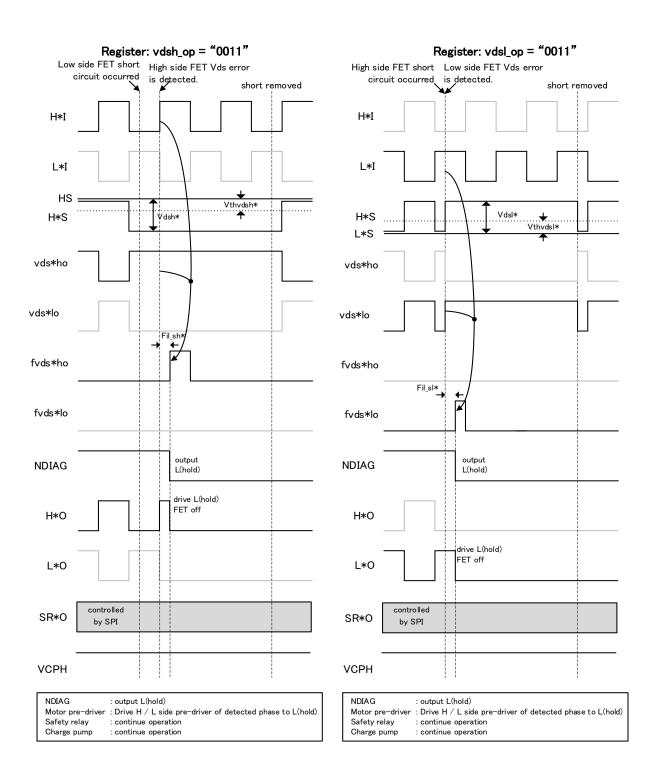

|                           |                 | "0000"                                                      | Detection disabled                                          | —                        | -                                   | _                                                        | —                                                | "H"                      |

|                           |                 | "0001"                                                      | Continued operation                                         | —                        | -                                   |                                                          |                                                  |                          |

|                           |                 | "0010"                                                      | Detected phase pre-driver: OFF                              | —                        | -                                   | vds_uh<br>vds_vh<br>vds_wh                               | vds_uh_cl                                        |                          |

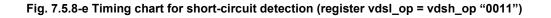

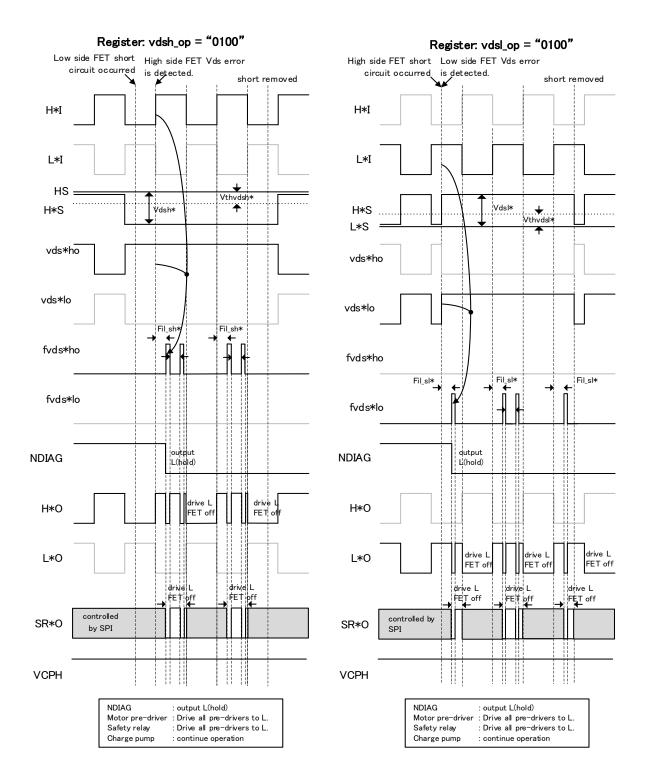

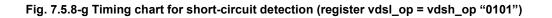

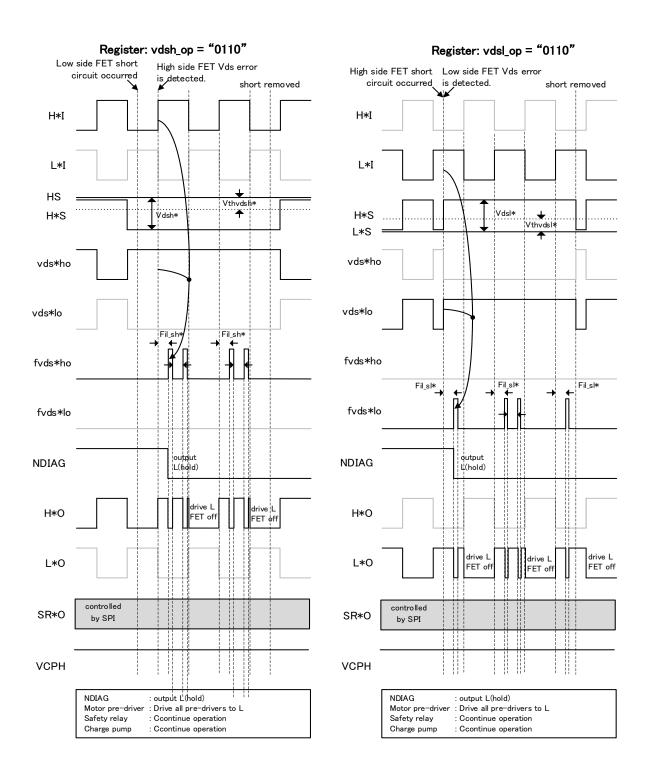

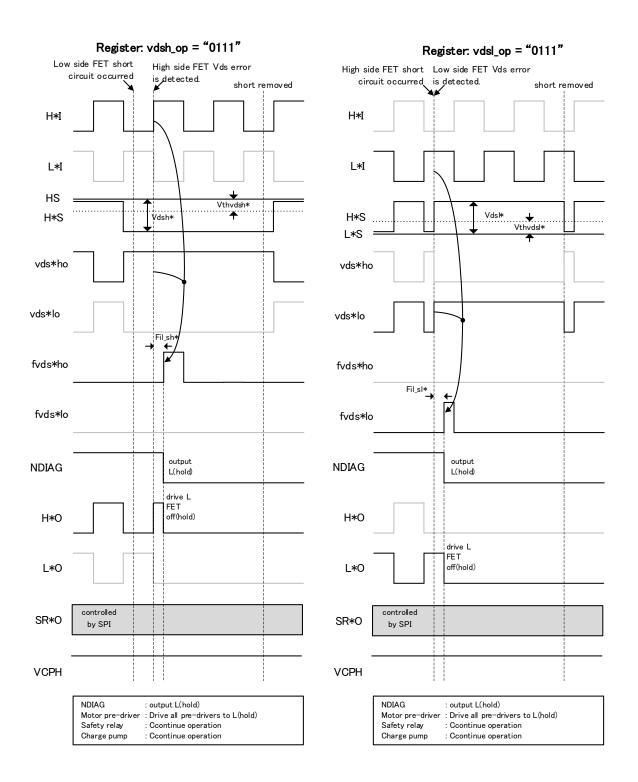

| External                  | vdsh<br>_op     | "0011"                                                      | Detected phase pre-driver:<br>OFF(hold)                     | _                        |                                     |                                                          |                                                  |                          |

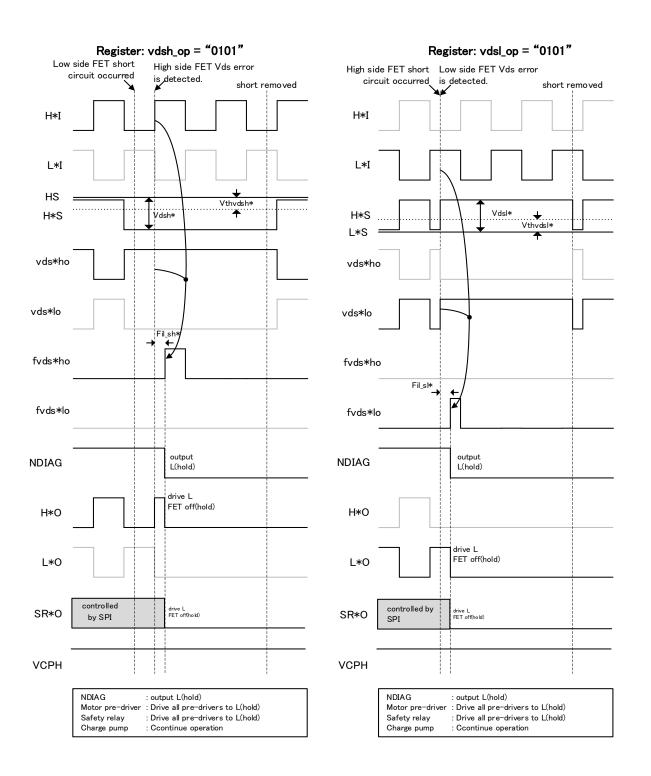

| MOSFET                    |                 | "0100"                                                      | All(9ch) pre-drivers: OFF                                   | —                        |                                     |                                                          |                                                  |                          |

| Vds                       |                 | "0101"                                                      | All(9ch) pre-drivers: OFF(hold)                             | —                        | -                                   |                                                          | vds_un_cl<br>vds_vh_cl                           | "L"                      |

| (high side)               |                 | "0110"                                                      | Motor (6ch) pre-driver: OFF                                 | —                        |                                     |                                                          | vds_wh_cl                                        | L .                      |

|                           |                 | "0111"                                                      | Motor (6ch) pre-driver: OFF(hold)                           | Х                        |                                     | vao_m                                                    | vuo_wn_or                                        |                          |

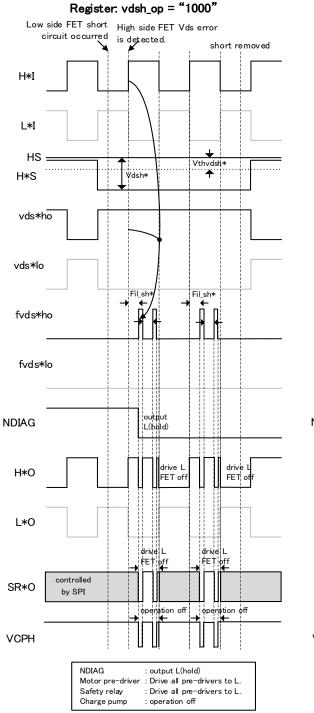

|                           |                 | "1000"                                                      | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF              | _                        |                                     |                                                          |                                                  |                          |

|                           |                 | "1001"                                                      | All(9ch) pre-drivers: OFF(hold),<br>Charge pump: OFF (hold) | _                        |                                     |                                                          |                                                  |                          |

|                           |                 | "0000"                                                      | Detection disabled                                          | _                        |                                     | _                                                        | _                                                | "H"                      |

|                           |                 | "0001"                                                      | Continued operation                                         | _                        |                                     |                                                          |                                                  |                          |

|                           |                 | "0010"                                                      | Detected phase pre-driver: OFF                              | _                        |                                     |                                                          |                                                  |                          |

| External                  |                 | "0011"                                                      | Detected phase pre-driver:<br>OFF(hold)                     | _                        |                                     |                                                          |                                                  |                          |

| MOSFET                    |                 | "0100"                                                      | All(9ch) pre-drivers: OFF                                   | —                        |                                     |                                                          |                                                  |                          |

| Vds                       |                 | "0101"                                                      | All(9ch) pre-drivers: OFF(hold)                             | —                        | -                                   | vds_ul                                                   | vds_ul_cl                                        | "L"                      |

| (low side)                | _op             | "0110"                                                      | Motor (6ch) pre-driver: OFF                                 |                          | ]                                   | vds_vl                                                   | vds_vl_cl                                        | _ "L"                    |

|                           |                 | "0111"                                                      | Motor (6ch) pre-driver:OFF(hold)                            | Х                        |                                     | vds_wl                                                   | vds_wl_cl                                        |                          |

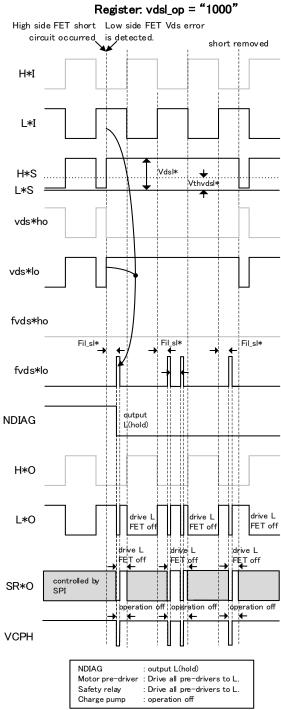

|                           |                 | "1000"                                                      | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF              | _                        |                                     |                                                          |                                                  |                          |

| ALARM alr_op              | "1001"          | All(9ch) pre-drivers: OFF(hold),<br>Charge pump: OFF (hold) | _                                                           |                          |                                     |                                                          |                                                  |                          |

|                           |                 | "000"                                                       | Detection disabled                                          | —                        |                                     | _                                                        | _                                                | "H"                      |

|                           |                 | "001"                                                       | Continued operation                                         | —                        | 1                                   |                                                          |                                                  |                          |

|                           |                 | "010"                                                       | All(9ch) pre-drivers: OFF                                   | —                        | 1                                   |                                                          |                                                  |                          |

|                           |                 | "011"                                                       | Motor (6ch) pre-driver: OFF                                 | —                        | ]                                   |                                                          |                                                  |                          |

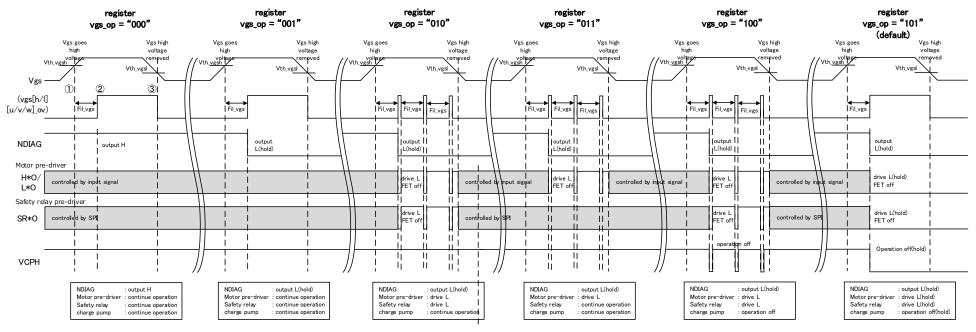

| external                  | vgs_op          | "100"                                                       | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF              | _                        |                                     | vgs_uh<br>vgs_ul<br>vgs_vh<br>vgs_vl<br>vgs_wh<br>vgs_wl | vgs_uh_cl<br>vgs_ul_cl                           |                          |

| MOSFET<br>Vgs overvoltage |                 | "101"                                                       | All(9ch) pre-drivers: OFF(hold),<br>Charge pump: OFF (hold) | x                        | A                                   |                                                          | vgs_vh_cl<br>vgs_vl_cl<br>vgs_wh_cl<br>vgs_wl_cl | "L"                      |

| Monitoring<br>features         | Reg.<br>setting | Bit<br>setting | Operation in detection<br>(Note4,5,6,7)                     | Initi<br>al<br>stat<br>e | BI<br>S<br>T<br>(N<br>ot<br>e8<br>) | Status<br>Reg.<br>(Note2)        | Status<br>Clear<br>(Note1)                | NDI<br>AG<br>(Not<br>e3) |

|--------------------------------|-----------------|----------------|-------------------------------------------------------------|--------------------------|-------------------------------------|----------------------------------|-------------------------------------------|--------------------------|

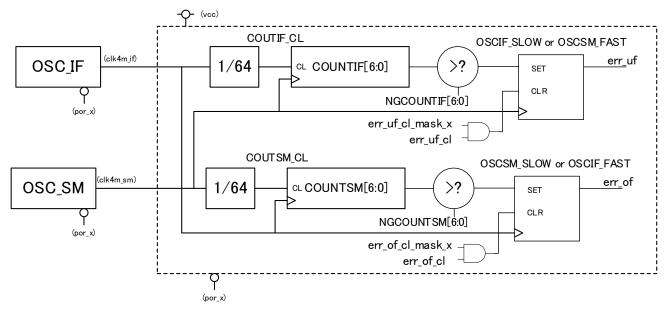

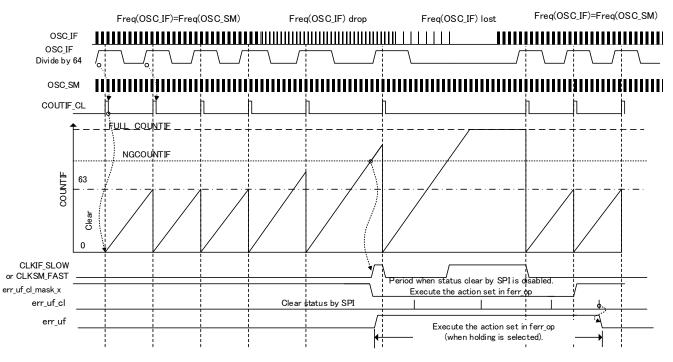

|                                |                 | "000"          | Detection disabled                                          | 0                        |                                     | -                                | _                                         | "H"                      |

|                                |                 | "001"          | Continued operation                                         | -                        |                                     | err_of<br>err_uf                 |                                           |                          |

| Abnormalities in               |                 | "010"          | All(9ch) pre-drivers: OFF                                   | —                        |                                     |                                  | err_of_cl<br>err_uf_cl                    |                          |

| frequency                      | ferr_op         | "011"          | Motor (6ch) pre-driver: OFF                                 | —                        | L                                   |                                  |                                           |                          |

| (Note 9)                       |                 | "100"          | All(9ch) pre-drivers: OFF,<br>Charge pump: OFF              | -                        |                                     |                                  |                                           | "L"                      |

|                                |                 | "101"          | All(9ch) pre-drivers: OFF(hold),<br>Charge pump: OFF (hold) | _                        |                                     |                                  |                                           |                          |

|                                |                 | "0"            | Detected phase pre-driver: OFF                              | 0                        |                                     | _                                | —                                         | "H"                      |

| Pre-driver<br>Inhibition input | pl_op           | "1"            | Detected phase pre-driver: OFF                              | _                        | _                                   | err_pl_u<br>err_pl_v<br>err_pl_w | err_pl_u_cl<br>err_pl_v_cl<br>err_pl_w_cl | "L"                      |

| SPI<br>communication<br>error  | _               | _              | Detection disabled                                          | _                        | _                                   | err_spi                          | err_spi_cl                                | "L"                      |

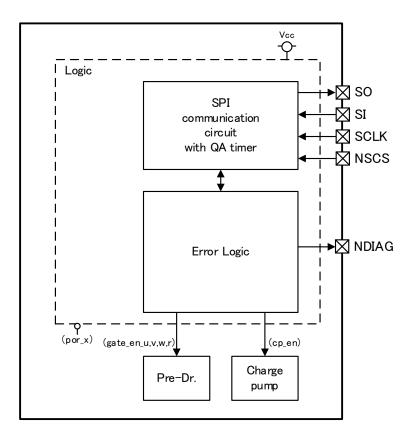

|                                |                 | "001"          | Continued operation                                         | 0                        |                                     |                                  |                                           |                          |

|                                |                 | "010"          | All(9ch) pre-drivers: OFF(hold)                             | —                        | L                                   |                                  |                                           |                          |

| QA calculation                 | qat_op          | "011"          | Motor (6ch) pre-driver: OFF                                 | -                        |                                     | err_qac                          | err_qac_cl                                | "L"                      |

|                                |                 | "100"          | All(9ch) pre-drivers: OFF(hold),<br>Charge pump: OFF (hold) | -                        |                                     |                                  |                                           |                          |

Note1 In settings modes where the status clear bit is shown in the Status Clear column, once a status bit has been set by the error detection function, it will be retained until cleared by writing "1" to the corresponding status clear bit. A retained status register cannot be cleared while the error detection circuit is still showing an error. In operation modes that do not have a status clear bit in the Status Clear column, the status bit is cleared when error detection is resolved.

Note2 A dash in the Status Reg column indicates that no value is set in the status register for that operating mode.

- Note3 "H" in the NDIAG column means that the NDIAG terminal does not change to "L" when an error is detected. "L" in the NDIAG column means that the NDIAG terminal will be the same as the status register (with the exception of VCC undervoltage detection). NDIAG output is "L" while the status register is retained, but reverts to "H" when all status registers are cleared. In operating modes where the status register is not retained, NDIAG reverts to "H" when error detection is cleared, irrespective of whether the status register has been cleared.

- Note4 "(Retained)" in the Response to Detection column means that the response is dictated by the retained status register. To revert to the standard response, the status register needs to be cleared. Where "(Retained)" does not appear, this means that the normal response will be restored once error detection is cleared, without needing to clear the status register.

Note5 The value \*\*\*\*\_op in the settings register for a monitoring function can be modified at any time; however, \*\*\*\*\_op has no effect on actual operations while the corresponding status register is indicating that an error has been detected.

Note6 "Charge pump off" means the CP\_SW is off and the CP driver stopped.

Note7 "All (9ch) pre-drivers:OFF", the pre-driver is driven to "L" so that the external FET including the safety relay is turned off. "Motor (6ch) pre-drivers:OFF" drives the pre-driver to "L" so that the external FET except the safety relay is turned off. "Detected phase pre-driver : OFF", the pre-driver is driven to "L" to turn off the high-side and low-side FET of the phase where the abnormality is detected.

Note8 A = ABIST, L = LBIST

Note9 If the OSC\_SM clock is lost, the detection response can still be executed but NDIAG will not change to "L."

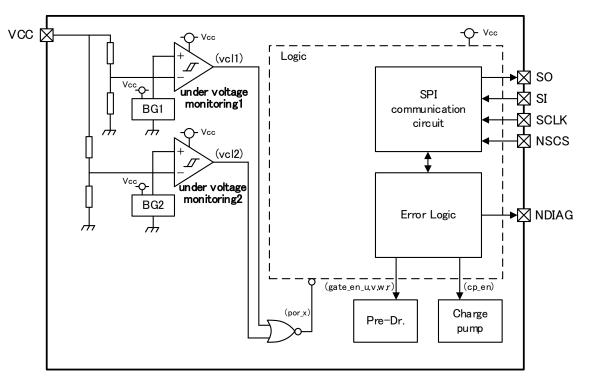

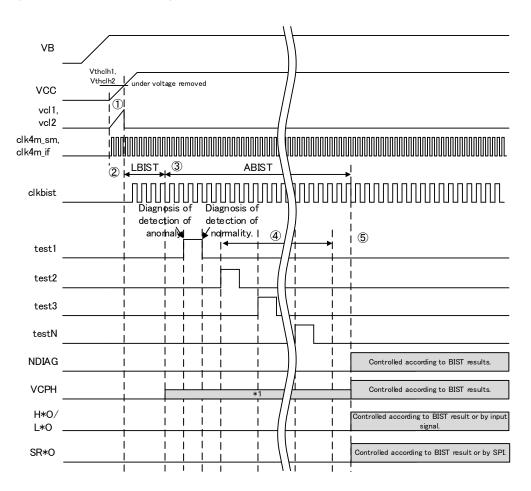

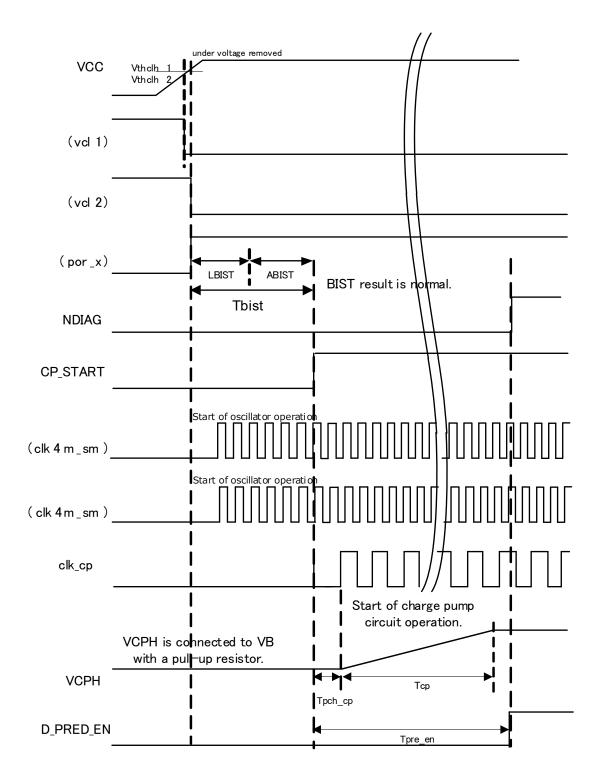

### 7.5.1. VCC undervoltage detection 1 and 2

This circuit has two built-in comparators for detecting low VCC voltage; an "H" value from either of the comparators indicates undervoltage. The band gap voltages used as the baseline reference by the comparators are generated by band gap circuits BG1 and BG2.

Fig. 7.5.1-a Block diagram for VCC undervoltage detector

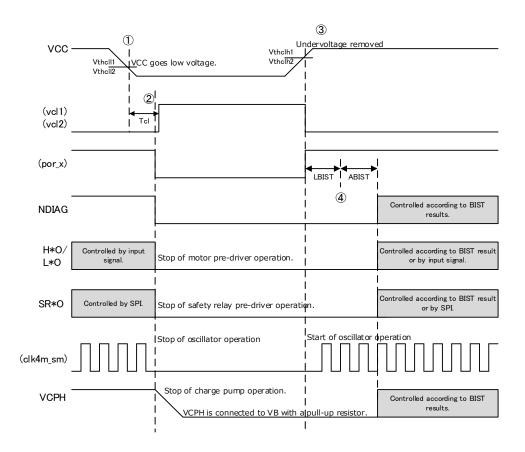

#### ➤ ① VCC voltage drops

roshiba

VCC voltage drops below the undervoltage Vthcll1/Vthcll2.

② VCC undervoltage detected

After the response time Tcl, VCC undervoltage signal (vcl1), (vcl2) "H" denotes undervoltage detection, (por\_x) changes to "L" and NDIAG output is "L." The motor drive (6 ch) pre-driver, safety relay (3 ch) pre-driver, charge pump and oscillator circuits all switch off and remain off until the undervoltage is cancelled.

> ③ VCC voltage restored (undervoltage cancelled)

When VCC voltage is greater than Vthclh1/Vthclh2, VCC undervoltage signal (vcl1), (vcl2) changes to "L" and undervoltage is cancelled.

#### ➤ ④ Normal operation resumes

If a BIST diagnosis of OK is returned after LBIST/ABIST execution, normal operation resumes. The charge pump circuit starts operating and the pre-driver circuits are re-enabled. If an NG diagnosis is returned, the charge pump and pre-driver circuits will not operate. NDIAG output is "H" for an OK diagnosis and "L" for a NG diagnosis. (See Section 7.7 for details.)

#### Fig. 7.5.1-b Timing chart for VCC undervoltage detection

Note: If the Vcc voltage falls further below the undervoltage threshold, standby mode will be engaged, whereby all functions other than Vcc undervoltage detection are switched off.

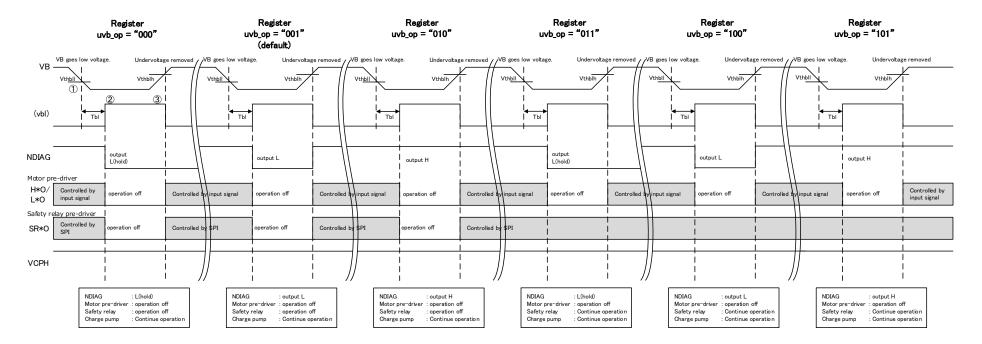

### 7.5.2. VB undervoltage detection

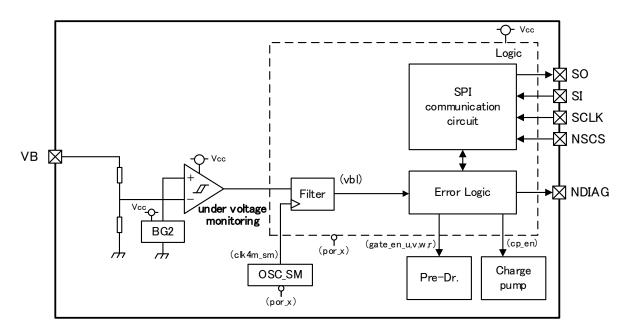

This circuit comprises a comparator and a filter for detecting VB undervoltage; filter output of "H" indicates undervoltage. The band gap voltage used as the baseline reference by the comparator is generated by the band gap circuit BG2.

Fig. 7.5.2-a Block diagram for VB undervoltage detection

#### ➤ ① VB voltage drops

VB voltage drops below the undervoltage threshold Vthbll. Vb L detection comparator outputs H.

#### > ② VB undervoltage detected

After the detection filter time Tbl has elapsed, VB undervoltage signal (vbl) "H" indicating undervoltage is generated, and all (9 ch) pre-driver circuits including safety relay switch off, as well as the motor drive (6 ch) pre-driver circuit. Note that the oscillator and charge pump circuits do not switch off. Pre-driver circuits remain off until undervoltage is cancelled.

At this point one of six operating modes can be selected via the SPI.

If the mode is changed during VB undervoltage, settings will not be enabled until the undervoltage is cancelled and the uvb register is cleared.

➤ ③ VB voltage restored (undervoltage cancelled)

Once the VB voltage exceeds Vthblh, the VB undervoltage signal (vbl) changes to "L," undervoltage is cancelled and normal operation resumes.

If NDIAG output is "L," clear the uvb register via the SPI to change it back to "H."

During an undervoltage, uvb register cannot be cleared and NDIAG output is "L."

Fig. 7.5.2-b Timing chart for VB undervoltage detection

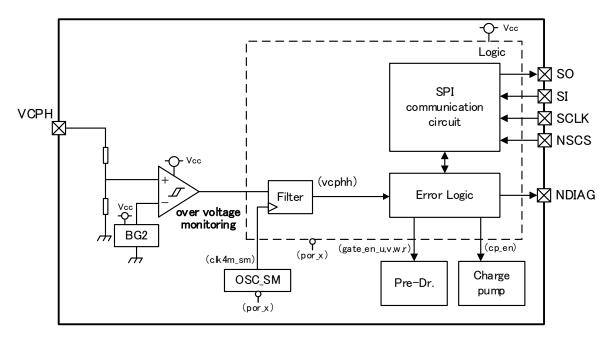

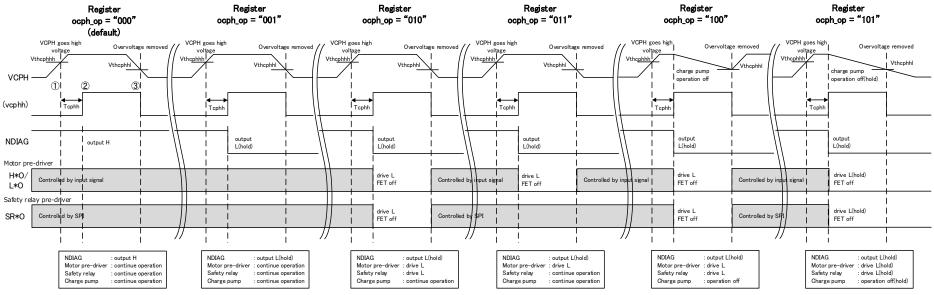

### 7.5.3. VCPH overvoltage detection

This circuit comprises a comparator and a filter; filter output of "H" indicates overvoltage. The band gap voltage used as the baseline reference by the comparator is generated by the band gap circuit BG2.

Fig. 7.5.3-a Block diagram for VCPH overvoltage

#### ➤ ① VCPH voltage rises

VCPH voltage exceeds the overvoltage threshold Vthcphh. VCPH H detection comparator outputs "H."

#### ➤ ② VCPH overvoltage detected

After the filter time Tcphh has elapsed, VCPH overvoltage signal (vcphh) "H" indicating overvoltage is generated and NDIAG output is "L," except where the register ocph\_op is "000," in which case NDIAG output remains at "H" and all circuits continue to operate as normal.

At this point one of six operating modes can be selected via the SPI.

If the mode is changed during VCPH overvoltage, settings will not be enabled until the overvoltage is cancelled and the ocph register is cleared.

#### > ③ VCPH voltage restored (overvoltage cancelled)

Once the VCPH voltage drops below Vthcphhl, the VCPH overvoltage signal (vcphh) changes to "L" and the overvoltage is cancelled.

When register ocph\_op is "101," the charge pump and pre-drivers remain off after the overvoltage is cancelled and NDIAG remains at "L."

When register ocph\_op is "001", "010", "011" or "100," the charge pump and pre-drivers operate normally but the status register is retained and NDIAG remains at "L."

When register ocph is cleared via SPI, NDIAG changes to "H."

During an overvoltage, register ocph cannot be cleared and NDIAG output is "L."

Fig. 7.5.3-b Timing chart for VCPH overvoltage

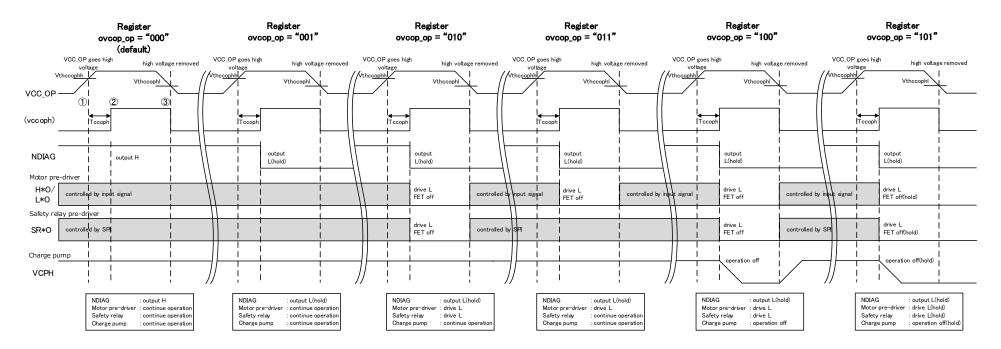

### 7.5.4. VCC overvoltage detection

This circuit comprises a comparator and a filter; filter output of "H" indicates overvoltage. The band gap voltage used as the baseline reference by the comparator is generated by the band gap circuit BG2.

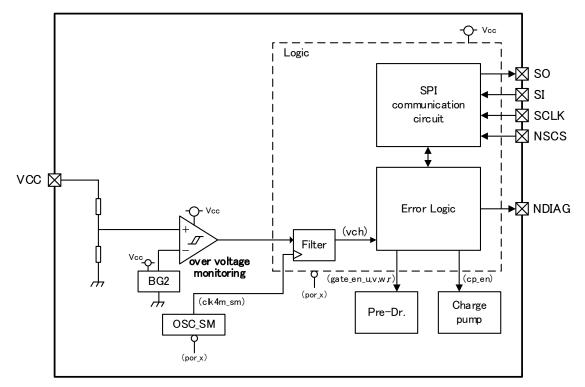

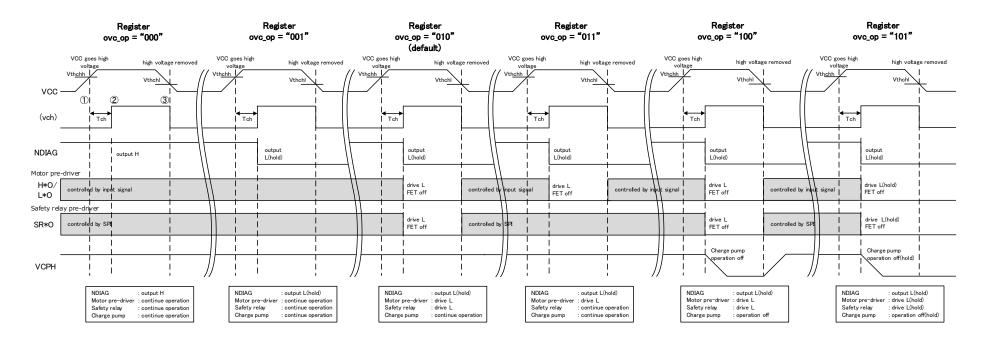

Fig. 7.5.4-a Block diagram for VCC overvoltage detection

#### ➤ ① VCC voltage rises

VCC voltage exceeds the overvoltage threshold Vthchh. VCC H detection comparator outputs "H."

#### ➤ ② VCC overvoltage detected

After the filter time Tch has elapsed, VCC overvoltage signal (vch) "H" indicating overvoltage is generated and NDIAG output is "L," except where the register ovc\_op is "000," in which case NDIAG output remains at "H" and all circuits continue to operate as normal.

At this point one of six operating modes can be selected via the SPI.

If the mode is changed during VCC overvoltage, settings will not be enabled until the overvoltage is cancelled and the ovc register is cleared.

#### > ③ VCC voltage restored (overvoltage cancelled)

Once the VCC voltage drops below Vthchl, the VCC overvoltage signal (vch) changes to "L" and the overvoltage is cancelled.

When register ovc\_op is "101," the charge pump and pre-drivers remain off after the overvoltage is cancelled and NDIAG remains at "L."

When register ovc\_op is "001", "010", "011" or "100," the charge pump and pre-drivers operate normally but the status register is retained and NDIAG remains at "L."

When register ovc is cleared via the SPI, NDIAG changes to "H."

During an overvoltage, register ovc cannot be cleared and NDIAG output is "L."

Fig. 7.5.4-b Timing chart for VCC overvoltage detection

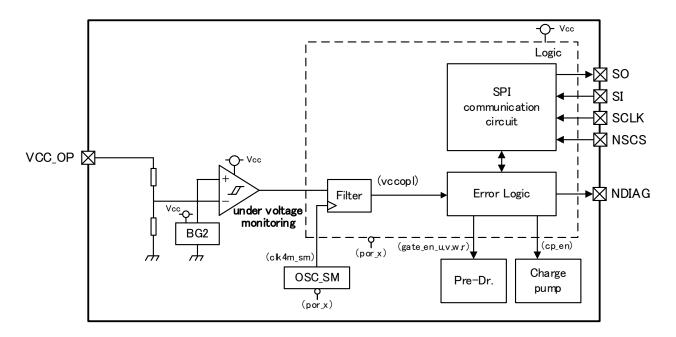

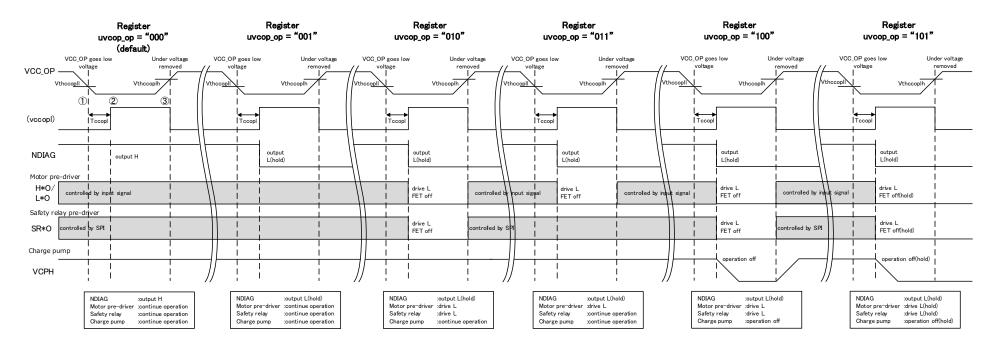

### 7.5.5. VCC\_OP undervoltage detection

This circuit comprises a comparator and a filter; filter output of "H" indicates undervoltage. The band gap voltage used as the baseline reference by the comparator is generated by the band gap circuit BG2.

Fig. 7.5.5-a Block diagram for VCC\_OP undervoltage detection

#### ➤ ① VCC OP voltage drops

VCC\_OP voltage drops below the undervoltage threshold Vthccopll. VCC\_OP L detection comparator outputs "H."

#### ➢ ② VCC OP undervoltage detected

After the detection filter time Tccopl has elapsed, VCC\_OP undervoltage signal (vccopl) "H" indicating undervoltage is generated and NDIAG becomes "L," except where the register uvccop\_op is "000," in which case NDIAG output remains at "H" and all circuits continue to operate as normal.

At this point one of six operating modes can be selected via the SPI.

If the mode is changed during VCC\_OP undervoltage, settings will not be enabled until the undervoltage is cancelled and the uvccop\_op register is cleared.

#### > ③ VCC OP voltage restored (undervoltage cancelled)

Once the VCC\_OP voltage rises above Vthccoplh, the VCC\_OP undervoltage signal (vccopl) changes to "L" and the undervoltage is cancelled.

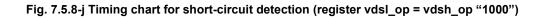

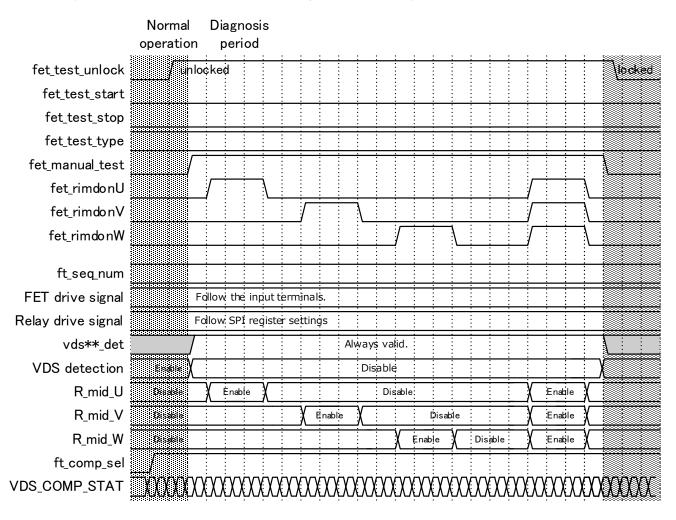

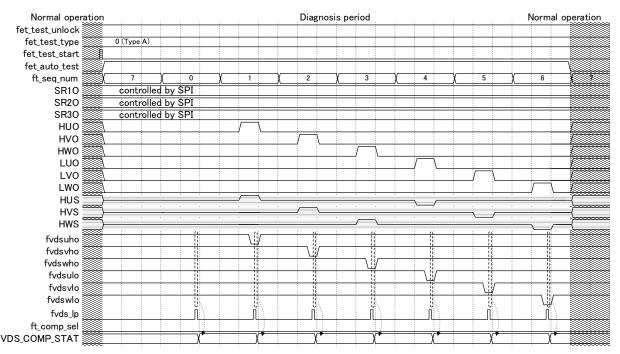

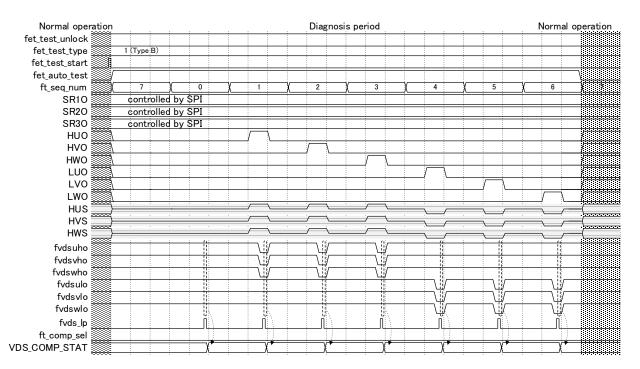

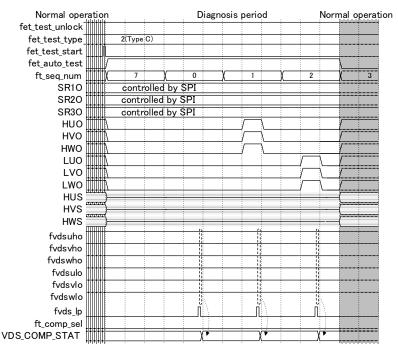

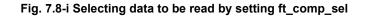

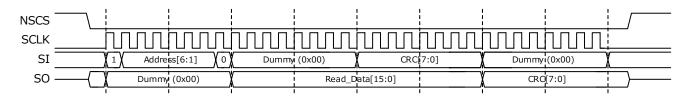

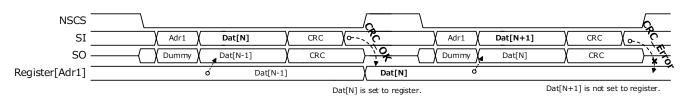

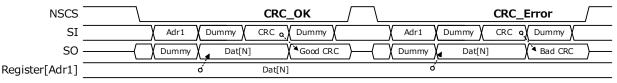

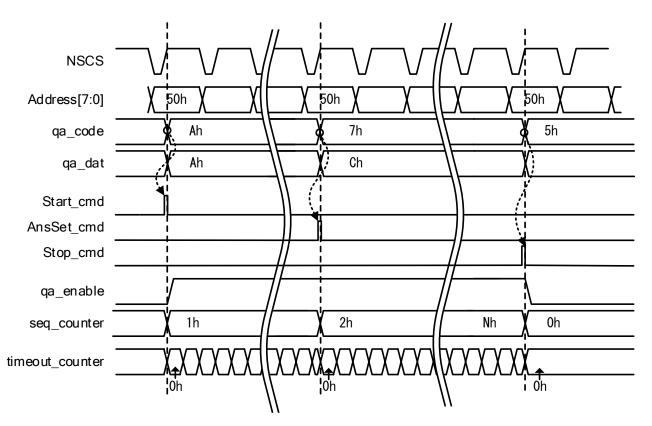

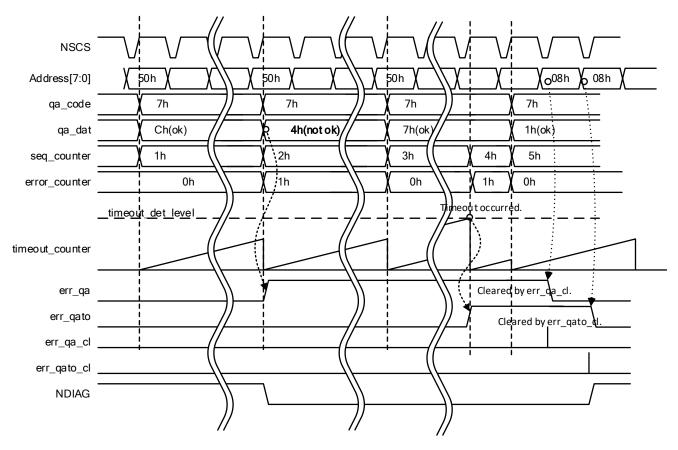

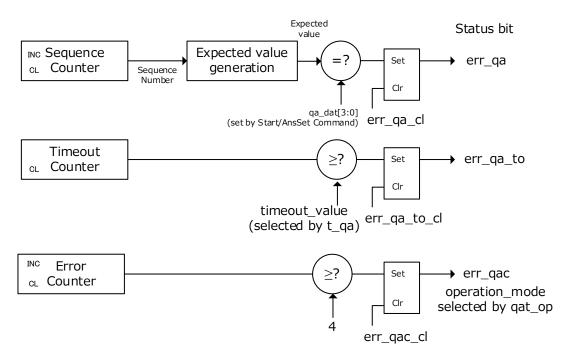

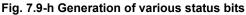

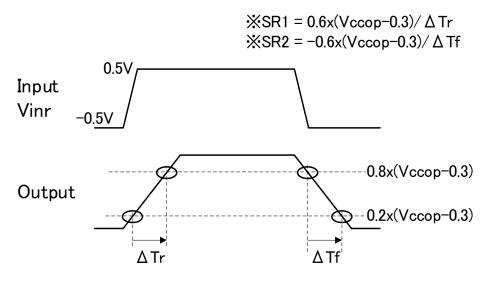

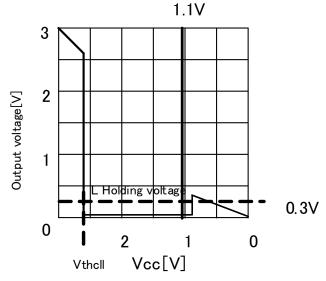

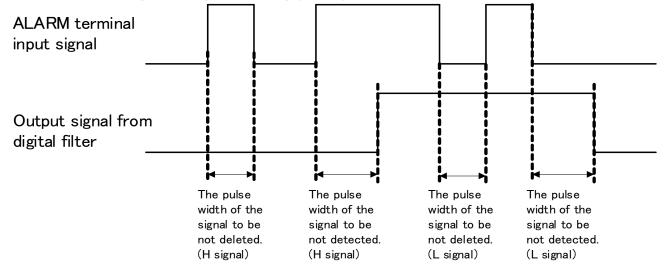

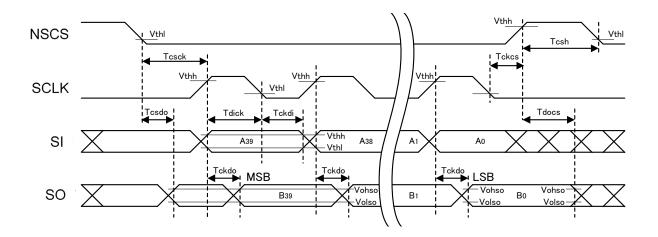

When register uvccop\_op is "101," the charge pump and pre-drivers remain off after the overvoltage is cancelled and NDIAG remains at "L."