# **32-bit RISC Microcontroller**

# TXZ+ Family TMPM3H Group(1)

# Reference Manual Clock Control and Operation Mode (CG-M3H(1)-D)

**Revision 1.7**

2025-05

**Toshiba Electronic Devices & Storage Corporation**

## Contents

| Contents                                                                                                   | 2          |

|------------------------------------------------------------------------------------------------------------|------------|

| List of Figures                                                                                            | 5          |

| List to Tables                                                                                             | 5          |

| Preface                                                                                                    | 6          |

| Related Documents                                                                                          | 6          |

| Conventions                                                                                                | 7          |

| Terms and Abbreviations                                                                                    | 9          |

| 1. Clock Control and Operation Mode                                                                        | 10         |

| 1.1. Outlines                                                                                              |            |

| 1.2. Clock Control                                                                                         |            |

| 1.2.1. Clock Type                                                                                          |            |

| 1.2.2. Initial Value by Reset Operation                                                                    |            |

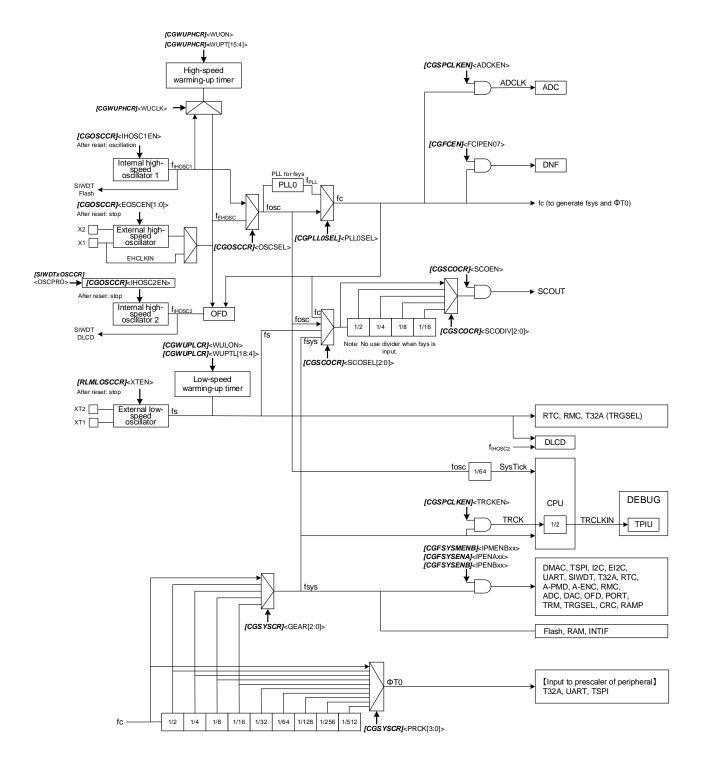

| 1.2.3. Clock System Diagram                                                                                |            |

| 1.2.4. Warming-up Function                                                                                 |            |

| 1.2.4.1. Warming-up Timer for High-speed Oscillation                                                       |            |

| 1.2.4.2. Warming-up Timer for Low-speed Oscillation                                                        |            |

| 1.2.4.3. Directions for Warming-up Timer                                                                   |            |

| 1.2.5. Clock Multiplying Circuit (PLL) for fsys                                                            | 15         |

| 1.2.5.1. PLL Setup after Reset Release                                                                     | 15         |

| 1.2.5.2. Formula and Example of Setting of PLL Multiplication Value                                        | 15         |

| 1.2.5.3. Change of PLL Multiplication Value under Operation                                                | 17         |

| 1.2.5.4. PLL Operation Start/Stop/Switching Procedure                                                      | 17         |

| 1.2.6. System Clock                                                                                        | 18         |

| 1.2.6.1. Setting Method of System Clock                                                                    | 19         |

| 1.2.7. Clock Supply Setting Function                                                                       | 21         |

| 1.2.8. Output Function of Clock in Terminal                                                                |            |

| 1.2.9. Prescaler Clock                                                                                     | 21         |

| 1.3. Operation Mode                                                                                        | 22         |

| 1.3.1. Details of Operation Mode                                                                           | 22         |

| 1.3.1.1. Feature in Each Mode                                                                              | 22         |

| 1.3.1.2. Low-power Consumption Mode                                                                        |            |

| 1.3.1.3. Selection of Low-power Consumption Mode                                                           |            |

| 1.3.1.4. Peripheral Function State in Low-power Consumption Mode                                           |            |

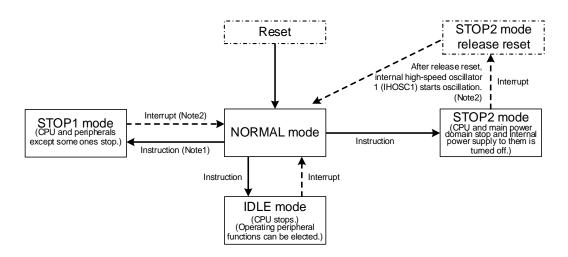

| 1.3.2. Mode State Transition                                                                               |            |

| 1.3.2.1. IDLE Mode Transition Flow                                                                         |            |

| 1.3.2.2. STOP1 Mode Transition Flow                                                                        |            |

| 1.3.2.3. STOP2 Mode Transition Flow                                                                        |            |

| 1.3.3. Return Operation from Low-power Consumption Mode                                                    |            |

| 1.3.3.1. Release Source of Low-power Consumption Mode                                                      |            |

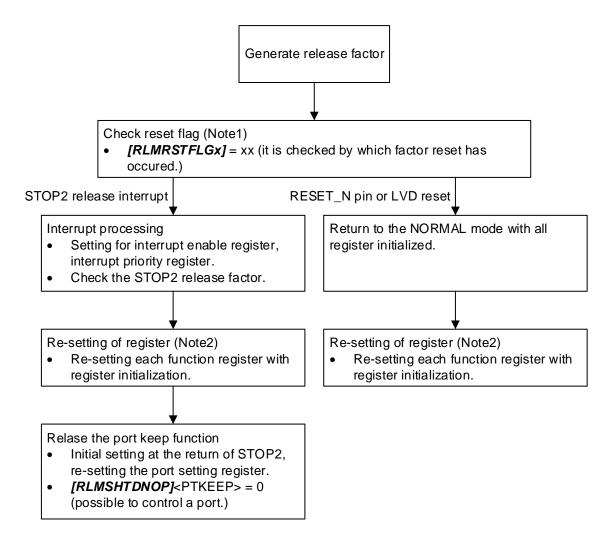

| 1.3.3.2. Warming up at Release of Low-power Consumption Mode<br>1.3.3.3. Restart Operation from STOP2 Mode |            |

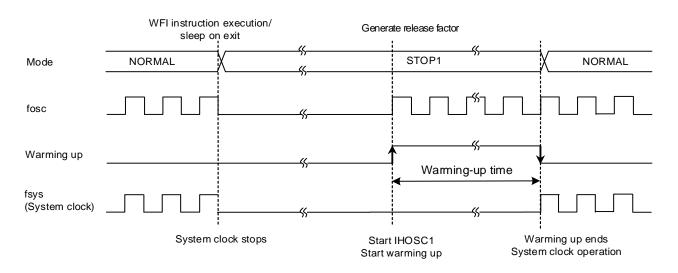

| 1.3.4. Clock Operation by Mode Transition                                                                  |            |

| 2 / 72                                                                                                     | 2025-05-27 |

# **TOSHIBA**

| 3.2.1.1. Reset by Power-on Reset Circuit (without Using RESET_N Pin)                                                       | 61 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2.1. Cold Reset                                                                                                          |    |

| 3.2. Function and Operation                                                                                                | 60 |

| 3.1. Outline                                                                                                               | 59 |

| 3. Power Supply and Reset Operation                                                                                        |    |

| 2.2.2.2. Peripheral Area                                                                                                   |    |

| 2.2.2.1. Code Area/SRAM Area                                                                                               |    |

| 2.2.2. Connection Table                                                                                                    | 57 |

| 2.2.1.2. Single Boot Mode                                                                                                  |    |

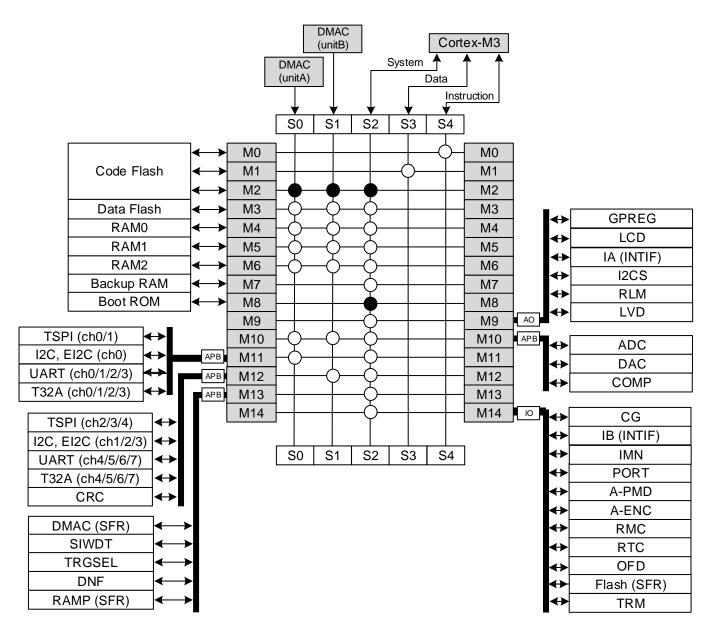

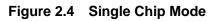

| 2.2.1.1. Single Chip Mode                                                                                                  | 55 |

| 2.2.1. Structure                                                                                                           | 55 |

| 2.2. Bus Matrix                                                                                                            | 55 |

| 2.1.3. TMPM3HxFYA                                                                                                          | 54 |

| 2.1.2. TMPM3HxFZA                                                                                                          | 53 |

| 2.1.1. TMPM3HxFDA                                                                                                          |    |

| 2.1. Overview                                                                                                              | 51 |

| 2. Memory Map                                                                                                              |    |

| 1.5.3. [CGFSYSENB]                                                                                                         | 50 |

| 1.5.2. [CGFSYSENA]                                                                                                         | 49 |

| 1.5.1. [CGFSYSMENB]                                                                                                        | 48 |

| 1.5. Information According to Product                                                                                      | 48 |

| 1.4.2.16. [RLMPROTECT] (RLM Write Protection Register)                                                                     |    |

| 1.4.2.15. [RLMSHTDNOP] (Power Supply Cut Off Control Register)                                                             |    |

| 1.4.2.14. [RLMLOSCCR] (Low-speed Oscillation Control Register)                                                             |    |

| 1.4.2.13. [CGSPCLKEN] (Clock Supply and Stop Register for ADC and Debug Circuit)                                           |    |

| 1.4.2.12. [CGFCEN] (Clock Supply and Stop Register for fc)                                                                 |    |

| 1.4.2.10. [CGFSYSENB] (Clock Supply and Stop Register A for fsys)                                                          |    |

| 1.4.2.10. [CGFSYSENA] (Clock Supply and Stop Register A for fsys)                                                          |    |

| 1.4.2.9. [CGFSYSMENB] (Clock Supply and Stop Register B for fsysm)                                                         |    |

| 1.4.2.7. [CGWUPHCR] (High-speed Oscillation Warming-up Register)                                                           |    |

| 1.4.2.6. [CGPLL0SEL] (PLL Selection Register for fsys)<br>1.4.2.7. [CGWUPHCR] (High-speed Oscillation Warming-up Register) |    |

| 1.4.2.5. [CGSCOCR] (SCOUT Output Control Register)                                                                         |    |

| 1.4.2.4. [CGSTBYCR] (Standby Control Register)                                                                             |    |

| 1.4.2.3. [CGSYSCR] (System Clock Control Register)                                                                         |    |

| 1.4.2.2. [CGOSCCR] (Oscillation Control Register)                                                                          |    |

| 1.4.2.1. [CGPROTECT] (CG Write Protection Register)                                                                        |    |

| 1.4.2. Register Description                                                                                                |    |

| 1.4.1.2. Low-speed Oscillation/Power Control (Note)                                                                        |    |

| 1.4.1.1. Clock and Mode Control                                                                                            | 35 |

| 1.4.1. Register List                                                                                                       | 35 |

| 1.4. Explanation of Register                                                                                               | 35 |

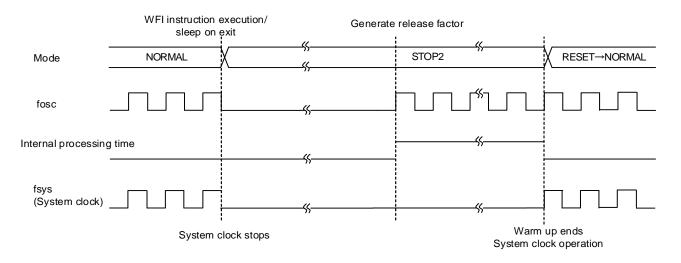

| 1.3.4.3. NORMAL $\rightarrow$ STOP2 $\rightarrow$ RESET $\rightarrow$ NORMAL Operation Mode Transition                     |    |

| 1.3.4.2. NORMAL $\rightarrow$ STOP1 $\rightarrow$ NORMAL Operation Mode Transition                                         |    |

| 1.3.4.1. NORMAL $\rightarrow$ IDLE $\rightarrow$ NORMAL Operation Mode Transition                                          |    |

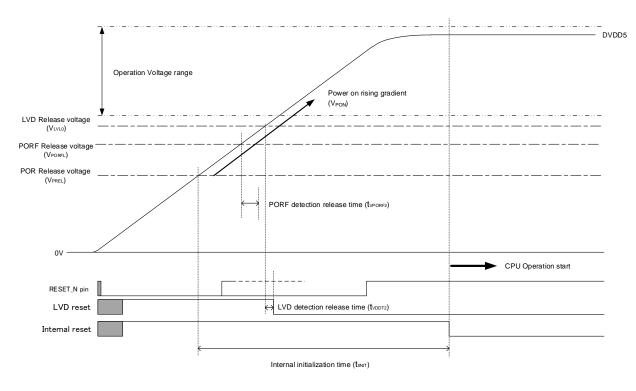

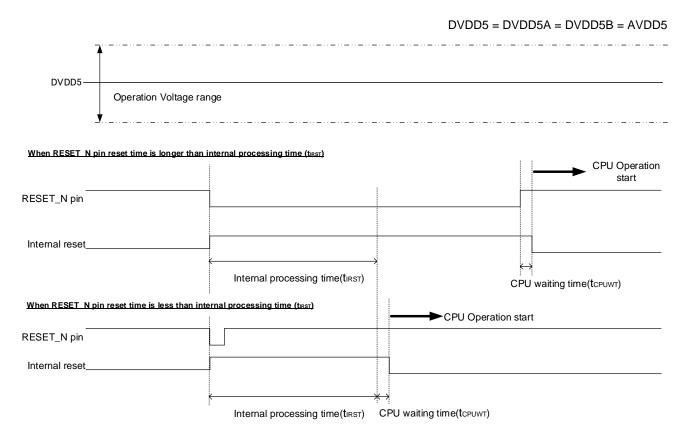

|    | 3.2.1.2. Reset by RESET_N Pin                                                | 62 |

|----|------------------------------------------------------------------------------|----|

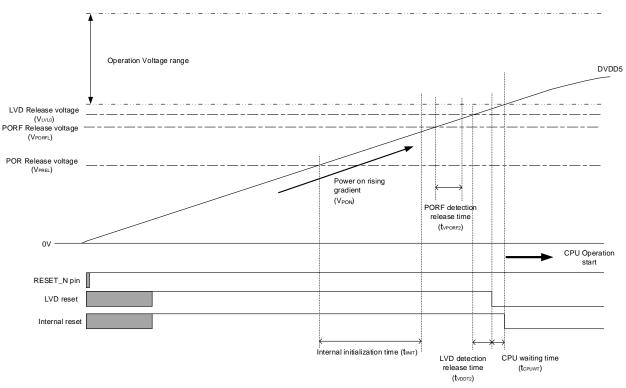

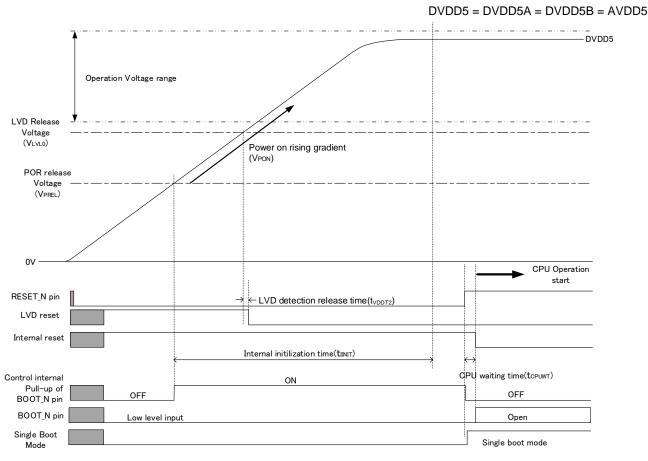

|    | 3.2.1.3. Continuation of Reset by LVD                                        | 64 |

|    | 3.2.2. Warm Reset                                                            | 65 |

|    | 3.2.2.1. Warm Reset by RESET_N Pin                                           | 65 |

|    | 3.2.2.2. Warm Reset by Internal Reset                                        | 65 |

|    | 3.2.3. Reset by STOP2 Mode Release                                           | 66 |

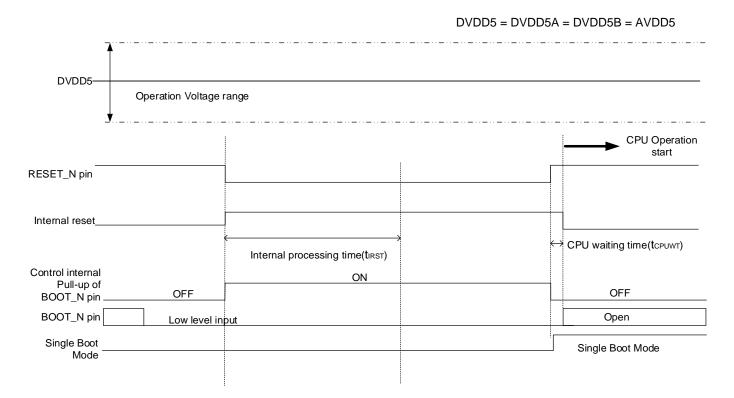

|    | 3.2.4. Starting in Reset and Single Boot Mode                                | 66 |

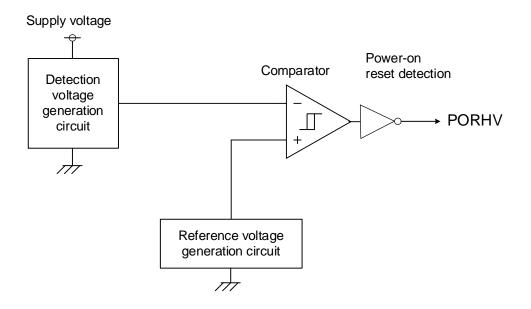

|    | 3.2.5. Power-on Reset Circuit                                                | 68 |

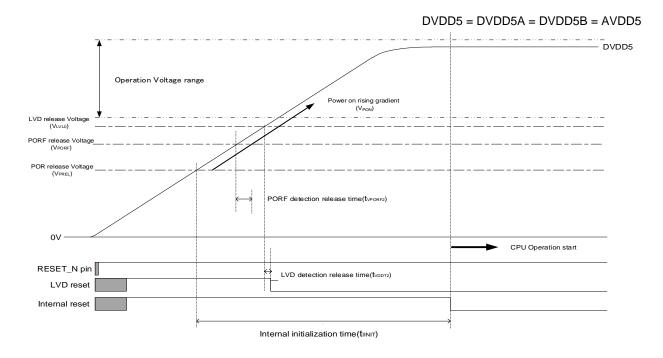

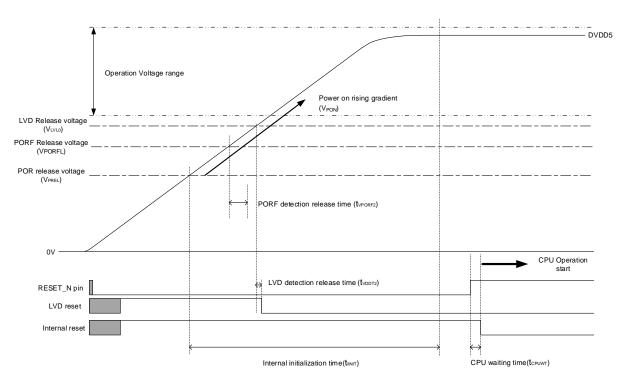

|    | 3.2.5.1. Operation at Time of Turn On                                        | 68 |

|    | 3.2.5.2. Operation at Time of Turn Off                                       | 68 |

|    | 3.2.6. Turning Off and Re-turning On Power Supply                            | 69 |

|    | 3.2.6.1. When Using External Reset Circuit or Internal LVD Reset Output      | 69 |

|    | 3.2.6.2. When not Using External Reset Circuit and Internal LVD Reset Output | 69 |

|    | 3.2.7. After Reset Release                                                   | 69 |

|    | 3.2.7.1. Reset Factor and Reset Initialized Range                            | 70 |

| 4. | Revision History                                                             | 71 |

| RE | STRICTIONS ON PRODUCT USE                                                    | 72 |

|    |                                                                              |    |

# List of Figures

| Figure 1.1 | Clock System Diagram                                                                          |    |

|------------|-----------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Mode State Transition                                                                         |    |

| Figure 1.3 | STOP2 Mode Restart Operation Flow                                                             | 32 |

| Figure 1.4 | NORMAL $\rightarrow$ STOP1 $\rightarrow$ NORMAL Operation Mode Transition                     | 33 |

| Figure 1.5 | NORMAL $\rightarrow$ STOP2 $\rightarrow$ RESET $\rightarrow$ NORMAL Operation Mode Transition |    |

| Figure 2.1 | TMPM3HxFD                                                                                     |    |

| Figure 2.2 | TMPM3HxFZ                                                                                     | 53 |

| Figure 2.3 | TMPM3HxFY                                                                                     | 54 |

| Figure 2.4 | Single Chip Mode                                                                              | 55 |

| Figure 2.5 | Single Boot Mode                                                                              | 56 |

| Figure 3.1 | Reset Operation by Power-on Reset Circuit                                                     | 61 |

| Figure 3.2 | Reset Operation by RESET_N Pin (1)                                                            | 62 |

| Figure 3.3 | Reset Operation by RESET_N Pin (2)                                                            | 63 |

| Figure 3.4 | Reset Operation by LVD Reset                                                                  | 64 |

| Figure 3.5 | Warm Reset Action                                                                             |    |

| Figure 3.6 | Starting in Power Supply is On and Single Boot Mode                                           | 66 |

| Figure 3.7 | Starting in Single Boot Mode when Power Supply is Stable                                      | 67 |

| Figure 3.8 | Power-on Reset Circuit                                                                        | 68 |

|            |                                                                                               |    |

## List to Tables

| Table 1.1  | Details of [CGPLL0SEL] <pll0set[23:0]> Setup</pll0set[23:0]> |    |

|------------|--------------------------------------------------------------|----|

| Table 1.2  | PLL Correction (Example)                                     |    |

| Table 1.3  | PLL0SET Set Point (Example)                                  |    |

| Table 1.4  | Example of Operation Frequency (Unit: MHz)                   |    |

| Table 1.5  | List of Use Propriety in Each Operation Mode                 |    |

| Table 1.6  | Low-power Consumption Mode Selection                         |    |

| Table 1.7  | Block Operation Status in Each Low-power Consumption Mode    | 24 |

| Table 1.8  | Release Source List                                          |    |

| Table 1.9  | Warming up                                                   |    |

| Table 1.10 | Allocation of [CGFSYSMENB] by Product                        | 48 |

| Table 1.11 | Allocation of [CGFSYSENA] by Product                         |    |

| Table 1.12 | Allocation of [CGFSYSENB] by Product                         | 50 |

| Table 2.1  | Single Chip Mode                                             | 57 |

| Table 2.2  | Single Boot Mode                                             | 57 |

| Table 2.3  | Peripheral Area                                              |    |

| Table 3.1  | Reset Factor and Initialized Range                           |    |

| Table 4.1  | Revision History                                             | 71 |

#### Preface

#### **Related Documents**

| Document name                                                                 |  |  |  |

|-------------------------------------------------------------------------------|--|--|--|

| ARM <sup>®</sup> Cortex <sup>®</sup> -M3 Processor Technical Reference Manual |  |  |  |

| The datasheet of each product (Electrical Characteristics)                    |  |  |  |

| Exception                                                                     |  |  |  |

| Oscillation Frequency Detector                                                |  |  |  |

| Voltage Detection Circuit                                                     |  |  |  |

| Clock Selective Watchdog Timer                                                |  |  |  |

| Flash Memory                                                                  |  |  |  |

# OSHIBA

#### Conventions

- Numeric formats follow the rules as shown below: Hexadecimal:

- 0xABC

- Decimal: 123 or 0d123 (Only when it needs to be explicitly shown that they are decimal numbers.) 0b111 (It is possible to omit the "0b" when the number of bits can be distinctly **Binary**: understood from a sentence.)

- "\_N" is added to the end of signal names to indicate low active signals.

- It is called "assert" that a signal moves to its active level, "deassert" to its inactive level.

- When two or more signal names are referred, they are described like as [m: n]. Example: S[3: 0] shows four signal names S3, S2, S1 and S0 together.

- The characters surrounded by [] defines the register. Example: [ABCD]

- "n" substitutes suffix number of two or more same kind of registers, fields, and bit names. Example:  $[XYZ1], [XYZ2], [XYZ3] \rightarrow [XYZn]$

- "x" substitutes suffix number or character of units and channels in the Register List. In case of unit, "x" means A, B, and C ... Example: [ADACR0], [ADBCR0], [ADCCR0] → [ADxCR0] In case of channel, "x" means 0, 1, and 2... Example:  $[T32A0RUNA], [T32A1RUNA], [T32A2RUNA] \rightarrow [T32AxRUNA]$

- The bit range of a register is written like as [m: n]. Example: Bit[3: 0] expresses the range of bit 3 to 0.

- The configuration value of a register is expressed by either the hexadecimal number or the binary number. Example: [ABCD] < EFG > = 0x01 (hexadecimal), [XYZn] < VW > = 1 (binary)

- Word and Byte represent the following bit length.

| 2            | 1       |

|--------------|---------|

| Byte:        | 8 bits  |

| Half word:   | 16 bits |

| Word:        | 32 bits |

| Double word: | 64 bits |

|              |         |

Properties of each bit in a register are expressed as follows:

| R:   | Read only                   |

|------|-----------------------------|

| W:   | Write only                  |

| R/W: | Read and Write are possible |

- Unless otherwise specified, register access supports only word access.

- The register defined as reserved must not be rewritten. Moreover, do not use the read value.

- The value read from the bit having default value of "-" is unknown.

- When a register containing both of writable bits and read-only bits is written, read-only bits should be written with their default value, In the cases that default is "-", follow the definition of each register.

- Reserved bits of the Write-only register should be written with their default value. In the cases that default is "-", follow the definition of each register.

- Do not use read-modified-write processing to the register of a definition which is different by writing and read out.

Arm, Cortex and Thumb are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

# arm

All other company names, product names, and service names mentioned herein may be trademarks of their respective companies.

#### **Terms and Abbreviations**

Some of abbreviations used in this document are as follows:

| ADC        | Analog to Digital Converter                      |

|------------|--------------------------------------------------|

| A-ENC      | Advanced Encoder input Circuit                   |

| APB        | Advanced Peripheral Bus                          |

| A-PMD      | Advanced Programmable Motor Control Circuit      |

| CG         | Clock control and Operation Mode                 |

| COMP       | Comparator                                       |

| CRC        | Cyclic Redundancy Check                          |

| DAC        | Digital to Analog Converter                      |

| DMAC       | Direct Memory Access Controller                  |

| DNF        | Digital Noise Filter                             |

| ELOSC      | External Low-speed Oscillator                    |

| EHOSC      | External High-speed Oscillator                   |

| EI2C       | I <sup>2</sup> C Interface Version A             |

| fsys       | frequency of SYSTEM Clock                        |

| I2C        | Inter-Integrated Circuit                         |

| I2CS       | Wake-up function by address matching             |

| IHOSC      | Internal High-speed Oscillator                   |

| IA (INTIF) | Interrupt control register A                     |

| IB (INTIF) | Interrupt control register B                     |

| I-Bus      | ICode memory interface                           |

| IMN        | Interrupt Monitor                                |

| INT        | Interrupt                                        |

| ΙΟ         | IO Bus (32bit Peripheral Bus)                    |

| LCD        | Liquid Crystal Display                           |

| LVD        | Voltage Detection Circuit                        |

| NMI        | Non-Maskable Interrupt                           |

| OFD        | Oscillation Frequency Detector                   |

| POR        | Power-on Reset Circuit                           |

| RAMP       | RAM Parity Circuit                               |

| RLM        | Low-speed oscillation/power supply control/reset |

| RMC        | Remote Control Signal Preprocessor               |

| RTC        | Real Time Clock                                  |

| S-Bus      | System interface                                 |

| SCOUT      | Source Clock Output                              |

| SIWDT      | Clock Selective Watchdog Timer                   |

| TPIU       | Trace Port Interface Unit                        |

| TRGSEL     | Trigger Selection Circuit                        |

| TRM        | Trimming Circuit                                 |

| TSPI       | Serial Peripheral Interface                      |

| T32A       | 32-bit Timer Event Counter                       |

| UART       | Asynchronous Serial Communication Circuit        |

|            |                                                  |

# 1. Clock Control and Operation Mode

## 1.1. Outlines

The clock/mode control block can select a clock gear and prescaler clock and set the warm up of oscillator and so on.

Furthermore, it has NORMAL mode and a low-power consumption mode in order to reduce power consumption using mode transition.

Functions related to a clock are as follows.

- System clock control

- Prescaler clock control

## 1.2. Clock Control

#### 1.2.1. Clock Type

This section shows a list of clocks.

| EHCLKIN:              | The clock input from the external.                                                     |

|-----------------------|----------------------------------------------------------------------------------------|

| fosc:                 | A clock generated in the internal oscillation circuit or input from the X1 and X2 pins |

| f <sub>PLL</sub> :    | A clock multiplied by PLL                                                              |

| fc:                   | A clock selected by [CGPLL0SEL] <pll0sel> (high-speed clock)</pll0sel>                 |

| fs:                   | A clock output from an external low-speed oscillator                                   |

| fsys:                 | A system clock selected by <i>[CGSYSCR]</i> <gear[2:0]></gear[2:0]>                    |

| ФТ0:                  | A clock selected by <i>[CGSYSCR]</i> <prck[3:0]> (prescaler clock)</prck[3:0]>         |

| f <sub>IHOSC1</sub> : | A clock generated with the internal high-speed oscillator 1                            |

| f <sub>IHOSC2</sub> : | A clock generated with the internal high-speed oscillator 2                            |

| ADCLK:                | A conversion clock for AD converter                                                    |

| TRCLKIN:              | A clock for tracing facilities of a debugging circuit (Trace/SWV)                      |

#### 1.2.2. Initial Value by Reset Operation

A clock setting is initialized to the following states by a reset operation.

| External high-speed oscillator:   | Stop                       |

|-----------------------------------|----------------------------|

| Internal high-speed oscillator 1: | Oscillation                |

| Internal high-speed oscillator 2: | Stop                       |

| External low-speed oscillator:    | Stop                       |

| PLL (multiplying circuit):        | Stop                       |

| Gear clock:                       | fc (no frequency dividing) |

#### 1.2.3. Clock System Diagram

The figure below shows a clock system diagram.

Figure 1.1 Clock System Diagram

#### 1.2.4. Warming-up Function

A warming-up function is used to secure the oscillation stable time at the time of the STOP1 mode release which starts the warming-up timer for high-speed oscillation automatically.

It is available also as a count up timer which uses the exclusive warming-up timer of high-speed clock /each low-speed clock for the waiting for the stability of an external oscillator or an internal oscillator.

This chapter explains the setting method to the register for warming-up timers, and the case where it is used as a count up timer. The detailed explanation at the time of STOP1 mode release, refer to "1.3.3.2 Warming up at Release of Low-power Consumption Mode".

#### 1.2.4.1. Warming-up Timer for High-speed Oscillation

A 16-bit up counter is built in as a warming-up timer only for a high-speed oscillation. Also when setting before changing to the STOP1 mode, the setting value is calculated in the following formula, set *[CGWUPHCR]*<WUPT[15:4]> to the upper 12 bits of the setting value. Lower 4 bits are ignored.

<Formula> (Using EHOSC)

> Warming-up timer setting value (16 bits) = - (warming-up time (s) / clock period (s)) -16

(Example) When 5 ms of warming-up time is set up with 10MHz (100ns of clock periods) of oscillators

Warming-up timer setting value (16 bits)

- = (5ms / 100ns) 16

- = 50000 16

- = 49984

- = 0xC340

Since upper 12 bits are set to a register, they are set as follows. [CGWUPHCR]<WUPT[15:4]> = 0xC34

(Using IHOSC1)

Warming-up timer setting value (16 bits) = - ((warming-up time (s) -63.3 ( $\mu$ s)) / clock period (s)) -41

(Example) When 163.4µs of warming-up time is set up with 10MHz (100ns of clock periods) of oscillators

Warming-up timer setting value (16 bits) = ((16)

= ((163.4-63.3) / 100ns) - 41 = (100.1µs / 100ns) - 41 = 960 = 0x03C0

Since upper 12 bits are set to register, they are set as follows.

*[CGWUPHCR]*<WUPT[15:4]> = 0x03C

In the case of 10MHz, the setting range is  $"0x03C" \le \langle WUPT[15:4] \rangle \le "0xFFF"$ , the warming-up time is set from 163.4µs to 6.6194ms.

#### **1.2.4.2.** Warming-up Timer for Low-speed Oscillation

A 19-bit up-timer is built in as a warming-up timer only for a low-speed oscillation. The setting value is calculated in the following formula, set *[CGWUPLCR]*<WUPT[18:4]> to the upper 15 bits of the setting value. Lower 4 bits are ignored. 16 is subtracted in order to perform the count for 4 bits of low ranks, even when a set point is "0".

<Formula>

Warming-up timer setting value (19 bits) = (warming-up time (s) / clock period (s)) - 16

(Example) When 50ms of warming-up time is set up with 32kHz (clock period 31.25 $\mu$ s) of oscillators Warming-up timer setting value (19 bits) = (50ms / 31.25 $\mu$ s) - 16 = 1600 - 16 = 1584

= 0x00630

Since upper 15 bits are set to a register, they are set as follows. [CGWUPLCR]<WUPTL[18:4]> = 0x0063

In the case of 32kHz, the setting range is  $0 \le <WUPTL[18:4] > \le 0x7FFF$ , the warming-up time is set from 500µs to 16.384s.

#### 1.2.4.3. Directions for Warming-up Timer

The directions for a warming-up function are explained.

- Selection of a clock

In a high-speed oscillation, the clock classification (internal oscillation/external oscillation) counted with a warming-up timer is selected by [CGWUPHCR]<WUCLK>.

- (2) Calculation of warming-up timer setting value The warming-up time can set any value to the timer for a high-speed oscillation/for a low-speed oscillation. Please compute and set up from each formula.

- (3) The start of warming up, and termination confirmation When software (instruction) performs to start warming up and to confirms termination of warming up, a warming-up timer starts by setting [CGWUPHCR]<WUON> (or [CGWUPLCR] <WULON>) to "1". Termination is confirmed with [CGWUPHCR]<WUEF> (or [CGWUPLCR]<WULEF>) that becomes from "1" to "0". "1" indicates under warming up and "0" indicates termination. After a counting end, a timer is reset and returns to an initial state. It is not forced to terminate, although "0" is written to [CGWUPHCR]<WUON> (or [CGWUPLCR]

<WULON>) during timer operation. Writing "0" is ignored.

Note: Since it is operating with the oscillating clock, a warming-up timer includes an error, when Oscillation frequency has fluctuation. Therefore, it should be taken as an approximate time.

#### 1.2.5. Clock Multiplying Circuit (PLL) for fsys

The clock multiplying circuit outputs the  $f_{PLL}$  clock (up to 120MHz) multiplied by the optimum condition for the frequency (6MHz to 12MHz) of the output clock fosc of the high-speed oscillator.

So, it is possible to make the input frequency to an oscillator low-speed and to make an internal clock high-speed by this circuit.

#### 1.2.5.1. PLL Setup after Reset Release

The PLL is disabled after reset release.

In order to use the PLL, set *[CGPLL0SEL]*<PLL0SET> to a multiplication value while *[CGPLL0SEL]* <PLL0ON> is "0". Then wait until approximately 100 µs has elapsed as a PLL initial stabilization time, and set <PLL0ON> to "1" to start PLL operation.

After that, to use  $f_{PLL}$  clock which is multiplied fosc, wait until approximately 400 µs has elapsed as a lock up time. Then set "1" to *[CGPLL0SEL]*<PLL0SEL>.

Note that a warm up time is required until PLL operation becomes stable using the warm up function, etc.

#### 1.2.5.2. Formula and Example of Setting of PLL Multiplication Value

The details of the items of *[CGPLL0SEL]*<PLL0SET[23:0]> which set up a PLL multiplication value are shown below.

| Items of PLL0SET | Function                                |                                                                                                                              |                                                                                                                              |

|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| [23:17]          | Correction value setting                | The quotient of fosc/450k (integer). For detail refer to Table 1.2                                                           |                                                                                                                              |

| [16:14]          | fosc setting                            | 000: $6 \le 6 \le 7$<br>001: $7 < 6 \le 8$<br>010: $8 < 6 \le 10$<br>011: $10 < 6 \le 12$<br>(Unit: MHz)                     | 100: 12 < fosc ≤ 15<br>101: 15 < fosc ≤ 19<br>110: 19 < fosc ≤ 24<br>111: Reserved                                           |

| [13:12]          | Dividing setting                        | 00: Reserved<br>01: 2 dividing (x 1 / 2)<br>10: 4 dividing (x 1 / 4)<br>11: 8 dividing (x 1 / 8)                             |                                                                                                                              |

| [11:8]           | Fraction part<br>Multiplication setting | 0000: 0.0000<br>0001: 0.0625<br>0010: 0.1250<br>0011: 0.1875<br>0100: 0.2500<br>0101: 0.3125<br>0110: 0.3750<br>0111: 0.4375 | 1000: 0.5000<br>1001: 0.5625<br>1010: 0.6250<br>1011: 0.6875<br>1100: 0.7500<br>1101: 0.8125<br>1110: 0.8750<br>1111: 0.9375 |

| [7:0]            | Integer part<br>Multiplication setting  | 0x00: 0<br>0x01: 1<br>0x02: 2<br>:<br>0xFD: 253<br>0xFE: 254<br>0xFF: 255                                                    |                                                                                                                              |

Table 1.1 Details of [CGPLL0SEL]<PLL0SET[23:0]> Setup

Note: A multiplication value is the total of <PLL0SET[7:0]> (integer part) and <PLL0SET[11:8]> (fraction part).

f<sub>PLL</sub> is denoted by the following formulas.

$f_{PLL} = foscosc \times ([CGPLL0SEL] < PLL0SET[7:0] > + [CGPLL0SEL] < PLL0SET[11:8] >) \times$ ([CGPLL0SEL] <PLL0SET[13:12]>)

Note1. The absolute value of frequency accuracy is not guaranteed.

Note2. There is no Linearity in the frequency by the fractional part Multiplication setup.

Note3:  $f_{PLL} \leq$  (Maximum Operating Frequency)

| fosc (MHz) | <pll0set [23:17]=""> (decimal, integral value)</pll0set> |

|------------|----------------------------------------------------------|

| 6.00       | 14                                                       |

| 8.00       | 18                                                       |

| 10.00      | 23                                                       |

| 12.00      | 27                                                       |

Table 1.2 PLL Correction (Example)

A PLL correction can be calculated below.

When fosc = 6.0MHz,  $6.0 / 0.45 = 13.33 \approx 14$ ; A fractional part is rounded up.

The main examples of a setting of [CGPLL0SEL]<PLL0SET[23:0]> are shown below.

- (1) It multiplies by PLL, and dividing is carried out and the target Clock frequency ( $f_{PLL}$ ) is generated for input frequency (fosc).

- (2) A dividing value is chosen from 1/2, 1/4, and 1/8.

- (3) Moreover, set up the frequency after multiplication in the following ranges.  $200MHz \le (fosc \times multiplication value) \le 320MHz$

| fosc (MHz) | Multiplication<br>value | Dividing<br>value | f <sub>PLL</sub> (MHz) | <pll0set[23:0]></pll0set[23:0]> |  |  |

|------------|-------------------------|-------------------|------------------------|---------------------------------|--|--|

| 6.00       | 40.0000                 | 1/2               | 120.00                 | 0x1C1028                        |  |  |

| 8.00       | 30.0000                 | 1/2               | 120.00                 | 0x24501E                        |  |  |

| 10.00      | 24.0000                 | 1/2               | 120.00                 | 0x2E9018                        |  |  |

| 12.00      | 20.0000                 | 1/2               | 120.00                 | 0x36D014                        |  |  |

| 6.00       | 53.3125                 | 1/4               | 79.97                  | 0x1C2535                        |  |  |

| 8.00       | 40.0000                 | 1/4               | 80.00                  | 0x246028                        |  |  |

| 10.00      | 32.0000                 | 1/4               | 80.00                  | 0x2EA020                        |  |  |

| 12.00      | 26.6250                 | 1/4               | 79.88                  | 0x36EA1A                        |  |  |

| 6.00       | 53.3125                 | 1/8               | 39.98                  | 0x1C3535                        |  |  |

| 8.00       | 40.0000                 | 1/8               | 40.00                  | 0x247028                        |  |  |

| 10.00      | 32.0000                 | 1/8               | 40.00                  | 0x2EB020                        |  |  |

| 12.00      | 26.6250                 | 1/8               | 39.94                  | 0x36FA1A                        |  |  |

| Table 1.3 | PLL0SET | Set Point | (Example) |

|-----------|---------|-----------|-----------|

|-----------|---------|-----------|-----------|

#### 1.2.5.3. Change of PLL Multiplication Value under Operation

It changes to a setup which sets "0" to *[CGPLL0SEL]*<PLL0SEL> first, and does not use a PLL multiplication clock during PLL multiplication clock operation when changing a multiplication value. And *[CGPLL0SEL]*<PLL0ST> = 0 is read, after checking having changed to a setup which does not use a multiplication clock, *[CGPLL0SEL]*<PLL0ON> is set to "0", and PLL is stopped.

Then, the multiplication value of *[CGPLL0SEL]*<PLL0SET> is changed, as reset time of PLL, after about 100µs progress, *[CGPLL0SEL]*<PLL0ON> is set to "1", and operation of PLL is started.

Then, *[CGPLL0SEL]*<PLL0SEL> is set to "1" after lock up time (about 400µs) has elapsed.

Finally, *[CGPLL0SEL]*<PLL0ST> is read and it checks having changed.

#### 1.2.5.4. PLL Operation Start/Stop/Switching Procedure

(1) fc setup (PLL stop  $\rightarrow$  PLL start)

As an fc setup, the example of switching procedure from the PLL stop state to the PLL operation state is as follows.

| < <state before="" switching="">&gt;</state>                                                       |                                                                    |  |

|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| [CGPLL0SEL] <pll0on> = 0</pll0on>                                                                  | Stops the PLL operation for fsys.                                  |  |

| [CGPLL0SEL] <pll0sel> = 0</pll0sel>                                                                | Selects the setting of the PLL for fsys to "PLL is unused (fosc)". |  |

| [CGPLL0SEL] <pll0st> = 0 Indicates the status of the PLL for fsys to "PLL is unused (fosc</pll0st> |                                                                    |  |

|   | < <example of="" procedure="" switching="">&gt;</example> |                                                                                       |  |  |  |

|---|-----------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| 1 | [CGPLL0SEL] <pll0set> = 0xX</pll0set>                     | A PLL multiplication value setup is chosen.                                           |  |  |  |

| 2 | Wait 100µs or more                                        | Latency time after a multiplication setup                                             |  |  |  |

| 3 | [CGPLL0SEL] < PLL0ON > = 1                                | PLL operation for fsys is carried out to an oscillation.                              |  |  |  |

| 4 | Wait 400µs or more                                        | PLL output clock stable latency time                                                  |  |  |  |

| 5 | [CGPLL0SEL] <pll0sel> = 1</pll0sel>                       | PLL selection for fsys is carried out to PLL use (f <sub>PLL</sub> ).                 |  |  |  |

| 6 | Read [CGPLL0SEL] <pll0st></pll0st>                        | It waits until the PLL selection status for fsys becomes "PLL use $(f_{PLL})$ (= 1)". |  |  |  |

Note: 1 to 4 is unnecessary when the state before switching is *[CGPLL0SEL]*<PLL0ON> = 1. When changing from the state where the PLL Output clock was stabilized, it can change to the conduct PLL state by execution of only 5 and 6.

(2) fc setup (PLL operation  $\rightarrow$  PLL stop)

As an fc setup, the example of switching procedure from the PLL operation state to a PLL stop state is as follows.

| < <state before="" switching="">&gt;</state> |                                                                   |  |

|----------------------------------------------|-------------------------------------------------------------------|--|

| [CGPLL0SEL] <pll0on> = 1</pll0on>            | Sets the PLL oscillation for fsys.                                |  |

| [CGPLL0SEL] <pll0sel> = 1</pll0sel>          | Selects the PLL for fsys to "PLL is used (fPLL)".                 |  |

| <b>[CGPLL0SEL]</b> <pll0st> = 1</pll0st>     | Indicates the status of the PLL for fsys to "PLL is used (fPLL)". |  |

|   | < <example of="" procedure="" switching="">&gt;</example> |                                                                                  |  |  |  |

|---|-----------------------------------------------------------|----------------------------------------------------------------------------------|--|--|--|

| 1 | [CGPLL0SEL] <pll0sel> = 0</pll0sel>                       | Selects the PLL for fsys to "PLL is unused (fosc)".                              |  |  |  |

| 2 | <b>[CGPLL0SEL]</b> <pll0st> , it read.</pll0st>           | Waits until the status of the PLL for fsys becomes "PLL is unused (fosc) (= 0)". |  |  |  |

| 3 | [CGPLL0SEL] <pll0on> = 0</pll0on>                         | Sets the PLL operation for fsys to stop.                                         |  |  |  |

#### 1.2.6. System Clock

An internal high-speed oscillation clock or external high-speed oscillation clock (connected oscillator or clock input) can be used as a source of system clock.

Dividing is possible for a system clock at *[CGSYSCR]*<GEAR[2:0]> (clock gear). Although a setup can be changed during operation, after register writing before a clock actually changes, a maximum of 16-clock time is required of fc. Check completion of a clock change by *[CGSYSCR]*<GEARST[2:0]>.

Note: Do not change a clock gear during operation of peripheral functions, such as a timer counter.

Table 1.4 shows the example of operation frequency by the clock gear ratio (1/1 to 1/16) to the frequency fc set up with oscillation frequency, a PLL multiplication value, etc.

| External oscillation | External clock | Internal oscillation | PLL<br>multiplication<br>value | Maximum                 |       |       | lock ge<br>PLL = O |      |      |     |     | lock ge<br>LL = OF |      |      |

|----------------------|----------------|----------------------|--------------------------------|-------------------------|-------|-------|--------------------|------|------|-----|-----|--------------------|------|------|

| (MHz)                | input<br>(MHz) | IHOSC1<br>(MHz)      | (After<br>dividing)            | frequency<br>(fc) (MHz) | 1/1   | 1/2   | 1/4                | 1/8  | 1/16 | 1/1 | 1/2 | 1/4                | 1/8  | 1/16 |

| 6                    | 6              | -                    | 20                             | 120                     | 120   | 60    | 30                 | 15   | 7.5  | 6   | 3   | 1.5                | -    | -    |

| 8                    | 8              | -                    | 15                             | 120                     | 120   | 60    | 30                 | 15   | 7.5  | 8   | 4   | 2                  | 1    | -    |

| 10                   | 10             | 10                   | 12                             | 120                     | 120   | 60    | 30                 | 15   | 7.5  | 10  | 5   | 2.5                | 1.25 | -    |

| 12                   | 12             | -                    | 10                             | 120                     | 120   | 60    | 30                 | 15   | 7.5  | 12  | 6   | 3                  | 1.5  | -    |

| 6                    | 6              | -                    | 13.329                         | 79.97                   | 79.97 | 39.99 | 20                 | 10   | 5    | 6   | 3   | 1.5                | -    | -    |

| 8                    | 8              | -                    | 10                             | 80                      | 80    | 40    | 20                 | 10   | 5    | 8   | 4   | 2                  | 1    | -    |

| 10                   | 10             | 10                   | 8                              | 80                      | 80    | 40    | 20                 | 10   | 5    | 10  | 5   | 2.5                | 1.25 | -    |

| 12                   | 12             | -                    | 6.657                          | 79.88                   | 79.88 | 39.95 | 19.98              | 9.99 | 4.99 | 12  | 6   | 3                  | 1.5  | -    |

| 6                    | 6              | -                    | 6.625                          | 39.75                   | 39.75 | 19.9  | 9.94               | 4.97 | 2.48 | 6   | 3   | 1.5                | -    | -    |

| 8                    | 8              | -                    | 5                              | 40                      | 40    | 20    | 10                 | 5    | 2.5  | 8   | 4   | 2                  | 1    | -    |

| 10                   | 10             | 10                   | 4                              | 40                      | 40    | 20    | 10                 | 5    | 2.5  | 10  | 5   | 2.5                | 1.25 | -    |

| 12                   | 12             | -                    | 3.3125                         | 39.75                   | 39.75 | 19.9  | 9.94               | 4.97 | 2.48 | 12  | 6   | 3                  | 1.5  | -    |

#### Table 1.4 Example of Operation Frequency (Unit: MHz)

#### 1.2.6.1. Setting Method of System Clock

fosc setup (internal oscillation → external oscillation)

As a fosc setup, the example of switching procedure to the external oscillation (EHOSC) from an internal oscillation (IHOSC1) is shown below.

| < <state before="" switching="">&gt;</state>    |                                                                             |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| [CGOSCCR] <ihosc1en> = 1</ihosc1en>             | An internal high-speed oscillator 1 oscillates.                             |  |  |  |

| [CGOSCCR] <oscsel> = 0</oscsel>                 | The high-speed oscillation selection for fosc is an inside (IHOSC1).        |  |  |  |

| <b>[CGOSCCR]</b> <oscf> = 0</oscf>              | The high-speed oscillation selection status for fosc is an inside (IHOSC1). |  |  |  |

| An oscillator is connected to X1/X2 pin. (Note) |                                                                             |  |  |  |

Note: Do not connect except a resonator.

|   | < <example of="" procedure="" switching="">&gt;</example>                                      |                                                                                                                                                           |  |  |  |

|---|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1 | <b>[PHPDN]</b> <bit[1:0]> = 00<br/><b>[PHIE]</b><bit[1:0]> = 00</bit[1:0]></bit[1:0]>          | Disable the pull-down of X1/X2 pin.<br>Disable input control of X1/X2 pin.                                                                                |  |  |  |

| 2 | [CGOSCCR] <eoscen[1:0]> = 01</eoscen[1:0]>                                                     | It is an external oscillation (EHOSC) about selection of an external oscillation of operation.                                                            |  |  |  |

| 3 | [CGWUPHCR] <wuclk> = 1<br/>[CGWUPHCR]<wupt[18:4]> = "arbitrary<br/>value"</wupt[18:4]></wuclk> | It is the external (EHOSC) about high-speed oscillation warming-up clock selection.<br>Oscillator stable time is set to a warming-up timer setting value. |  |  |  |

| 4 | [CGWUPHCR] <wuon> = 1</wuon>                                                                   | High-speed oscillation warming up is started.                                                                                                             |  |  |  |

| 5 | [CGWUPHCR] <wuef> is read.</wuef>                                                              | It waits until it becomes the termination of high-speed oscillation warming up (= $0$ ).                                                                  |  |  |  |

| 6 | [CGOSCCR] <oscsel> = 1</oscsel>                                                                | It is high-speed oscillation selection for fosc to the exterior (EHOSC).                                                                                  |  |  |  |

| 7 | [CGOSCCR] <oscf> is read.</oscf>                                                               | It waits until the high-speed oscillation selection status for fosc becomes outside (= 1).                                                                |  |  |  |

| 8 | [CGOSCCR] <ihosc1en> = 0</ihosc1en>                                                            | An internal high-speed oscillator 1 is suspended.                                                                                                         |  |  |  |

(2) fosc setup ( internal oscillation  $\rightarrow$  external clock input)

As a fosc setup, the example of switching procedure to the external clock input (EHCLKIN) from an internal oscillation 1 (IHOSC1) is shown below.

| < <state before="" switching="">&gt;</state>                                        |                                                                             |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| [CGOSCCR] <ihosc1en> = 1 An internal high-speed oscillator 1 oscillates.</ihosc1en> |                                                                             |  |

| [CGOSCCR] <oscsel> = 0</oscsel>                                                     | The high-speed oscillation selection for fosc is an inside (IHOSC1).        |  |

| [CGOSCCR] <oscf> = 0</oscf>                                                         | The high-speed oscillation selection status for fosc is an inside (IHOSC1). |  |

| Clock input to EHCLKIN                                                              | Input in the proper voltage range.                                          |  |

|   | < <example of="" procedure="" switching="">&gt;</example>                     |                                                                        |  |  |  |

|---|-------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| 1 | <b>[PHPDN]</b> <bit[0]> = 0<br/><b>[PHIE]</b><bit[0]> = 0/1</bit[0]></bit[0]> | Disable the pull-down of X1 pin.                                       |  |  |  |

|   | <i>[PHIE]</i><br>bit[0]> = 0/1                                                | The input control of X1/EHCLKIN pin is arbitrary.                      |  |  |  |

| 2 | <b>[CGOSCCR]</b> <eoscen[1:0]> = 10</eoscen[1:0]>                             | Selection of an external oscillation of operation is carried out to an |  |  |  |

| 2 | [COOSCER] < COSCEN[1.0] > = 10                                                | external clock input (EHCLKIN).                                        |  |  |  |

| 3 | [CGOSCCR] <oscsel> = 1</oscsel>                                               | It is high-speed oscillation selection for fosc to an external clock.  |  |  |  |

| 4 | [CGOSCCR] <oscf> is read.</oscf>                                              | It waits until the high-speed oscillation selection status for fosc    |  |  |  |

| 4 | [COUSCER]<03CF> Is read.                                                      | becomes outside (= 1).                                                 |  |  |  |

| 5 | [CGOSCCR] <ihosc1en> = 0</ihosc1en>                                           | An internal high-speed oscillator 1 is suspended.                      |  |  |  |

(3) fosc setup (an external oscillation/external clock input → an internal oscillation) As a fosc setup, the example of switching procedure to the internal oscillation (IHOSC1) from an external oscillation (EHOSC) or an external clock input (EHCLKIN) is shown below.

| << State before switching >>                     |                                                                                                             |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| [CGOSCCR] <eoscen[1:0]> = 01 or 10</eoscen[1:0]> | Selection of an external oscillator of operation is an external oscillator (EHOSC) or external clock input. |  |

| [CGOSCCR] <oscsel> = 1</oscsel>                  | The high-speed oscillation selection for fosc is the exterior (EHOSC).                                      |  |

| <b>[CGOSCCR]</b> <oscf> = 1</oscf>               | The high-speed oscillation selection status for fosc is the exterior (EHOSC).                               |  |

|   | << Example of switching procedure >>                |                                                                                                    |  |  |

|---|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| 1 | <b>[CGWUPHCR]</b> <wuclk> = 0</wuclk>               | Set the warming-up clock selection to internal high-speed oscillator 1 (IHOSC1).                   |  |  |

| 2 | <b>[CGWUPHCR]</b> <wupt[15:4]> = 0x03C</wupt[15:4]> | Set the high-speed oscillation warming-up timer setting value of 163.4µs (= 0x3C) or more.         |  |  |

| 3 | [CGOSCCR] <ihosc1en> = 1</ihosc1en>                 | An internal high-speed oscillator 1 oscillates.                                                    |  |  |

| 4 | <b>[CGWUPHCR]</b> <wuon> = 1</wuon>                 | Start the high-speed oscillation warming-up timer                                                  |  |  |

| 5 | [CGWUPHCR] <wuef> is read.</wuef>                   | Wait until warming-up timer status flag becomes ends (= 0).                                        |  |  |

| 6 | <b>[CGOSCCR]</b> <oscsel> = 0</oscsel>              | Set the high-speed oscillation selection for fosc to internal high-<br>speed oscillator1 (IHOSC1). |  |  |

| 7 | [CGOSCCR] <oscf> is read.</oscf>                    | It waits until the high-speed oscillation selection status for fosc becomes an inside (= 0).       |  |  |

| 8 | [CGOSCCR] <eoscen[1:0]> = 00</eoscen[1:0]>          | Set the selection of an external oscillator operation to unused.                                   |  |  |

#### 1.2.7. Clock Supply Setting Function

This MCU has the clock on/off function for the peripheral circuits. To reduce the power consumption, this CPU can stop supplying the clock to the peripheral functions that are not used.

Except some peripheral functions, clocks are not supplied after reset.

In order to supply the clock of the function to be used, set the bit of relevance of *[CGFSYSENA]*, *[CGFSYSENB]*, *[CGFSYSMENB]* and *[CGSPCLKEN]* to "1".

For details, refer to "1.5. Explanation of Register".

#### 1.2.8. Output Function of Clock in Terminal

This MCU has the clock output function to the terminal. A low-speed clock "fs", high-speed oscillation clock "fosc", high-speed clock "fc", system clock "fsys" can be output from the SCOUT pin. For details, refer to "1.4.2.5. *[CGSCOCR]* (SCOUT Output Control Register)".

The below table shows the use propriety state of SCOUT pin in each operation mode.

|                 |             | Operation mode |       |

|-----------------|-------------|----------------|-------|

| SCOUT selection | NORMAL/IDLE | STOP1          | STOP2 |

| Fosc            | Yes         | N/A            | N/A   |

| Fc              | Yes         | N/A            | N/A   |

| fs              | Yes         | Yes            | N/A   |

| fsys            | Yes         | N/A            | N/A   |

Table 1.5

List of Use Propriety in Each Operation Mode

#### 1.2.9. Prescaler Clock

Each peripheral function has a prescaler circuit to divide the  $\Phi$ T0 clock. The  $\Phi$ T0 clock inputted into the prescaler circuit can be divided by the *[CGSYSCR]*<PRCK[3:0]>. As for  $\Phi$ T0 clock after reset, fc is selected.

After register writing before a clock actually changes, a time up to 512-clock of fc is required. To confirm the completion of the clock changed, check the status of *[CGSYSCR]*<PRCKST[3:0]>.

Note: Do not change a prescaler clock during operation of peripheral functions, such as a timer counter.

## 1.3. Operation Mode

There are NORMAL mode and a low-power consumption mode (IDLE, STOP1, STOP2) in this product as an operation mode, and it can reduce power consumption by performing mode changes according to directions for use.

#### 1.3.1. Details of Operation Mode

#### 1.3.1.1. Feature in Each Mode

The feature in NORMAL, low-power consumption mode are follows.

• NORMAL mode

It is a mode to operate a CPU core and peripheral circuits. After the reset release, operation mode is NORMAL mode.

- Low-power consumption mode Low-power consumption mode is as following.

- IDLE mode

It is the mode which CPU stops.

The peripheral function should perform operation/stop by the register of each peripheral function, a clock supply setting function, etc.

Note: CPU cannot clear the watchdog timer in IDLE mode.

STOP1 mode

It is the mode which all the internal circuits also including an internal oscillator stop.

However, when an external low-speed oscillator is oscillated and it shifts to the STOP1 mode, the RTC operates.

If the STOP1 mode is released, an internal high-speed oscillator1 (IHOSC1) will start, and operation mode will return to NORMAL mode.

Please disable interrupt which is not used for STOP1 release before shifting to the STOP1 mode.

- STOP2 mode

It is the mode which holds a part of the function and cut off an internal electrical power source. STOP1 Consumption of electric power larger than the STOP2 mode can be held down. If the STOP2 mode is released, the power supply will be switched on to the Main power domain, a reset sequence will be performed, and it will return to NORMAL mode.

As for the Main power domain, it is a function which does not supply a power supply in STOP2 mode.

Before shifting to the STOP2 mode, disable an interrupt which is not made into a release STOP2, please be sure to set up *[RLMSHTDNOP]*<PTKEEP> = 1 and to hold the state of each port.

An Output/Pull up holds, and input permission holds a state when it sets as a port keeping function. In addition, external interrupt continues an input.

The product will be cut off the power except for the following circuit in STOP2 mode.

- External low-speed oscillator (ELOSC)

- RTC

- Backup RAM

- Port pin status

- LVD

- RLM

- IA

- I2C Wake up

- LCD

Regarding a power supply cutoff in the Low-power consumption mode, for details, refer to "1.3.1.4. Peripheral Function State in Low-power Consumption Mode".

#### 1.3.1.2. Low-power Consumption Mode

In order to shift to each low-power consumption mode, the IDLE/STOP1/STOP2 mode is chosen by standby control register *[CGSTBYCR]*<STBY[1:0] >, and a WFI command is executed. When it shifts to a Low Power Consumption mode by WFI command, the restart operation from a Low Power Consumption mode is performed by reset or interrupt generating. To return by an interrupt, it is necessary to set up. Please refer to "Interrupt" chapter of the reference manual "Exception" for details.

- Note1: This product does not support a return by events; therefore, do not make a transition to low-power consumption mode triggered by WFE (Wait For Event).

- Note2: This product does not support low-power consumption mode by SLEEPDEEP of the Cortex-M3 core. Do not use the <SLEEPDEEP> bit of the system control register.

#### 1.3.1.3. Selection of Low-power Consumption Mode

Low-power consumption mode selection is chosen by the setup of *[CGSTBYCR]*<STBY [1:0]>. Following table shows the mode chosen from a setup of <STBY [1:0]>.

| Mode  | [CGSTBYCR] <stby[1:0]></stby[1:0]> |

|-------|------------------------------------|

| IDLE  | 00                                 |

| STOP1 | 01                                 |

| STOP2 | 10                                 |

| Table 1.6 | Low-power | Consumption | <b>Mode Selection</b> |

|-----------|-----------|-------------|-----------------------|

|-----------|-----------|-------------|-----------------------|

Note: Do not use the settings other than the above.

#### 1.3.1.4. Peripheral Function State in Low-power Consumption Mode

The following Table 1.7 shows the Operation State of the peripheral function (block) in each mode. In addition, after reset release it will be in the state where a clock is not supplied except for a part of blocks. If needed, set up *[CGFSYSENA]*, *[CGFSYSENB]*, *[CGFSYSMENB]*, *[CGFCEN]* and *[CGSPCLKEN]* and enable clock supply.

| Block                                     |                    |          |                    | STOP1         |               | STOP2 (Note1) |               |

|-------------------------------------------|--------------------|----------|--------------------|---------------|---------------|---------------|---------------|

|                                           |                    | NORMAL   | IDLE               | ELOSC         | ELOSC         | ELOSC         | ELOSC         |

|                                           |                    |          |                    | On            | Off           | On            | Off           |

| Processor core (Debu                      | ıg included)       | ✓        | -                  | -             | -             | ×             | ×             |

| DMAC                                      |                    | ✓        | $\checkmark$       | -             | -             | ×             | ×             |

| I/O port                                  | Pin state          | ~        | ~                  | ~             | ~             | ✓<br>(Note4)  | ✓<br>(Note4)  |

|                                           | Register           | ✓        | ✓                  | -             | -             | ×             | ×             |

| ADC                                       |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| DAC                                       |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| COMP                                      |                    | ✓        | ✓                  | -             | -             | ×             | ×             |

| UART                                      |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| I2C                                       |                    | ~        | ~                  | -<br>(Note 3) | -<br>(Note 3) | ×<br>(Note 3) | ×<br>(Note 3) |

| EI2C                                      |                    | ~        | ~                  | -<br>(Note 3) | -<br>(Note 3) | ×<br>(Note 3) | ×<br>(Note 3) |

| TSPI                                      |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| A-PMD                                     |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| A-ENC                                     |                    | ~        | ~                  | -             | -             | ×             | ×             |

| T32A                                      |                    | ~        | $\checkmark$       | -             | -             | ×             | ×             |

| LCD                                       |                    | ✓        | ~                  | ✓             | -             | ✓             | -             |

| TRGSEL                                    |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| CRC                                       |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| RTC                                       |                    | ✓        | ~                  | ✓             | -             | ✓             | -             |

| RMC                                       |                    | ~        | $\checkmark$       | ✓             | -             | ×             | ×             |

| SIWDT                                     |                    | ✓        | ✓ (Note 2)         | -             | -             | ×             | ×             |

| LVD                                       |                    | ✓        | ~                  | ✓             | ✓             | ✓             | ✓             |

| OFD                                       |                    | ~        | ~                  | -             | -             | ×             | ×             |

| TRM                                       |                    | ✓        | Unavailable        | -             | -             | ×             | ×             |

| CG                                        |                    | ✓        | ~                  | ✓             | ✓             | ×             | ×             |

| PLL                                       |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| RAMP (RAM parity)                         |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| External high-speed of                    | oscillator (EHOSC) | ✓        | ~                  | -             | -             | ×             | ×             |

| Built-in high-speed oscillator 1 (IHOSC1) |                    | ~        | ~                  | -             | -             | ×             | ×             |

| Built-in high-speed oscillator 2 (IHOSC2) |                    | ✓        | ~                  | -             | -             | ×             | ×             |

| External low-speed or                     | scillator (ELOSC)  | ✓        | ✓                  | ✓             | -             | ✓             | -             |

| RLM                                       |                    | ✓        | ✓                  | ✓             | ✓             | ✓             | ✓             |

| Code flash                                |                    |          |                    |               |               | Data          | Data          |

| Data flash                                |                    | Access   | Access<br>possible | Data          | Data          | hold          | hold          |

| RAM                                       |                    | possible | (Note5)            | hold          | hold          | ×             | ×             |

| Backup RAM                                |                    |          |                    |               |               | Data hold     | Data hold     |

| Table 1.7 | <b>Block Operation</b> | Status in Each | Low-power C | Consumption Mode |

|-----------|------------------------|----------------|-------------|------------------|

|           |                        |                |             |                  |

$\checkmark$ : operation is possible.

-: if it shifts to the object mode, the clock to a peripheral circuit stops automatically.

×: If it shifts to the object mode, the electric supply source to a module intercepts automatically. When returning, initialized by the reset.

Note1: Check that the peripheral function is not running and change to STOP 2 mode. Note2: It's in the protected A mode only. In other case, Stop SIWDT before shifting to the IDLE mode.

Note3: The address match wake up function can only be used.

Note4: A port state when the *[RLMSHTDNOP]* <PTKEEP> is set to "1" is held.

Note5: It becomes a data hold when peripheral functions (DMA etc.) which carry out data access (R/W), except CPU, are not connected on the bus matrix.

#### 1.3.2. Mode State Transition

Figure 1.2 Mode State Transition

- Note1: Warm up is required at returning. A warm up time must be set in the previous mode (NORMAL mode) before entering to STOP1 mode.

- Note2: When the CPU returns from STOP2 mode, the CPU branches to the interrupt service routine triggered by reset. When the CPU returns from STOP1 mode, the CPU branches to the interrupt service routine triggered by interrupt events.

#### 1.3.2.1. IDLE Mode Transition Flow

Set up the following procedure at switching to IDLE mode.

Because IDLE mode is released by an interrupt, set the interrupt before switching to IDLE mode. For the interrupts that can be used to release the IDLE mode, refer to "1.3.3.1. Release Source of Low-power Consumption Mode". Disables unused interrupts and unavailable interrupts for release IDLE mode.

| Switching procedure (from NORMAL mode) |                                                |                                                        |  |

|----------------------------------------|------------------------------------------------|--------------------------------------------------------|--|

| 1                                      | <b>[SIWDxEN]</b> <wdte> = 0</wdte>             | Disable SIWDT.                                         |  |

| 2                                      | <b>[SIWDxCR]</b> <wdcr[7:0]>= 0xB1</wdcr[7:0]> | Disable SIWDT.                                         |  |

| 3                                      | [FCSR0] <rdybsy> is read</rdybsy>              | It waits until Flash will be in a Ready state (= 1).   |  |

| 4                                      | <b>[CGSTBYCR]</b> <stby[1:0]> = 00</stby[1:0]> | Low-power consumption mode selection is set to IDLE.   |  |

| 5                                      | [CGSTBYCR] <stby[1:0]> is read</stby[1:0]>     | Confirm "00" to written to the register at the step 4. |  |

| 6                                      | WFI command execution                          | Switch to IDLE.                                        |  |

Note: When using the protected A mode of SIWDT, step 1 and 2 are not required.

#### 1.3.2.2. STOP1 Mode Transition Flow

Set up the following procedure at switching to STOP1.

Because STOP1 mode is released by an interrupt, set the interrupt before switching to STOP1 mode. For the interrupts that can be used to release the STOP1 mode, refer to "1.3.3.1. Release Source of Low-power Consumption Mode". Disables unused interrupts and unavailable interrupts for release STOP1.

|    | Switching procedure (from NORMAL mode)             |                                                                                                                          |  |  |

|----|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| 1  | <b>[SIWDxEN]</b> <wdte> = 0</wdte>                 | Disable SIWDT.                                                                                                           |  |  |

| 2  | <b>[SIWDxCR]</b> <wdcr[7:0]> = 0xB1</wdcr[7:0]>    | Disable SIWDT.                                                                                                           |  |  |

| 3  | [FCSR0] <rdybsy> is read</rdybsy>                  | Wait until Flash becomes the Ready state (= 1).                                                                          |  |  |

| 4  | [CGWUPHCR] <wuef> is read</wuef>                   | Wait until the high-speed oscillation warming up ends (= 0).                                                             |  |  |

| 5  | <b>[CGWUPHCR]</b> <wuclk> = 0</wuclk>              | Set the warming-up clock selection to internal high-speed oscillator 1 (IHOSC1).                                         |  |  |

| 5  | <b>[CGWUPHCR]</b> <wupt[15:4]> = 0x3C</wupt[15:4]> | Set the high-speed oscillation warming-up timer setting value of 163.4 $\mu$ s (= 0x3C) or more.                         |  |  |

| 6  | [CGSTBYCR] <stby[1:0]> = 01</stby[1:0]>            | Low-power consumption mode selection is set to STOP1.                                                                    |  |  |

| 7  | [CGPLL0SEL] <pll0sel>=0</pll0sel>                  | Select the PLL for fsys to "PLL is unused (fosc)".                                                                       |  |  |

| 8  | [CGPLL0SEL] <pll0st> is read</pll0st>              | Wait until the status of the PLL for fsys becomes "PLL is unused (fosc) (= 0)".                                          |  |  |

| 9  | [CGPLL0SEL] <pll0on> = 0</pll0on>                  | Stop PLL for fsys                                                                                                        |  |  |

| 10 | [CGOSCCR] <ihosc1en> = 1</ihosc1en>                | Enable the internal high-speed oscillator.                                                                               |  |  |

| 11 | [CGWUPHCR] <wuon> = 1</wuon>                       | Start the high-speed oscillation warming-up timer                                                                        |  |  |

| 12 | [CGWUPHCR] <wuef> is read.</wuef>                  | Wait until an warming-up timer status flag becomes ends (= 0).                                                           |  |  |

| 13 | [CGOSCCR] <oscsel> = 0</oscsel>                    | Set the high-speed oscillation selection for fosc to internal high-<br>speed oscillator1 (IHOSC1).                       |  |  |

| 14 | [CGOSCCR] <oscf> is read.</oscf>                   | Wait until the high-speed oscillation selection status for fosc becomes internal high-speed oscillator1 (IHOSC1). (= 0). |  |  |

| 15 | [CGOSCCR] <eoscen[1:0]> = 00</eoscen[1:0]>         | Set the selection of an external oscillator operation to unused.                                                         |  |  |

| 16 | [CGOSCCR] <ihosc2en> = 0</ihosc2en>                | The internal high-speed oscillator 2 (IHOSC2) is stopped.                                                                |  |  |

| 17 | [CGOSCCR] <eoscen[1:0]> is read</eoscen[1:0]>      | The register writing of above 15th row is checked (= 00).                                                                |  |  |