## **3-Phase Multi-Level Inverter using MOSFET**

# Design guide

RD208-DGUIDE-01

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**

### Table of Contents

| 1.                    | Int                   | roduction3                                                   |

|-----------------------|-----------------------|--------------------------------------------------------------|

| 2.                    | Cor                   | nponents Used4                                               |

| 2.1.                  | Ро                    | wer MOSFET TPH9R00CQ54                                       |

| 2.2.                  | Ga                    | te Driver Coupler TLP1525                                    |

| 2.3.                  | LD                    | O Power Regulator TCR3UF Series                              |

| 2.4.                  | Со                    | mparator TC75W57FK7                                          |

| 3.                    | Mu                    | lti-Level Inverter8                                          |

| 3.1.                  | Op                    | peration of 2-Level Inverter8                                |

| 3.2.                  | Ov                    | verview of Multi-Level Inverter10                            |

| 3.3.                  | Op                    | peration of Multi-Level Inverter10                           |

| 4.                    | Cir                   | cuit Design14                                                |

| 4.1.                  | Ise                   | olated Power Supply Circuit15                                |

| 4.1                   | L <b>.1.</b>          | DC 400 V In /DC 15 V Out Isolated DC-DC Converter            |

| 4.1                   | 2.                    | DC 15 V In /DC 15 V-4channel Out Isolated DC-DC Converter 16 |

| 4.2.                  | СР                    | LD Power Supply Circuit (3.3 V, 1.8 V)17                     |

| 4.3.                  | Ga                    | te Driver Power Supply Circuit18                             |

| 4.4.                  | 4. Gate Drive Circuit |                                                              |

| 4.5. Current Detector |                       |                                                              |

| 4.5                   | 5.1.                  | Current Sensor                                               |

| 4.5                   | 5.2.                  | Current Measurement Output Circuit                           |

| 4.5                   | 5.3.                  | Overcurrent Detection Circuit                                |

### 1. Introduction

This Design Guide (hereafter referred to as this guide) describes the design of 3-Phase Multi-Level Inverter (hereafter referred to as this inverter) using MOSFET.

3-phase inverters are used to drive induction motors and synchronous motors used in industrial robots, etc. When output is AC 200 V, and a common 2-level inverter configuration is used, then one 600 V MOSFET is used on each of the upper and lower arms. By using a multi-stack MOSFET configuration per arm, the resolution of the voltage output is increased, and precise voltage output control is achieved, thus realizing a highly efficient inverter. This inverter uses four MOSFETs in each of the upper and lower arms, enabling up to five-level PWM voltage output.

150 V power MOSFET <u>TPH9R00CQ5</u> is used as a switching device. TPH9R00CQ5 features a highspeed built-in diode. It can reduce switching-loss in the inverter operation with inductive loads such as motors. Since four TPH9R00CQ5 are used for each arm, the configuration apparently operates as a MOSFET for withstanding voltage 600 V.

A small, high-speed switching driver coupler <u>TLP152</u> is used for driving MOSFETs.

### 2. Components Used

This section introduces the components that are used in this inverter. Toshiba has an extensive lineup of power semiconductors, driver couplers, and LDOs, including those used this time.

#### 2.1. Power MOSFET TPH9R00CQ5

This inverter uses <u>TPH9R00CQ5</u> for inverter switching.

#### Features

- Fast reverse recovery time: t<sub>rr</sub> = 40 ns (Typ.)

- Small reverse recovery charge: Q<sub>rr</sub> = 34 nC (Typ.)

- Small gate charge: Q<sub>SW</sub> = 11.7 nC (Typ.)

- Low on-resistance:  $R_{DS(ON)} = 7.3 \text{ m}\Omega \text{ (Typ.)} (V_{GS} = 10 \text{ V})$

- Low leakage current:  $I_{DSS} = 10 \ \mu A \ (Max.) \ (V_{DS} = 150 \ V)$

- Easy-to-use enhancement type:  $V_{th} = 3.1$  to 4.5 V ( $V_{DS} = 10$  V,  $I_D = 1.0$  mA)

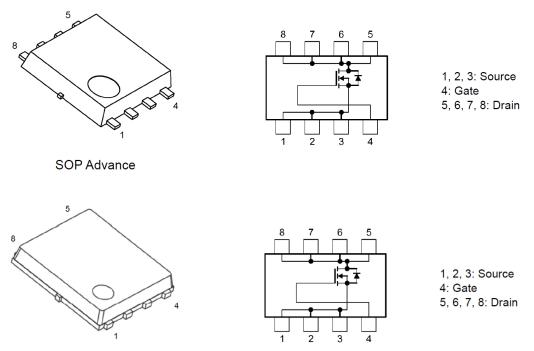

#### **Appearance and Pin Layout**

SOP Advance(N)

The package can be selected according to your preference.

#### 2.2. Gate Driver Coupler TLP152

This inverter uses  $\underline{\text{TLP152}}$  as the gate driver for MOSFET used in the inverter circuit.

#### Features

- Buffer logic output type (totem pole output)

- Output peak current: ± 2.5 A (Max.)

- Operating temperature range: -40 to 100 °C

- Supply current: 3.0 mA (Max.)

- Supply voltage: 10 to 30 V

- Threshold input current: 7.5 mA (Max.)

- Propagation delay time: tpHL = 190 ns (Max.), tpLH = 170 ns (Max.)

- Common-mode transient immunity: ± 20 kV/µs (Min.)

- Isolation voltage: 3750 Vrms (Min.)

- Safety standard compliance

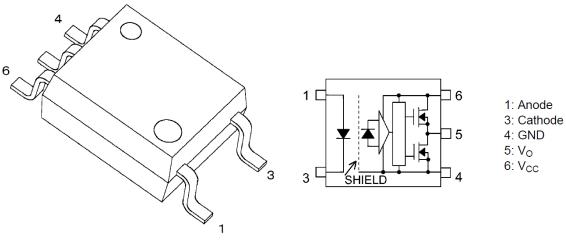

#### **Appearance and Pin Layout**

11-4L1S

#### 2.3. LDO Power Regulator TCR3UF Series

This inverter uses TCR3UF33A and TCR3UF18A as a stabilized power source for CPLD, etc.

#### Features

- Low bias current  $I_B = 0.34 \ \mu A$  (Typ.) @  $I_{OUT} = up$  to 0 mA, power 1.5 V

- High ripple rejection ratio = 70 dB (Typ.) @ 0.8 V output

- Fast load transient response -51/+36 mV @ 0.8 V output,  $I_{OUT} = 1 \text{ mA} \Leftrightarrow 50 \text{ mA}$

- Low dropout voltage  $V_{DO}$  = 206 mV (Typ.) @ 3.3 V out,  $I_{OUT}$  = 300 mA

- Wide output voltage lineup ( $V_{OUT} = 0.8$  to 5.0 V)

- High output voltage accuracy  $\pm$  1.0 % (1.8 V  $\leq$  V<sub>OUT</sub>)

- Auto-discharge (TCR3UFxxA series) / Non-discharge (TCR3UFxxB series)

- Overcurrent protection

- Thermal shutdown

- Inrush current reduction

- Control pin has pull-down connection

- Ceramic capacitors can be used ( $C_{IN} = 1 \ \mu F$ ,  $C_{OUT} = 1 \ \mu F$ ).

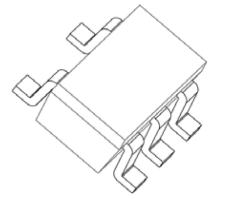

- General purpose package SMV(SOT-25)(SC-74A)

#### Appearance and Pin Layout

#### 2.4. Comparator TC75W57FK

This inverter uses  $\underline{\mathsf{TC75W57FK}}$  as a comparator for overcurrent detection.

#### Features

- Low current consumption:  $I_{DD} = 200 \ \mu A$  (Typ.)

- Single power supply operation

- Wide common mode input voltage range:  $V_{SS}$  to  $V_{DD}$ -0.9 V

- Push-pull output circuit

- Low input bias current

- Small package

#### Appearance and Pin Layout

SSOP8-P-0.50A

### 3. Multi-Level Inverter

#### 3.1. Operation of 2-Level Inverter

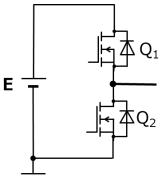

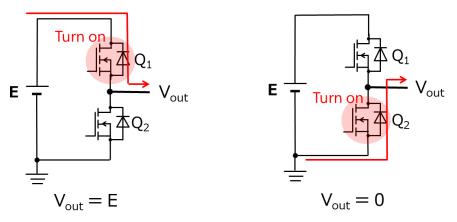

An example of a half-bridge circuit that is a component of a typical 2-level inverter is shown in Fig. 3.1. As shown in the diagram, a MOSFET (Q1) is used for the upper arm and a MOSFET (Q2) is used for the lower arm as a switching element. Bus-voltage E is supplied. As shown in Fig. 3.2, two levels of voltage, E (bus voltage) or 0 (GND voltage), are output from the inverter output Vout by turning Q1, Q2 on/off.

Fig. 3.1 Example of Half-Bridge Circuit

Fig. 3.2 Switching Operation of 2-Level Inverter

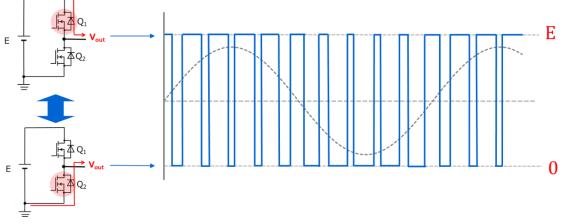

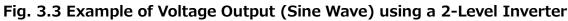

Output voltage is controlled by PWM control of these switching devices. Fig. 3.3 shows an example of voltage output as a sine wave.

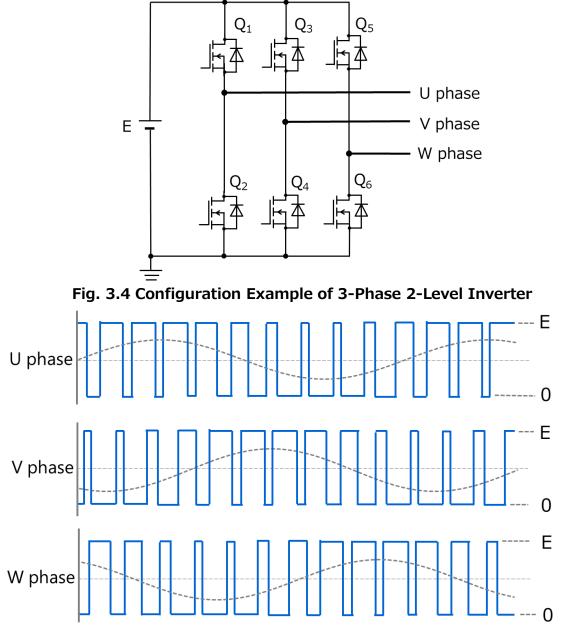

Fig. 3.4 shows the configuration of a 3-phase 2-level inverter. A 3-phase 2-level inverter has a 3-phase full-bridge configuration consisting of three half-bridge circuits. By PWM controlled switching of each phase, 3-phase alternating current with a 120° phase difference between each phase is output. Fig. 3.5 shows an example of sine wave phase voltage output of 3-phase 2-level inverter.

Fig. 3.5 Example of Phase Voltage (Sine Wave) Output of 3-Phase 2-Level Inverter

#### 3.2. Overview of Multi-Level Inverter

In the above mentioned 2-level inverter, one switching element such as a MOSFET is used for each arm, but in the multi-level inverter a configuration with a stack of multiple switching elements is used for each arm. Since the multi-level inverter can increase the resolution of the output voltage by dividing the input voltage, a waveform similar to a sine wave can be output and the efficiency is expected to be better compared to the 2-level inverter. In addition, the output ripple current and harmonics can be reduced without increasing the switching frequency. Furthermore, the appropriate gate control circuit enables the use of low voltage switching elements compared to the 2-level inverter.

Multi-level inverters can be built using various circuit design methods, including NPC (Neutral Point Clamped) method, a T-NPC method, and a flying capacitor method, however this inverter uses NPC method.

#### 3.3. Operation of Multi-Level Inverter

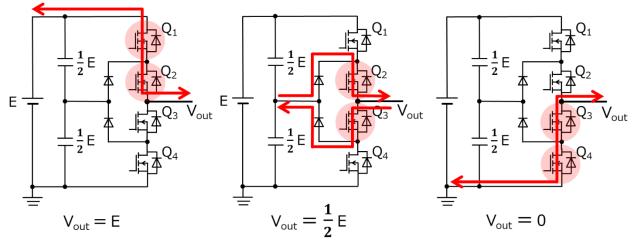

Fig. 3.6 shows the switching operation of the 3-level inverter using two MOSFET for each of the upper and lower arms. The inverter output voltage Vout provides three levels of output: bus voltage E when  $Q_1$  and  $Q_2$  are on,  $\frac{1}{2}E$  when  $Q_2$  and  $Q_3$  are on, and 0 when  $Q_3$  and  $Q_4$  are on.  $Q_1$  and  $Q_3$ , and  $Q_2$  and  $Q_4$  performs complementary operation and therefore are not turned on at the same time. In addition to supplying current to the load from the power supply side during inverter operation, there is a period in which the current returns from the inductive load to the power supply side, therefore, the direction of the current is shown in both directions in Fig. 3.6.

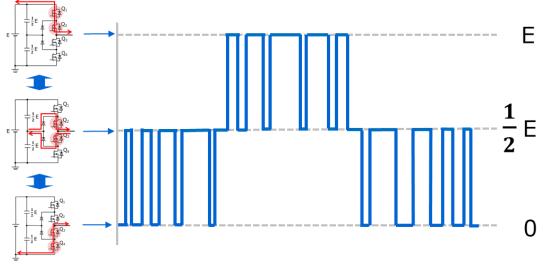

In this way, a 3-level inverter doubles the number of switching elements compared to a 2-level inverter, but the resolution of the output voltage is 1.5 times that of the 2-level inverter, so there is an advantage that the output voltage can be finely controlled. An example of phase voltage output for a 3-level inverter is shown in Fig. 3.7.

Fig. 3.6 3-Level Inverter Switching Operation

Fig. 3.7 Example of Phase Voltage Output of 3-Level Inverter

Here, the amplitude of the output voltage and the voltage applied to each switching element in both 2-level inverter and the 3-level inverter is considered. If both bus voltages are the same E, the output of the 2-level inverter is E and 0, so the amplitude of the output voltage is E, and the voltage applied to each switching element is E. On the other hand, since the output of the 3-level inverter is E,  $\frac{1}{2}$ E, and 0, the amplitude of the output voltage in each switching section is  $\frac{1}{2}$ E, and the voltage applied to each switching element is also  $\frac{1}{2}$ E. Since the voltage applied to each switching element is  $\frac{1}{2}$  compared to a 2-level inverter, therefore, a switching element with half withstand voltage can be used. Generally, when the withstand voltage of a switching element such as a MOSFET is high, the loss in the switching application tends to deteriorate due to an increase in the on-resistance per unit area, etc., but with a multi-level inverter, a device with low withstand voltage can be used, thereby reducing the loss in the inverter.

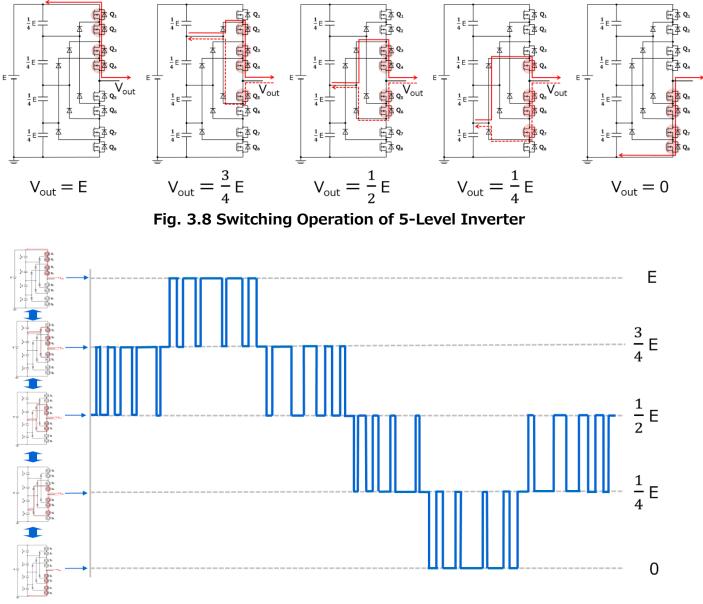

Likewise, Fig. 3.8 shows the switching operation of a 5-level inverter using four MOSFET stack for each of the upper and lower arms. The inverter output voltage Vout has five levels of output: E,  $\frac{3}{4}$ E,  $\frac{1}{2}$ E,  $\frac{1}{4}$ E, and 0 which are produced by switching the MOSFETs. An example of phase voltage output for a 5-level inverter is shown in Fig. 3.9. The 5-level inverter can control the output voltage more precisely than the 3-level inverter. Compared to a 2-level inverter, a 5-level inverter applies  $\frac{1}{4}$ voltage to each switching element. Therefore, a switching element with  $\frac{1}{4}$ withstand voltage to the bus voltage can be used.

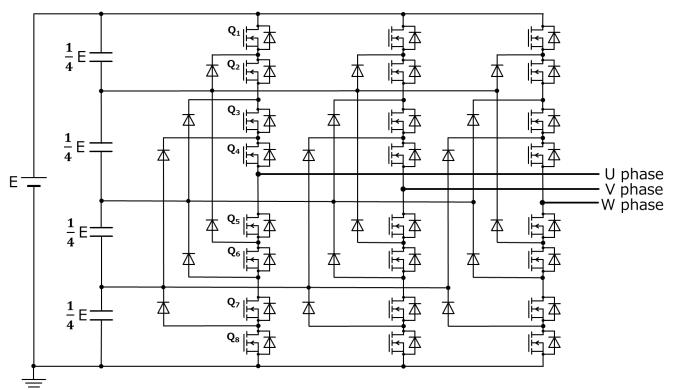

As shown in Fig. 3.10, this inverter uses a 5-level inverter to realize a 3-phase inverter.

#### RD208-DGUIDE-01

Fig. 3.9 Example of Phase Voltage Output of 5-Level Inverter

Fig. 3.10 Example of 3-Phase, 5-Level Inverter Configuration

### 4. Circuit Design

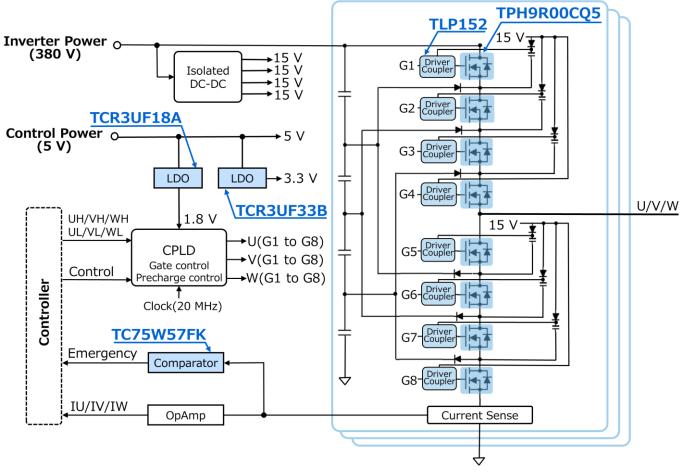

This section describes the gist of the circuit design. Refer to RD208-SCHEMATIC for the schematic and to RD208-BOM for the bill of material. Fig. 4.1 shows the block diagram of this inverter.

Fig. 4.1 Block Diagram of 3-Phase Multi-Level Inverter using MOSFET

#### 4.1. Isolated Power Supply Circuit

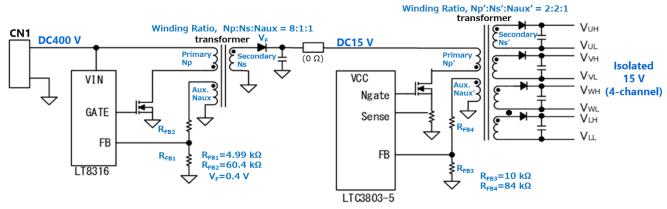

This inverter operates using DC 400 V (Max.) supplied from the inverter power supply connector (CN1) and DC 5 V supplied from the control power supply connector (CN2). The isolated power supply circuit takes DC 400 V input and generates power for the gate-drive circuit. Fig. 4.2 shows the configuration of the isolated power supply circuit.

Fig. 4.2 Isolated Power Supply Circuit

#### 4.1.1. DC 400 V In /DC 15 V Out Isolated DC-DC Converter

In Fig. 4.2, the voltage output V<sub>out1</sub> of the first stage of the isolated power supply (DC 400 V input/DC 15 V output) is determined by the voltage dividing resistors ( $R_{FB1}$ ,  $R_{FB2}$ ) connected to the FB pin of the power supply controller IC (LT8316), the winding ratio  $N_{TS}$  of the Aux. and Secondary windings of the transformer ( $N_{TS} = 1$  for this circuit because the winding ratio is 1:1), and the voltage drop V<sub>F</sub> of the output diode (V<sub>F</sub> = 0.4 V for this circuit).

$$V_{out1} = \left(1 + \frac{R_{FB2}}{R_{FB1}}\right) \times \frac{Internal \ reference \ voltage \ 1.22 \ (V)}{N_{TS}} - V_F$$

And

$R_{FB1} = 4.99 \ k\Omega, \ R_{FB2} = 60.4 \ k\Omega,$

Therefore

$$\begin{array}{rcl} V_{out1} & = & \left(1 + \frac{60.4 \times 10^3}{4.99 \times 10^3}\right) \times \frac{1.22}{1} - 0.4 \\ & \cong & 15.6 \ (V) \end{array}$$

#### 4.1.2. DC 15 V In /DC 15 V-4channel Out Isolated DC-DC Converter

In Fig. 4.2, the output voltage  $V_{out2}$  of the subsequent stage (DC 15 V input /DC 15 V-4channel output) is determined by the voltage dividing resistors ( $R_{FB3}$ ,  $R_{FB4}$ ) connected to FB pin of the power supply controller IC (LTC3803-5) and the winding ratio  $N_{TS'}$  of the Aux. and Secondary windings of the transformer ( $N_{TS'}$  = 0.5 for this circuit because the winding ratio is 1:2).

$$V_{out2} = \left(1 + \frac{R_{FB4}}{R_{FB3}}\right) \times \frac{Internal \ reference \ voltage \ 0.8 \ (V)}{N_{TS}}$$

And

$R_{FB3} = 10 \ k\Omega, \ R_{FB2} = 84 \ k\Omega,$

Therefore

$$V_{out2} = \left(1 + \frac{84 \times 10^3}{10 \times 10^3}\right) \times \frac{0.8}{0.5}$$

\$\approx 15.0 (V)\$

#### 4.2. CPLD Power Supply Circuit (3.3 V, 1.8 V)

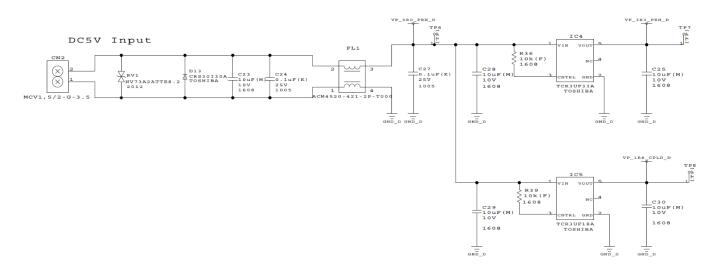

It generates the power supply for CPLD that performs gate-control by using DC 5 V supplied from the control power supply connector. CPLD used in this inverter has a I/O voltage of 3.3 V and core voltage of 1.8 V. LDO TCR3UF33A (IC4) is used to generate 3.3 V and LDO TCR3UF18A (IC5) is used to generate 1.8 V. Fig. 4.3 shows the power supply for CPLD.

Fig. 4.3 Power supply for CPLD

#### 4.3. Gate Driver Power Supply Circuit

Since the source voltage level of each MOSFET of the inverter arm changes during switching operation, a gate driver power supply is required for each MOSFET in the stack. And, since the base voltage level of upper arms of each phase and all lower arms (same voltage for all phases) is different, thus four separate isolated power supplies are required. Thus, four different channels of 15 V isolated power supply are used for U-phase upper arm, the V-phase upper arm, the W-phase upper arm, and the lower arms of all phases (common for the U/V/W phase). Furthermore, the power supplies of gate drivers for MOSFETs other than the lowest MOSFET in the arm are implemented by a bootstrap circuit consisting of a diode and a capacitor.

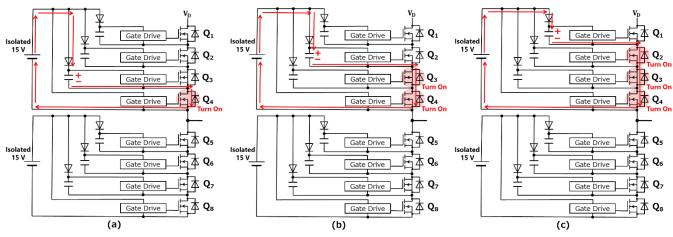

To charge (pre-charge) the capacitors for gate driver of each MOSFET in the stack, an external controller or a CPLD installed in the inverter must be used to control the gate signal. This is necessary before starting the inverter operation. Fig. 4.4 shows the charging sequence of the power supply capacitors of the gate drivers using the upper arm as an example. The gate driver of Q<sub>4</sub> can always work since 15 V isolated power supply is always supplied. As shown in Fig. 4.4 (a), Q<sub>3</sub> gate driver power supply capacitor is charged by turning on Q<sub>4</sub> for a period of time to enable Q<sub>3</sub> gate driver. Then, as shown in (b), Q<sub>2</sub> gate driver power supply capacitor is charged by turning on Q<sub>4</sub> and Q<sub>3</sub> for a period of time to enable Q<sub>2</sub> gate driver. Finally, as shown in (c), Q<sub>1</sub> gate driver power supply capacitor is charged by turning on Q<sub>4</sub>, Q<sub>3</sub> and Q<sub>2</sub> for a period of time to enable Q<sub>1</sub> gate driver. Other arms also require a similar charging sequence before starting the inverter operation.

Fig. 4.4 Charging Sequence of Gate Driver Power Supply Capacitors

#### 4.4. Gate Drive Circuit

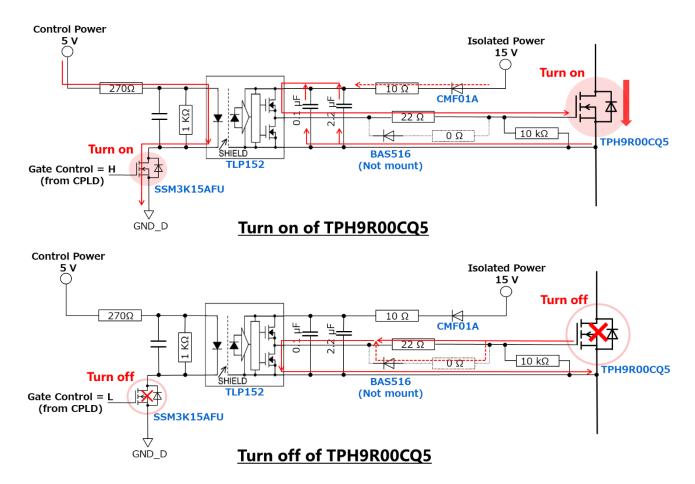

The driver coupler TLP152 is used as a gate driver of MOSFET. When the gate control signal from CPLD goes to H level, MOSFET (SSM3K15AFU) is turned on and the current flows through the primary-side diode of TLP152. This turns on the high-side circuit of the secondary side of TLP152, which turns on MOSFET (TPH9R00CQ5). On the other hand, when the gate-control signal from CPLD is turned off, the diode on the primary side of TLP152 is turned off. Therefore, MOSFET (TPH9R00CQ5) connected to the secondary side is also turned off. Fig. 4.5 shows the gate-drive operation of MOSFET (TPH9R00CQ5) for inverter switching in this case. By default, the external gate resistance when turning on is 22  $\Omega$  and the external gate resistance when turning off is 22  $\Omega$ . However, since the optimum value differs depending on the switching frequency, bus voltage, etc., therefore the value of gate resistance must be optimized according to the actual design specifications.

Fig. 4.5 Gate Drive Operation of MOSFET for Inverter Switching

#### 4.5. Current Detector

#### 4.5.1. Current Sensor

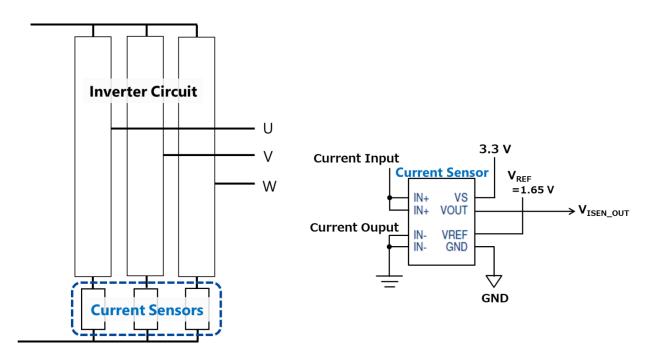

Fig. 4.6 shows the configuration of the current sensors. A current sensor is connected to each phase of the inverter circuit, and the current of each phase is converted to voltage output and then is input to the current measurement output circuit and overcurrent detection circuit. The relationship between the input current and the output voltage of current sensor is as follows.

$V_{ISEN_OUT} = S \times I_{phase} + V_{REF} \cdots (1)$

Here

$V_{ISEN_OUT}$  : Current sensor output voltage [V]

```

S : Sensitivity = 0.05 [V/A]

```

$I_{phase}$ : Input current of each phase [A]

$V_{REF}$ : Reference voltage = 1.65 [V]

From the above, output voltage  $V_{ISEN_{OUT}}$  of current sensor, when the current is flowing towards ground the output voltage is more than the reference voltage of 1.65 V, and when the current is coming from the ground then the output voltage is less than the reference voltage of 1.65 V.

Fig. 4.6 Current Sensor

#### 4.5.2. Current Measurement Output Circuit

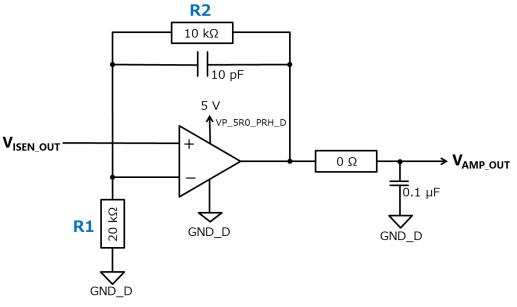

Fig. 4.7 shows the current measurement output circuit.

Fig. 4.7 Current Measurement Output Circuit

The output voltage  $V_{ISEN_OUT}$  of the current sensor in each phase is amplified by a non-inverting amplifier using an operational amplifier and is output to the controller connector. The output voltage  $V_{AMP_OUT}$  to the controller connector is expressed by the following equation. When the resistance R1 = 20 k $\Omega$  and R2 = 10 k $\Omega$  as shown in Fig. 4.7, output  $V_{AMP_OUT}$  is as shown below.

$$V_{AMP_OUT} = \frac{R1 + R2}{R1} \times V_{ISEN_OUT}$$

=  $\frac{20 \times 10^3 + 10 \times 10^3}{20 \times 10^3} \times V_{ISEN_OUT}$

=  $1.5 \times V_{ISEN_OUT}$

=  $0.075 \times I_{phase} + 2.475$

### \_\_\_\_\_

**FOSHIBA**

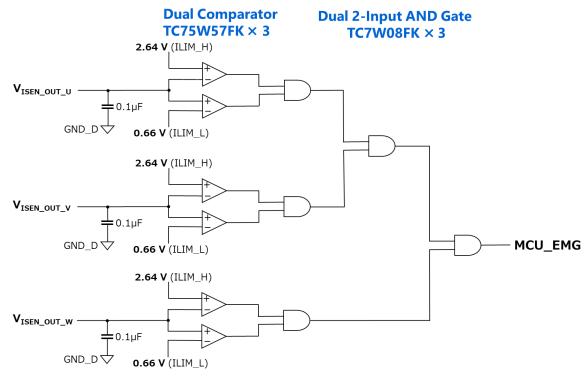

**4.5.3.** Overcurrent Detection Circuit

Fig. 4.8 shows the overcurrent detection circuit.

$V_{ISEN_OUT}$  input from each phase is compared by the comparator. The comparator inputs are connected with ILIM\_H (2.64 V) or ILIM\_L (0.66 V) as reference voltages. According to the above equation (1) these voltages are equivalent to  $I_{phase} = 20$  A when  $V_{ISEN_OUT} = 2.64$  V and  $I_{phase} = -20$  A when  $V_{ISEN_OUT} = 0.66$  V. When ILIM\_H is the + input of the comparator, and  $V_{ISEN_OUT}$  is the -input of the comparator, and if  $V_{ISEN_OUT} > 2.64$  V (that is,  $I_{phase} > 20$  A), then the comparator output is L level. Also, if  $V_{ISEN_OUT}$  is the + input of the comparator, and ILIM\_L is the -input of the comparator, and if  $V_{ISEN_OUT} < 0.66$  V (that is,  $I_{phase} < -20$  A), then the comparator output is L level. This comparison is done with each phase sensor output  $V_{ISEN_OUT_U}$ ,  $V_{ISEN_OUT_V}$ ,  $V_{ISEN_OUT_W}$ . The overcurrent detection signal MCU\_EMG has a negative logic output that becomes L level output when overcurrent is detected. When any of the six comparators' outputs are L level, then the output of the final AND gate (= MCU\_EMG signal) becomes L, indicating that overcurrent error has occurred.

#### Terms of Use

This terms of use is made between Toshiba Electronic Devices and Storage Corporation ("We") and customers who use documents and data that are consulted to design electronics applications on which our semiconductor devices are mounted ("this Reference Design"). Customers shall comply with this terms of use. Please note that it is assumed that customers agree to any and all this terms of use if customers download this Reference Design. We may, at its sole and exclusive discretion, change, alter, modify, add, and/or remove any part of this terms of use at any time without any prior notice. We may terminate this terms of use at any time and for any reason. Upon termination of this terms of use, customers shall destroy this Reference Design. In the event of any breach thereof by customers, customers shall destroy this Reference Design, and furnish us a written confirmation to prove such destruction.

#### 1. Restrictions on usage

1. This Reference Design is provided solely as reference data for designing electronics applications. Customers shall not use this Reference Design for any other purpose, including without limitation, verification of reliability.

2. This Reference Design is for customer's own use and not for sale, lease or other transfer.

3. Customers shall not use this Reference Design for evaluation in high or low temperature, high humidity, or high electromagnetic environments.

4. This Reference Design shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

#### 2. Limitations

1. We reserve the right to make changes to this Reference Design without notice.

2. This Reference Design should be treated as a reference only. We are not responsible for any incorrect or incomplete data and information.

3. Semiconductor devices can malfunction or fail. When designing electronics applications by referring to this Reference Design, customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of semiconductor devices could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Customers must also refer to and comply with the latest versions of all relevant our information, including without limitation, specifications, data sheets and application notes for semiconductor devices, as well as the precautions and conditions set forth in the "Semiconductor Reliability Handbook".

4. When designing electronics applications by referring to this Reference Design, customers must evaluate the whole system adequately. Customers are solely responsible for all aspects of their own product design or applications. WE ASSUME NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

5. No responsibility is assumed by us for any infringement of patents or any other intellectual property rights of third parties that may result from the use of this Reference Design. No license to any intellectual property right is granted by this terms of use, whether express or implied, by estoppel or otherwise.

6. THIS REFERENCE DESIGN IS PROVIDED "AS IS". WE (a) ASSUME NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (b) DISCLAIM ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO THIS REFERENCE DESIGN, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

#### 3. Export Control

Customers shall not use or otherwise make available this Reference Design for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). This Reference Design may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of this Reference Design are strictly prohibited except in compliance with all applicable export laws and regulations.

#### 4. Governing Laws

This terms of use shall be governed and construed by laws of Japan.