東芝和日本半導體株式會社共同研發了用於車載應用的具有嵌入式非易失性記憶體的高可靠度多功能模擬平臺

2022年5月31日

東芝電子元件及儲存裝置株式會社

日本半導體株式會社

日本川崎--東芝電子元件及存儲裝置株式會社(“東芝”)和日本半導體株式會社(Japan Semiconductor Corporation )共同研發出用於車載應用的具有嵌入式非易失性記憶體(eNVM)的高可靠多功能模擬平臺。 新一代0.13微米類比平臺適用於模擬積體電路(IC),可根據額定電壓、性能、可靠性和成本,為單晶元上集成汽車類比電路和eNVM提供工藝和器件的優化組合。

包括電機驅動IC的類比IC廣泛應用於車載應用領域。 隨著電動汽車的發展以及配置高級駕駛輔助系統(ADAS)的車輛增加,預計類比IC市場將持續增長。 因此需要多功能專用汽車級平臺滿足相關車載應用的需求。 由於eNVM和微控制器單元(MCU)尚未在單個晶片上實現,因此IC總面積較大。

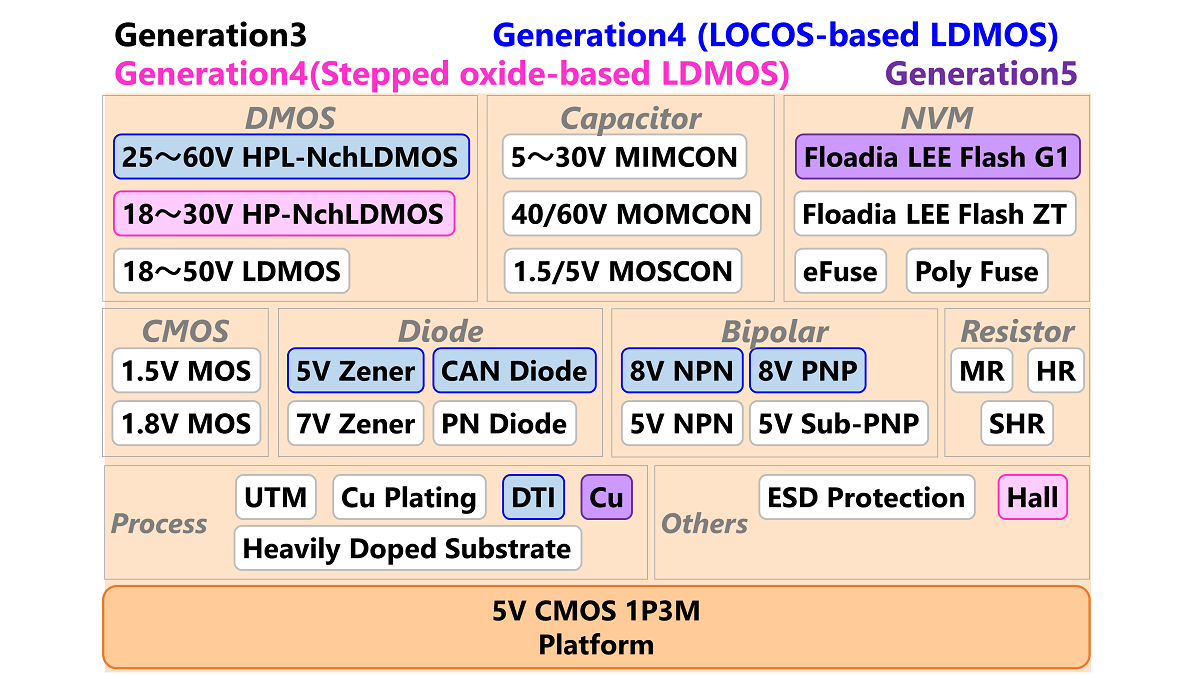

東芝和日本半導體提供三種LDMOS*1結構和包括eNVM在內的非常廣泛的器件產品線,可選擇用來滿足不同的要求。 目前,雙方已開發出高度可靠的、符合汽車可靠性國際標準AEC-Q100/Grade-0的類比IC平臺。

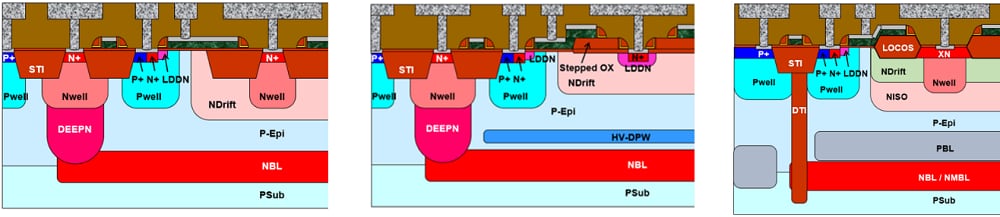

LDMOS關鍵參數導通電阻(RonA)與漏極-源極擊穿電壓(BVDSS )之間需要進行權衡。 在一定的BVDSS之下,RonA越低性能越好。 東芝和日本半導體證實,位於漏極和源極之間採用台階氧化層或LOCOS*2結構的兩種LDMOS最大Ron A比基於STI*4的LDMOS低(好)44%*3 。 他們還確定了相應機制用來評估基於LOCOS的LDMOS器件可靠性、故障率和ESD耐受性優勢。

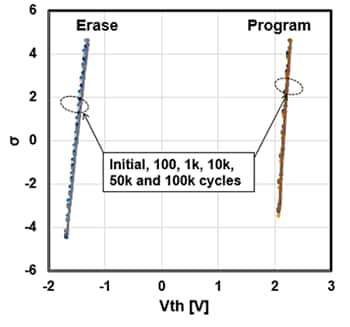

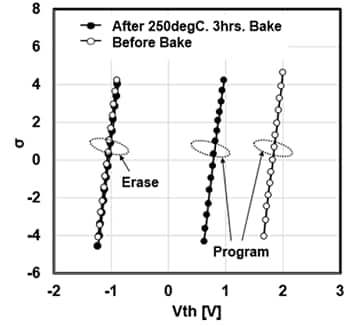

嵌入平臺IP公司Floadia的 eNVM(Floadia LEE Flash G1)只需加三個額外掩模,即可滿足車載模擬功率器件高可靠性要求,而不影響基礎平臺和器件。 同時,還可以通過優化佈局防止類比電路開關LDMOS產生的雜訊的影響,從而避免eNVM故障。

東芝和日本半導體計劃2022年12月開始使用新開發的平臺製作車載半導體試樣。 5月22日至25日,加拿大溫哥華舉行的2022年IEEE國際功率半導體器件和積體電路會議( ISPSD)報告並在線發佈這一成果的詳細資訊。

*1 LDMOS:橫向雙擴散MOS(金屬氧化物半導體)。

*2 LOCOS:局部氧化矽隔離。 氮化矽薄膜用作硬掩模,在矽襯底上選擇性形成氧化矽膜用於隔離元件。

*3 東芝和日本半導體證實,東芝測試結果顯示,位於漏極和源極之間採用台階氧化層或LOCOS結構的兩種LDMOS最大RonA 比基於STI的LDMOS低(好)44%。

*4 STI:淺溝槽隔離。 將絕緣膜嵌入淺溝槽以隔離元件。

開發平臺的元件產品線

三種LDMOS的結構

(左起STI結構、階梯氧化層結構、LOCOS結構)

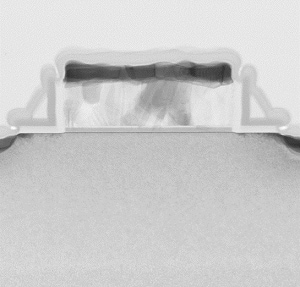

Floadia公司eNVM TEM圖像以及耐久性測試和數據保持測試評估結果(東芝測試結果)

*公司名稱、產品名稱和服務名稱可能是其各自公司的商標。

*本新聞稿中的產品價格和規格、服務內容和聯繫方式等資訊,在公告之日仍為最新資訊,如有更改,恕不另行通知。