Toshiba and Japan Semiconductor Develop Technology to Improve Reliability of Pch-LDMOS for Analog ICs

September 23, 2020

Toshiba Electronic Devices & Storage Corporation

Japan Semiconductor Corporation

東京—東芝電子元件及存儲裝置株式會社(“東芝”)及其製造生產子公司日本半導體株式會社(Japan Semiconductor Corporation)研發了一種旨在提高模擬IC用P溝道橫向雙擴散MOS(P溝道 LDMOS)技術可靠性的技術。這兩家公司闡明了漏極雪崩熱載流子(DAHC)應力測試(LDMOS的可靠性測試)中擊穿電壓下降的原因,並確定了抑制此電壓下降的器件結構。

詳情可參見由IEEE主辦並線上舉行的2020年功率半導體器件和IC國際研討會(ISPSD 2020)報告。

車輛的電氣化和工業設備的自動化正不斷刺激市場對於適用於低溫和高溫環境中長期保持高度可靠性的模擬IC的需求。因此,具有低導通電阻,適合於廣泛應用的LDMOS引起了極大的關注。

在漏極雪崩熱載流子(DAHC)應力測試中,我們在LDMOS柵極上長時間施加中壓以評估LDMOS的可靠性。該測試測量了擊穿電壓的下降,因為擊穿電壓下降是已知的類比IC損壞和可靠性降低的原因。

到目前為止,導致擊穿電壓下降的機制原理尚未十分明確,但普遍認為是由於淺溝隔離(STI)[1] 角落的陷阱電荷所引起,那裡碰撞電離率最高。但是近來兩家公司通過對電子流和器件結構進行調查,發現了不同的原因,陷阱電荷位於STI底部,而不是淺溝隔離角落。

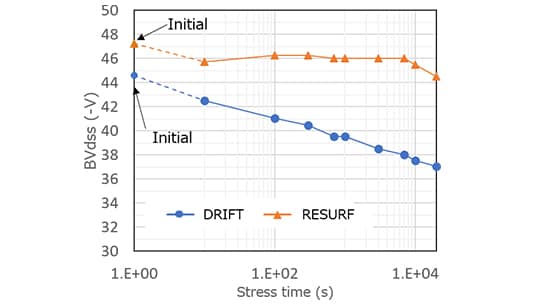

兩家公司發現,RESURF結構[2]比更常用的DRIFT(漂移)結構[3]對於擊穿電壓的下降具有更強的耐受性,因為漂移區下方的一個附加結平衡了整個區域的總電場。RESURF結構的下降抑制可達到漂移結構的三分之二。 [4]

Cross sections of DRIFT and RESURF Pch-LDMOS structures

Improved reliability demonstrated by the DAHC stress test

Note

[1] STI: Shallow Trench Isolation. This divides elements or electrodes by embedding insulator film into shallow trenches.

[2] Comparison of breakdown voltage degradation in DAHC stress test after 5.5 hours. Breakdown voltage in the DRIFT structure falls 7.6V, but in the RESURF structure, it falls only 2.8V.

[3] DRIFT structure: an LDMOS structure in which the P-channel drift region is surrounded by the same P-channel region.

[4] RESURF structure: an LDMOS structure in which the P-channel drift region is surrounded by the N-channel region.

Customer Inquiries

System Devices Sales & Marketing Dept.

Sales Promotion Group

Tel: +81-3-3457-3332

* Information in this document, including product prices and specifications, content of services and contact information, is current on the date of the announcement but is subject to change without prior notice.

* Company names, product names and service names may be trademarks of their respective companies.