アナログIC向けPチャンネルLDMOSの信頼性を改善する技術を開発

2020年9月23日

東芝デバイス&ストレージ株式会社

株式会社ジャパンセミコンダクター

東芝デバイス&ストレージ株式会社(以下、東芝デバイス&ストレージ)と株式会社ジャパンセミコンダクター(以下、ジャパンセミコンダクター)は、アナログIC向けPチャンネルLDMOS注1の信頼性を改善する技術を開発しました。本技術により、「DAHCストレス試験注2」と呼ばれる信頼性試験におけるLDMOSの耐圧低下のメカニズムを解明し、耐圧低下を抑制する構造を特定しました。注3

自動車の電動化や産業機器の自動化などを背景に、モーターコントロールなどに用いられるアナログICの需要が高まっています。アナログICに搭載され、低オン抵抗を特長とする素子であるLDMOSは、今後もさまざまな用途で採用されることが期待されています。一方、車載や産業用途の半導体は長期間の使用が前提となるため、製品の信頼性を長時間保持することが重要です。LDMOSの信頼性試験には、「DAHCストレス試験」と呼ばれる、オンとオフの中間の電圧を長時間印加する試験があり、同試験においてLDMOSの耐圧が低下するという信頼性上の問題がありました。

これまで、「DAHCストレス試験」における耐圧低下のメカニズムは解明されてきませんでしたが、一般的には、LDMOS内のSTI注4領域の角に強い電界がかかると、そこに電子が埋め込まれて電界経路が変わることが原因と考えられてきました。

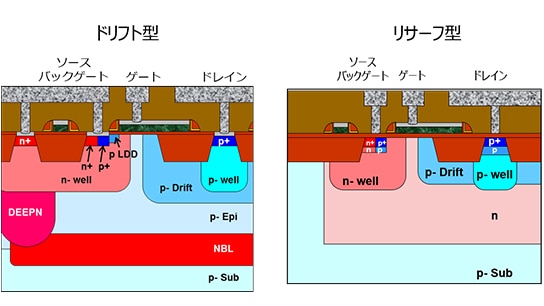

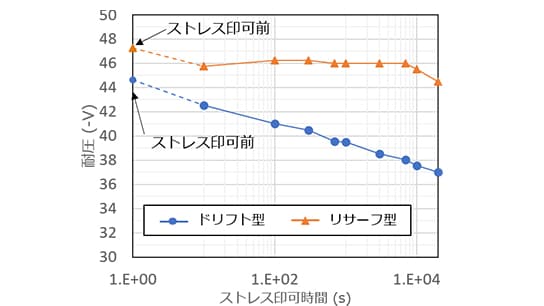

しかし、東芝デバイス&ストレージとジャパンセミコンダクターが電子の流れやデバイス構造を解析した結果、耐圧低下はSTI領域の角ではなく、STI領域の底面に電子が埋め込まれることで、LDMOS内の電界のバランスが崩れることが原因であることを見出しました。耐圧低下のメカニズムを解明した結果、現在主流の「ドリフト型注5」に比べ、全体の電界のバランスが崩れにくい構造である「リサーフ型注6」は、耐圧低下を3分の1に抑制できることを明らかにしました。注3

東芝デバイス&ストレージとジャパンセミコンダクターは本技術の詳細を、9月13日から18日までオンラインで開催された半導体国際学会「IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD) 2020」において発表しました。今後も、LDMOSの信頼性改善に向けた技術開発を促進していきます。

注1 LDMOS:Laterally Double Diffused MOSの略。耐圧向上を目的とてして、ドレイン近傍から横方向に不純物拡散領域(ドレイン領域)を持たせたMOSFETのこと。

注2 DAHCストレス試験:DAHCはDrain Avalanche Hot-Carrierの略。オンとオフの中間の電圧を長時間印加する試験のこと。

注3 「DAHCストレス試験」において、5.5時間ストレスを印加した場合の耐圧を比較。ドリフト構造は7.6V耐圧低下した(低下率17.0%)のに対し、リサーフ構造は2.8V(低下率5.8%)だった。2020年9月時点、当社調べ。

注4 STI:Shallow Trench Isolationの略。浅い溝に絶縁膜を埋め込み、素子間・電極間を分離する領域のこと。

注5 ドリフト型:ドリフト領域(P型)が同種の型(P型)の不純物領域で囲われているLDMOS構造のこと。

注6 リサーフ型:ドリフト領域(P型)が異種の型(N型)の不純物領域で囲われているLDMOS構造のこと。

リサーフ構造LDMOSの断面図

「DAHCストレス試験」における耐圧変動の比較

お客様からの製品に関するお問い合わせ先:

システムデバイス営業推進部

販売促進担当

Tel: 03-3457-3332

*本資料に掲載されている情報(製品の価格/仕様、サービスの内容及びお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。

*社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。