東芝開發帶嵌入式肖特基勢壘二極體的低導通電阻高可靠性SiC MOSFET

2022年12月09日

東芝電子元件及存儲裝置株式會社

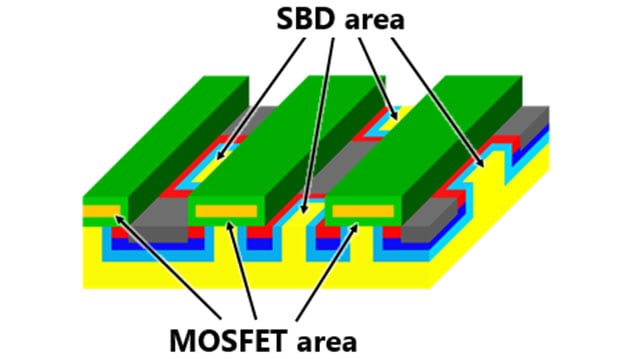

日本川崎-東芝電子元件及存儲裝置株式會社(“東芝”)已經開發了一種碳化矽(SiC)金屬氧化物半導體場效應電晶體(MOSFET)。該電晶體將嵌入式肖特基勢壘二極體(SBD)排列成方格狀(方格狀嵌入式SBD),以實現低導通電阻和高可靠性。東芝已經證實,與目前的SiC MOSFET相比,這種設計能夠在不影響可靠性的前提下,將導通電阻[1] (RonA)降低約20%。[2]

功率元件是管理電能和減少各種電子設備功率損耗以及實現碳中和社會的基本組件。碳化矽能夠提供比矽更高的電壓和更低的損耗,是公認的新一代元件材料。儘管碳化矽現階段的應用主要局限於列車逆變器,但在車輛電氣化和工業設備小型化等領域,已經開始出現更廣泛的應用。然而,一個亟待解決的問題是:在SiC MOSFET反向操作期間,體二極體中的雙極傳導會降低電阻,進而造成不良影響。

東芝電子元件及儲存裝置株式會社開發了一種將SBD嵌入MOSFET的元件結構來抑制體二極體,但其發現,用嵌入式SBD取代MOSFET溝道會降低溝道密度並增加導通電阻。這一取捨問題現在已經透過新的嵌入式SBD結構得以解決,東芝證實,該結構能夠顯著提高性能特性。

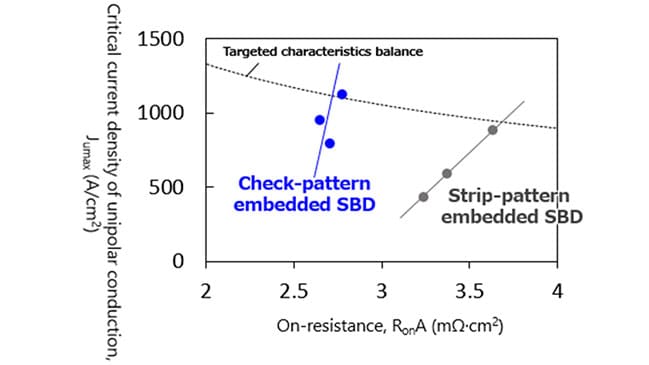

透過部署方格狀SBD分布,東芝改善了SBD嵌入式SiC MOSFET傳導損耗,並實現了良好的二極體導電性。對具有最佳化設計的1.2kV級SBD嵌入式MOSFET的側電流特性的評估證實,使用方格設計將嵌入式SBD固定在體二極體附近能夠有效限制寄生二極體的雙極傳導,而反向傳導的單極電流限制是由相同SBD面積消耗的電流條狀SBD圖案設計實現的單極電流限制的兩倍。在2.7mΩ・cm2條件下,導通電阻降低約20%。

如果要在馬達驅動應用的逆變器中使用SiC MOSFET,這種經證實的取捨改進將至關重要。東芝正在繼續進行評估,以提高動態特性和可靠性,並開發有助於碳中和且具有吸引力的高性能功率半導體。

12月3日至7日在美國舊金山舉行的第68屆IEEE國際電子元件年會(IEEE International Electron Devices Meeting)是一次國際功率半導體會議,會上報導了這項成就的詳細情況。

注:

[1] 導通電阻是MOSFET在工作(導通)期間漏極和源極之間的電阻值。

[2] 截至2022年11月,東芝研究。

新開發的檢查圖案嵌入式SBD-SiC MOSFET的示意圖

1,2kV級SiC MOSFET的特性對比

* 公司名稱、產品名稱和服務名稱可能是其各自公司的商標。

* 本新聞稿中的產品價格和規格、服務內容和聯絡方式等資訊,在發布之日為最新資訊。之後如有變更,恕不另行通知。