低雑音指数を実現したスマートフォン向け高周波低雑音アンプ用SOIプロセスの開発について

2018年 1月26日

東芝デバイス&ストレージ株式会社

当社は、スマートフォンなどのモバイル機器向けに、低雑音アンプ(LNA[注1])に適した高周波半導体用プロセス「TarfSOI™(Toshiba advanced RF SOI)」[注2]の次世代プロセス「TaRF10」を開発しました。

近年、モバイルデータ通信の高速化に伴い、モバイル端末のフロントエンド部には高周波スイッチやフィルタが多数使用され、アンテナ-受信回路間の信号ロスが増加して受信感度が劣化する傾向がありました。このため、信号ロスを補償して受信信号品質を改善することができる低い雑音指数(NF[注3])のLNAへの要望が高まっています。

当社は、今回開発した新プロセス「TaRF10」を用いてNF特性に優れたLNAを試作し、周波数1.8GHzにおいてNF 0.72dBと電力増幅率(Gain[注4])16.9dBを実現しました。

一方、モバイル端末の受信回路には高周波スイッチやLNAが多数使用されることから、実装面積の低減のため回路の小型化が求められています。従来、LNAにはSiGe:C(シリコンゲルマニウム:カーボン)バイポーラトランジスタが用いられていましたが、半導体製造プロセスが異なる高周波スイッチを同一チップ上に集積することが困難でした。

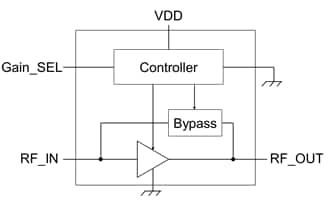

今回開発したTaRF10は、高周波特性に優れた当社高周波スイッチIC用プロセス「TaRF8」や、さらに挿入損失特性や歪特性を低減した「TaRF9」プロセスとの親和性が高く、LNAと高周波スイッチ、制御回路をワンチップで作製することが可能となります。今後、高周波スイッチを集積したLNA製品を鋭意市場投入していく計画です。

当社は、SOI-CMOS技術を用いた高周波半導体用ICを、当社グループの生産拠点(株式会社ジャパンセミコンダクター)を活用し、半導体プロセス開発と製品開発を一貫して行うことにより、最新プロセスを適用したスイッチ製品の早期市場投入を行ってきました。当社は今後も5Gに向かう市場の要求に対応すべく、TarfSOI™プロセスの特性改善を継続し、最先端技術を用いた高周波IC製品を開発していきます。

表1.LNAの主な仕様

| モード | TaRF10プロセス適用LNA | 単位 | |

|---|---|---|---|

| チップサイズ | - | 0.70×0.43 | mm |

| 周波数 | - | 1.8 | GHz |

| 動作電圧 | - | 1.8 | V |

| 消費電流 | ゲインモード | 7.4 | mA |

| バイパスモード | 50 | μA | |

| 制御電圧 | ゲインモード | 1.8 | V |

| バイパスモード | 0 | V | |

| 電力増幅率 | ゲインモード | 16.9 | dB |

| バイパスモード | -1.6 | dB | |

| 雑音指数 | ゲインモード | 0.72 | dB |

| 入力側反射損失 | ゲインモード | 8.4 | dB |

| 出力側反射損失 | ゲインモード | 12.1 | dB |

| 逆方向アイソレーション | ゲインモード | 26.5 | dB |

| 1 dB 利得圧縮時入力電力 | ゲインモード | -8.9 | dBm |

| 3次インターセプトポイント入力電力 | ゲインモード | 4.3 | dBm |

[注1]Low Noise Amplifier

[注2]TarfSOI™(Toshiba advanced RF SOI):TarfSOI™は、当社が高周波半導体用に独自に開発したSOI-CMOS(Silicon On Insulator-Complementary Metal Oxide Semiconductor)フロントエンドプロセス。

[注3]雑音指数(Noise Figure):増幅回路における入力端および出力端の信号対ノイズ比。小さいほど雑音が小さく特性が良い。

[注4]電力増幅率(Gain):増幅回路における入力信号と出力信号の電力の比。

*記載されている社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

お客様からの製品に関するお問い合わせ先:

小信号デバイス営業推進部

Tel : 03-3457-3411

*本資料に掲載されている情報(製品の価格/仕様、サービスの内容及びお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。