0.13μm世代のアナログパワーIC向けにNチャネル-LDMOSの信頼性を向上させる技術を開発

2018年 5月 17日

東芝デバイス&ストレージ株式会社

株式会社ジャパンセミコンダクター

東芝デバイス&ストレージ株式会社(以下、東芝デバイス&ストレージ)と株式会社ジャパンセミコンダクター(以下、ジャパンセミコンダクター)は、0.13μm世代のアナログパワーIC向けに、Nチャネル-LDMOS注1の信頼性を向上させる技術を開発しました。本技術は、ホットキャリア注入注2による経時劣化を抑制することで、従来技術と比較してLDMOSの寿命注3が5倍以上に改善し、アナログパワーICの飛躍的な長寿命化を実現します。本技術の詳細を、米国シカゴで開催されたパワー半導体国際学会「ISPSD2018」にて、5月16日(現地時間)に発表しました。

自動車の電動化やIoTの進展により、車載用途や産業用途における低消費電力なアナログパワーICの需要が高まっています。車載・産業向けの半導体は、長期の利用が前提となっており、高い信頼性を保持することが求められます。現在開発の進んでいるNチャネル-LDMOSは、従来製品よりも低いオン抵抗と高い信頼性を特長としており、今後、モーター制御や電源ICなどでの活用が期待されています。

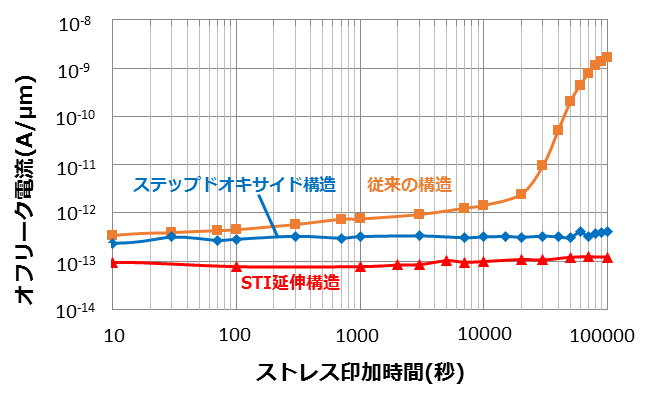

一方、Nチャネル-LDMOSは、オフリーク電流と呼ばれるオフ状態であっても漏洩する電流が長期の使用によって急激に増加することが確認されています注4。オフリーク電流が増加すると、回路動作の不具合や消費電力の増加などの問題が起こるため、LDMOSの信頼性向上には、オフリーク電流の増加を抑制することが求められていました。

そこで両社は、オフリーク電流増加のメカニズムを実験データとTCADを用いて解析し、ドリフト上のSTI領域注5を延伸した構造と、ドリフト上のSTIをステップドオキサイド注6に変更した構造が、オフリーク電流増加の抑制に有効であることを見出しました。第一のSTI領域を延伸した構造では、オン抵抗の増加があるものの追加工程が不要なため、ドライバー制御用ICなど、チップ全体に対してLDMOSの面積が小さい高耐圧アナログ回路での活用に適しています。第二のステップドオキサイド構造では、追加工程が必要になる一方、オン抵抗が低く高い電流が得られるため、モータードライバICやDC-DCコンバータ向け電源ICなど、半導体チップ全体に対してLDMOSの面積が大きい用途で有効です。

東芝デバイス&ストレージのトランジスタ設計技術と、ジャパンセミコンダクターの車載アナログIC製造で培ったプロセス開発技術を組み合わせることで、用途に応じてLDMOSの構造を使い分けできるプロセスを実現しました。

なお、ステップドオキサイド構造のLDMOSは、TCADシミュレーションによるデザインの最適化後、従来のLDMOSよりもさらにオン抵抗を低減できることが確認されています。両社は引き続き、オン抵抗と信頼性の検証を行い、2019年までに本技術を使ったLDMOSを搭載したアナログパワーICの製品化を目指します。今後も、本技術をはじめとした半導体プロセスに関する技術開発を促進し、高信頼性や低消費電力など顧客価値の高い半導体製品を提供していきます。

注1 LDMOS:Lateral Double Diffused MOS略。横方向拡散MOSのこと。

注2 ホットキャリア注入:ドレインーソース間の電界で加速されたホットキャリアが酸化膜等に注入されトランジスタ特性が劣化する現象のこと。

注3 オフリーク電流が初期状態から1桁増加する時間を寿命と定義

注4 国際学会「2017 International Conference on Solid State Devices Materials (SSDM 2017)」における東芝デバイス&ストレージの論文による。(論文タイトル:Hot-carrier Induced Drastic Off-state Leakage Current Degradation in STI-based N-channel LDMOS)

注5 STI領域:STIはShallow Trench Isolationの略。浅い溝に絶縁膜を埋めこみ、素子間・電極間を分離する領域のこと。

注6 ステップドオキサイド構造:階段状に酸化膜を形成したLDMOS構造のこと。

*本資料に掲載されている情報(製品の価格/仕様、サービスの内容及びお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。