信頼性と短絡耐久性を維持したSBD内蔵SiC MOSFETのオン抵抗低減に成功

2024年6月3日

東芝デバイス&ストレージ株式会社

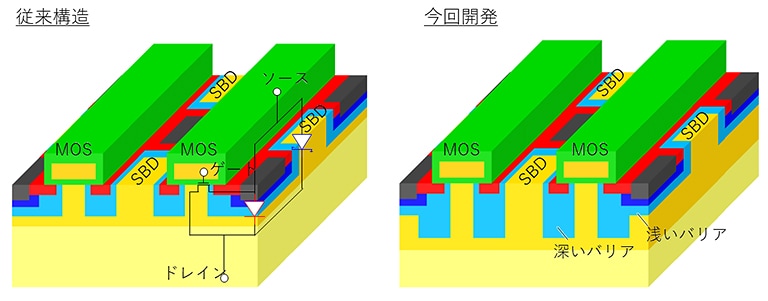

当社は、これまでのSBD注1内蔵SiC(炭化ケイ素)MOSFET注2を改良し、高い信頼性と短絡耐久性を維持したSiC MOSFETを開発しました。深さの異なるバリア構造注3を適切に配置したデバイス構造により(図1)、内蔵SBDの働きによる逆導通動作注4に対する信頼性を保ったまま、短絡動作注5時の破壊原因となるSBD部の電流成分を抑制しています。今回得られた設計技術を活用してデバイス構造を最適化することで、従来構造注6と比較してオン抵抗注7 (RonA) を約26%低減することに成功し、消費電力の低減に貢献します。

電力を供給、制御する役目を果たすパワー半導体は、あらゆる電気機器の省エネルギー化やカーボンニュートラルの実現に不可欠な半導体であり、自動車の電動化や産業機器の小型化などを背景に、今後も継続的な需要拡大が見込まれています。SiC MOSFETは従来のSi(シリコン)MOSFETよりも電力エネルギー変換効率を向上する次世代パワー半導体として注目され、近年急速に利用が拡がっています。しかし、SiC MOSFETには逆導通動作によって素子のオン抵抗が増加する信頼性の課題があるため、当社は、オン抵抗の増加を起こさずに逆導通動作が可能なSBD内蔵SiC MOSFETを開発しています。

SiC MOSFETのオン抵抗を低減することは、同時に短絡動作時にMOSFET部に過剰に流れる電流が増加するため、短絡動作の耐久性が低下します。また、逆導通動作の信頼性向上のために内蔵SBDを動作しやすくすることも、短絡動作時にSBD部の漏れ電流が増加し、短絡動作の耐久性の低下につながります。バリア構造を深く形成することで、短絡動作中のMOSFET部の過剰な電流とSBD部の漏れ電流の抑制がいずれも可能ですが、深いバリア構造はSBDからの電流の流れを妨げてしまい、ダイオード通電の信頼性が低下する懸念がありました。

そこで当社は、浅い領域と深い領域に作り分けたバリア構造の導入を検討しました。深いバリア領域による短絡動作時のMOSFET部からの過剰電流の抑制とSBD部の漏れ電流の低減の効果を発揮しながら、浅いバリア領域を残すことでバリア部に妨げられずにSBDからの電流が拡がる効果を両立しました。これらにより、逆導通動作に対する優れた信頼性を保ちながら、短絡動作時の耐久性を向上することが可能になりました。当社は、本技術を適用したSBD内蔵SiC MOSFETのテストサンプルを2023年12月より一部顧客に提供し評価していただき、さらなる性能改善を目指しています。

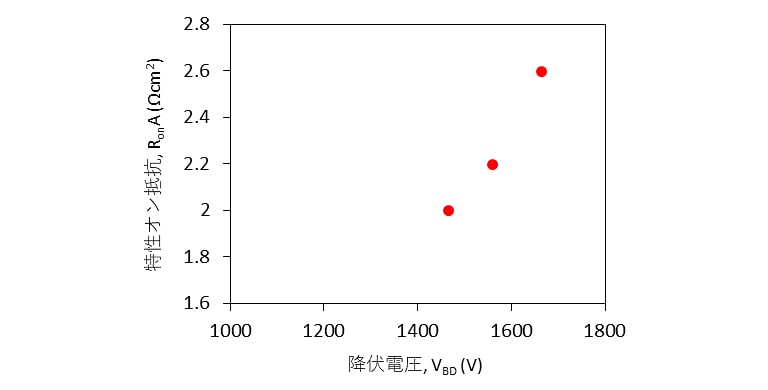

また、今回得られた設計技術によって高電圧印加時の電界を抑制でき、積極的なオン抵抗の低減が可能になりました。デバイス構造を最適化した1.2 kV級のSBD内蔵MOSFETを試作した結果、従来構造注6に対して約26%の低減となる2.0 mΩcm2の低いオン抵抗を実現しました(図2)。当社は、本技術の詳細を、6月2日〜6日にドイツ・ブレーメンで開催されているパワー半導体の国際学会「The 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD) 2024」で6月3日(現地時間)に発表します。

注1 SBD: Schottky Barrier Diode(ショットキーバリアダイオード)、金属とN型半導体が一つの結晶内でつながった、電流の流れを一方向に整える整流素子。

注2 MOSFET:Metal Oxide Semiconductor Field Effect Transistor(金属酸化膜半導体電界効果トランジスター)の略で、ゲート、ドレイン、ソースの3つの電極を持ち、ゲート電圧を印加することでドレイン-ソース間の電流のオンオフを切り替えるスイッチング素子。

注3 バリア構造:高電圧による高電界をコントロールするために設けられる、デバイス構造の要素。素子の性能に大きく影響する。

注4 逆導通動作:回路中の電流の還流によってMOSFETのソースからドレイン方向に電流が流れる動作。

注5 短絡動作:正常スイッチング動作時の短時間の導通に対して、制御回路の故障等の異常時に長時間の導通が起こる現象。一定時間の短絡動作で故障しない耐久性が求められる。

注6 2022年12月9日に発表した市松模様SBD配置型SBD内蔵MOSFET。

低オン抵抗と高信頼性を両立したショットキーバリアダイオード内蔵SiC MOSFETを開発

注7 オン抵抗:MOSFETが動作している時のドレイン-ソース間の抵抗値。

* 社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

* 本資料に掲載されている情報(製品の価格/仕様、サービスの内容及びお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。