SiCパワーモジュールにおける並列接続チップ間の寄生発振を高速スイッチングに対応する小さなゲート抵抗で抑制可能な技術を開発

2024年7月26日

東芝デバイス&ストレージ株式会社

株式会社東芝

東芝デバイス&ストレージ株式会社と株式会社東芝(以下、東芝グループ)は、SiC(炭化ケイ素) MOSFET注1を搭載したパワーモジュールにおいて、スイッチング動作時に並列接続間で生じる寄生発振注2を、従来比60%小さくしたゲート抵抗注3注4でも抑制可能な技術を開発しました。この技術を適用したパワーモジュールでは、低損失かつ、発振を抑え、高信頼なスイッチング動作が可能となります。

近年、カーボンニュートラルの実現に向けて再生可能エネルギーや、鉄道車両、産業機器などのエネルギー効率の向上が求められる中、高電圧や大電流を高速でスイッチング(オン/オフ)できるSiC MOSFETを搭載したパワーモジュールの需要が高まっています。パワーモジュールでは、電力変換器の小型化に対応するため高いスイッチング周波数が求められますが、周波数が高いほど消費電力あたりのスイッチング損失の割合が高くなるため、同損失を減少させることが求められています。

一方で、パワーモジュール内部で複数のチップを並列接続すると、チップ間の配線インダクタンス注5や、チップの寄生容量注6により発振回路が形成される場合があります。この寄生発振はモジュールの信頼性に影響するため抑制する必要があります。一般的にはゲート抵抗を用いて発振を抑制する手法が用いられますが、スイッチング速度が遅くなるためスイッチング損失とトレードオフの関係があります。SiC MOSFETを搭載したパワーモジュールでは高速スイッチングを行うため、小さいゲート抵抗で発振抑制可能な手法が必要とされていました。

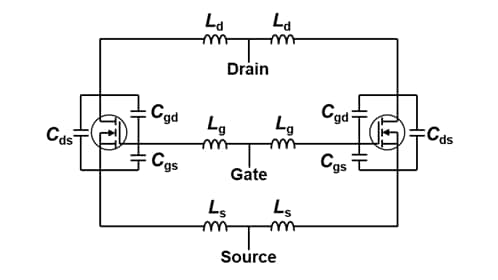

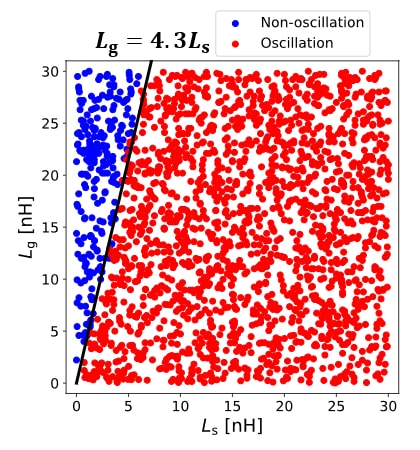

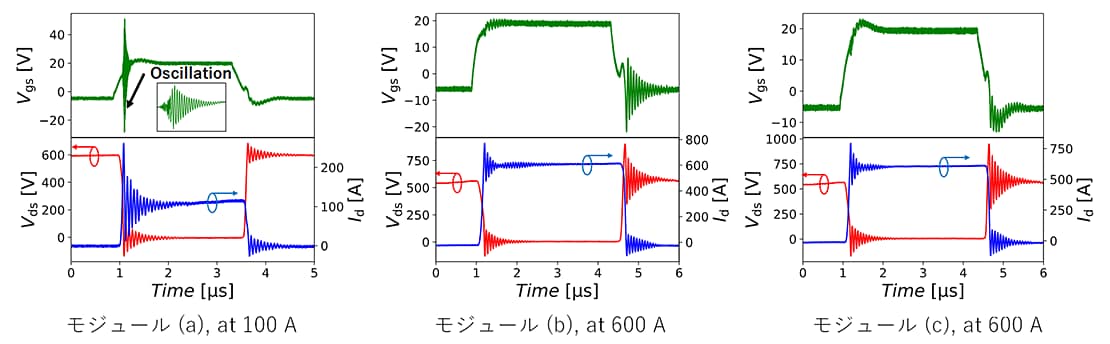

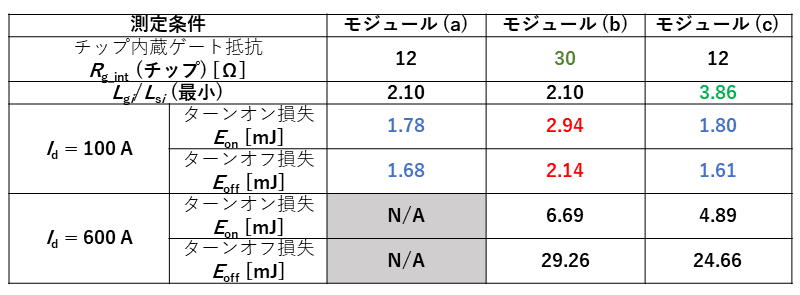

そこで東芝グループは、パワーモジュールの等価回路モデル(図1)から、寄生発振が生じる条件を理論的に導出し、寄生発振が生じにくい配線レイアウトを開発しました。具体的には、並列接続されたチップのゲート間インダクタンスLgとソース間インダクタンスLsの比率Lg/Lsがある一定値以下となった場合に寄生発振することを、シミュレーションで解析しました(図2)。寄生発振を抑制するためにはLg/Lsを大きくすることが重要であるため、Lg/Lsが異なるモジュールを試作し、スイッチング試験を行いました。Lg/Lsを大きくする手法では、ゲート抵抗を用いた発振抑制手法と比較して60%小さいゲート抵抗でも発振が抑制されていることを確認しました。(図3)

今回開発した寄生発振の抑制手法を開発中のパワーモジュールに適用することで、小さなゲート抵抗でも寄生発振を生じにくく、低損失かつ、発振を抑制し高信頼なスイッチング動作が可能なパワーモジュールを提供することが可能になります。今後、さらなる改良を進め、早期実用化を目指します。東芝グループは、本技術の詳細を、6月2日〜6日にドイツ・ブレーメンで開催されたパワー半導体の国際学会「The 36th International Symposium on Power Semiconductor Devices and ICs (ISPSD) 2024」において6月6日に発表しました。

注1 MOSFET:Metal Oxide Semiconductor Field Effect Transistor(金属酸化膜半導体電界効果トランジスター)の略で、ゲート、ドレイン、ソースの3つの電極を持ち、ゲート電圧を印加することでドレイン-ソース間の電流のオン/オフを切り替えるスイッチング素子。

注2 寄生発振:MOSFETがスイッチング時にゲート電圧が振動してしまうこと。MOSFETを単独使用する場合に比べ、MOSFETを並列接続で使用する場合、寄生発振が起こりやすい。

注3 当社従来製品での比較。

注4 ゲート抵抗:MOSFETにおいてゲート端子とソース端子の間に存在する抵抗のこと。ゲート電圧を印加した際に、電流の流れを制限する役割を果たす。ゲート抵抗の値は、デバイスのスイッチング特性や信号の立ち上がり時間に影響を与える重要な要素。

注5 配線インダクタンス:電流が流れる導体に固有の特性で、電流の変化に対して抵抗として機能する。電流が流れるときにその周囲に磁場が発生し、この磁場が変化すると電流の流れに反対する電圧(起電力)が生じる現象。

注6 寄生容量:電子回路の部品や配線間において意図しない容量のこと。コンデンサーのように電荷を蓄える能力を持ち、回路の動作に影響を与えることがある。特に、高速で動作する回路では、寄生容量が原因で信号の遅延や歪みが生じることがある。

Vgs: ゲートソース間電圧、Vds: ドレインソース間電圧、Id: ドレイン電流

* 社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

* 本資料に掲載されている情報(製品の価格/仕様、サービスの内容及びお問い合わせ先など)は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。