SiCトレンチMOSFETとスーパージャンクションショットキーバリアダイオードの損失低減を可能にする技術を開発

2025年6月9日

東芝デバイス&ストレージ株式会社

当社は、SiC (炭化ケイ素) トレンチMOSFET注1の損失 (オン抵抗注2) 低減を可能にした上で、UIS耐量注3を向上させる技術と、高温でのオン抵抗上昇を抑制するSiCセミスーパージャンクション注4ショットキーバリアダイオード (SJ-SBD) を開発しました。これら2つの技術により電気自動車や再生可能エネルギーシステムなどの電力変換用途におけるデバイスの信頼性と効率を大幅に向上させることに貢献します。

電力を供給、制御する役目を果たすパワー半導体は、あらゆる電気機器の省エネルギー化やカーボンニュートラルの実現に不可欠な半導体であり、自動車の電動化や産業機器の小型化などを背景に、今後も継続的な需要拡大が見込まれています。特にSiC MOSFETは、従来のSi (シリコン) MOSFETよりも電力エネルギー変換効率を向上する次世代パワー半導体として注目され、近年急速に利用が拡がっています。中でも、オン抵抗低減のためにゲートがトレンチ状に形成されているSiCトレンチMOSFETと、効率的な電力変換のために金属とSiCを接合したSiCショットキーバリアダイオード (SBD) は、電気自動車や再生可能エネルギーシステムなどの高効率電力変換用途で広く使用されています。しかし、これらの用途では高温環境下での動作が求められるため、信頼性や効率向上が課題となっています。

SiCトレンチMOSFETは、ゲート酸化膜を高電界から保護する必要がありますが、UIS耐量と電界保護構造注5に対する接地抵抗注6の関係が不明確で、ゲート酸化膜の信頼性とオン抵抗低減の両立が課題でした。

またSiC SBDは、従来のSi SBDに比べると高温での動作が可能ですが、高温では抵抗が増加するためオン抵抗も上昇することが課題でした。

そこで当社は、これらの課題に対応するため、2つの技術を開発しました。

1. SiCトレンチMOSFETのUIS耐量向上技術

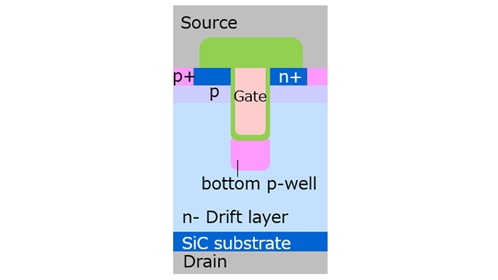

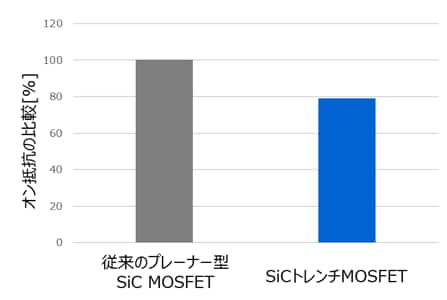

当社は、ゲート酸化膜の信頼性向上のためトレンチの下側に保護層であるBottom p-wellを形成したSiCトレンチMOSFET (図1) について、Bottom p-wellの接地抵抗を適切に下げることで、UIS耐量が向上することを確認し、これまで不明確であったUIS耐量と電界保護構造に対する接地抵抗の関係を明らかにしました。これによりゲート酸化膜の信頼性向上とオン抵抗低減を両立した構造最適化が可能であることを示しました。今回試作したSiCトレンチMOSFET (図1) は、従来のプレーナー型のSiC MOSFETに対してオン抵抗を約20%低減することを確認しました (図2)。

2. SiC SJ-SBDの特性改善

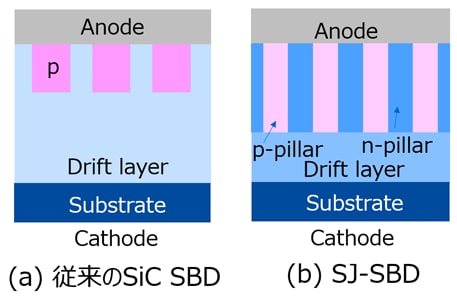

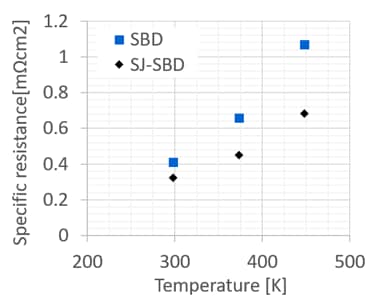

さらに当社は、ドリフト層に配置したピラー注7によりドリフトの層の抵抗を低減し、高温での抵抗増加を抑えることが期待できるSiC SJ-SBDを開発しました (図3 (b) ) 。従来のSiC SBD (図3 (a) ) とSiC SJ-SBDの温度を変えたときのオン抵抗注8の変化を比較すると、SiC SJ-SBDは、オン抵抗が低く、特に高温環境下でのその低減効果が大きいことを確認しました (図4)。これは、SJ構造によって、電界分布が均一化されたことでオン抵抗が低減されたためです。650V耐圧の SiC SJ-SBDでは、従来のSiC SBDと比較して、175°C (448.15K) の高温環境下でオン抵抗が約35%低減することを確認しました。

今回開発した2つの技術によりSiC トレンチMOSFETとSiC SBDのさらなる損失低減が可能になり、将来の高効率電力変換用途におけるデバイスの信頼性と効率をさらに向上させることが期待できます。特に、電気自動車や再生可能エネルギーシステムなどの分野での応用が見込まれます。今後、さらなる改良を進め、早期実用化を目指します。

当社は、本技術の詳細を、6月1日から5日に熊本で開催されたパワー半導体の国際学会「The 37th International Symposium on Power Semiconductor Devices and ICs (ISPSD) 2025」で発表しました。

この成果は、NEDO (国立研究開発法人新エネルギー・産業技術総合開発機構) の助成事業の結果得られたものです。

注1 MOSFET (metal-oxide-semiconductor field-effect transistor): 金属酸化膜半導体電界効果トランジスター。トランジスターの構造の一種。

注2 オン抵抗: MOSFETが動作している時のドレイン-ソース間の抵抗値。

注3 UIS (Unclamped Inductive Switching) 耐量: MOSFETが定格電圧を超えても、一定のエネルギーと電流の範囲内で破壊せずに耐える能力のこと。

注4 スーパージャンクション: ドリフト層にN型領域とP型領域を柱状 (pillar) に交互に配置した構造。

注5 電界保護構造: トレンチMOSFETがオフ状態 (電流を遮断している状態) のときに、ゲート酸化膜にかかる電界を軽減する構造。

注6 接地抵抗: Bottom p-well構造からソースメタルまでのp型領域の抵抗値の合計。

注7 ピラー: ドリフト層に不純物を柱状 (pillar) に形成したものを指す。SJ-SBDはp型半導体とn型半導体のピラーを交互に配置している。

注8 SBDのオン抵抗: 電流電圧カーブの傾きから算出し、SiC基板抵抗を差し引いた値。

* 社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。

* 本資料に掲載されている情報 (製品の価格/仕様、サービスの内容及びお問い合わせ先など) は、発表日現在の情報です。予告なしに変更されることがありますので、あらかじめご了承ください。