- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

Design & Development

Innovation Centre

At the Toshiba Innovation Centre we constantly strive to inspire you with our technologies and solutions. Discover how to place us at the heart of your innovations.

-

Knowledge

Knowledge

Highlighted Topics

Further Materials

Other

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

Optimising MOSFET performance – chip and package

The ongoing drive to improve power conversion performance while reducing system size and thermal dissipation is at the heart of today’s MOSFET development. And to achieve this, semiconductor manufacturers must consider both the underlying semiconductor processes and the packaging technology.

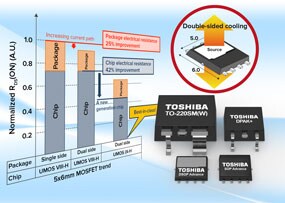

The image here shows the improvements in electrical performance brought about by some of the recent advances in device and package technology. As MOSFETs in the 5mm x 6mm footprint have evolved from UMOS VIII to UMOS IX-H technology, the new silicon has reduced RDS(ON) by 42%, while the lower DFPR of the DSOP Advance package is shown to be responsible for an additional 25% reduction.

This diagram, of course, is concerned only with electrical performance and does not express the increased thermal capability of the DSOP Advance package.

Toshiba’s white paper on the latest silicon and package advances for power MOSFETs provides more information on the capabilities of these new technologies.