- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

- Automotive SmartMCD™ (Integreted SoC Conbining Microcontroller and Driver)

- Automotive Brushless Motor Driver ICs

- Automotive Brushed DC Motor Driver ICs

- Automotive Stepping Motor Driver ICs

- Automotive Driver ICs

- Automotive System Power Supplies ICs

- Automotive audio power amplifier ICs

- Automotive Network Communication

Digital Devices

Wireless Devices

※

: Products list (parametric search)

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

Design & Development

Innovation Centre

At the Toshiba Innovation Centre we constantly strive to inspire you with our technologies and solutions. Discover how to place us at the heart of your innovations.

-

Knowledge

Knowledge

Highlighted Topics

Further Materials

Other

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

Paralleling MOSFETs: Some key considerations

Power MOSFETs are probably the most popular switching device in modern power solutions. They are generally easy to use and semiconductor manufacturers ensure that performance increases with each successive generation. Even so, on occasion, designers find the need to operate two MOSFETs in a parallel configuration.

Generally speaking, as MOSFETs do not suffer from thermal runaway (as can happen with bipolar devices), this makes paralleling them easier. As MOSFETs are voltage-driven, they simply need a stable and uniform voltage.

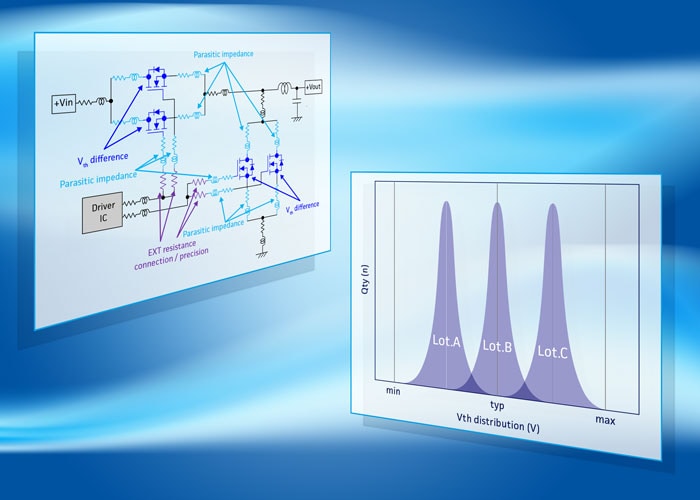

However, 'stable and uniform' can be more challenging than it might first appear. The PCB itself introduces unwanted ('parasitic') circuit elements that must be managed and designed for. Also, natural manufacturing variations in MOSFETs require consideration.

Individual device characteristics can vary within the tolerances of the datasheet specifications. The threshold voltage (Vth) is susceptible to variation and can cause current imbalance. Using MOSFETs from the same production lot or batch (with matched values of Vth) will reduce variations in current through each device.

When using external components, such as a gate resistor (Rg), tolerances will cause imbalance. However, the issue is not just the obvious components - all PCB traces have an element of resistance, inductance and capacitance. If there is a difference in the path length from the voltage source to the MOSFETs, this will also create imbalances. To address this, each gate pin trace must be kept as short as possible, thereby avoiding resistance accuracy problems and reducing the parasitic elements.

The same applies to power traces. Non-symmetrical traces here can cause destructive oscillations due to unbalanced impedances. Using surface-mount devices is one effective solution to decrease parasitic impedance, especially parasitic inductance.

Designing circuits with parallel MOSFETs is an important requirement in applications such as buck converters. The best solutions will be based on a careful selection of MOSFET devices and a methodical and balanced approach to circuit design. This is especially important in terms of managing the parasitic impedances that can occur in external resistances and PCB traces. Effectively addressing these issues can significantly simplify the implementation and effectiveness of parallel MOSFET architectures.

To find out more about important factors to consider when connecting MOSFETs in parallel click here: