- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

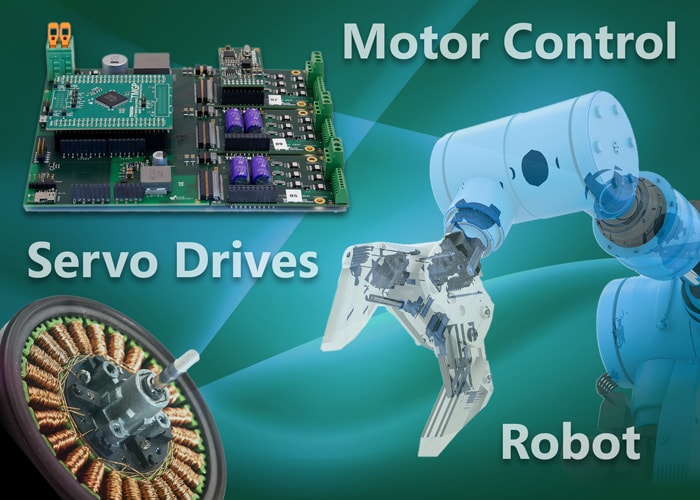

Factory Automation

Commercial Equipment

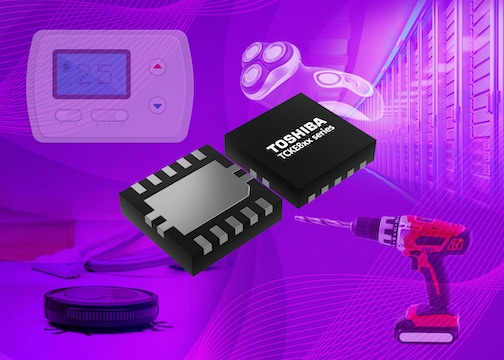

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

- Automotive SmartMCD™ (Integreted SoC Conbining Microcontroller and Driver)

- Automotive Brushless Motor Driver ICs

- Automotive Brushed DC Motor Driver ICs

- Automotive Stepping Motor Driver ICs

- Automotive Driver ICs

- Automotive System Power Supplies ICs

- Automotive audio power amplifier ICs

- Automotive Network Communication

Digital Devices

Wireless Devices

※

: Products list (parametric search)

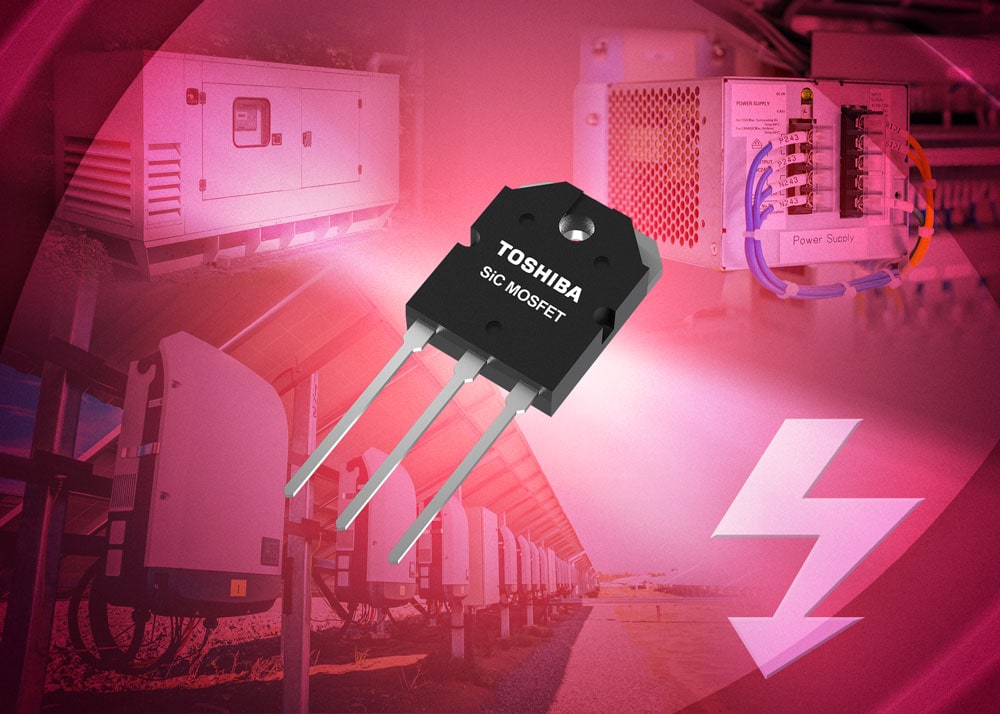

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

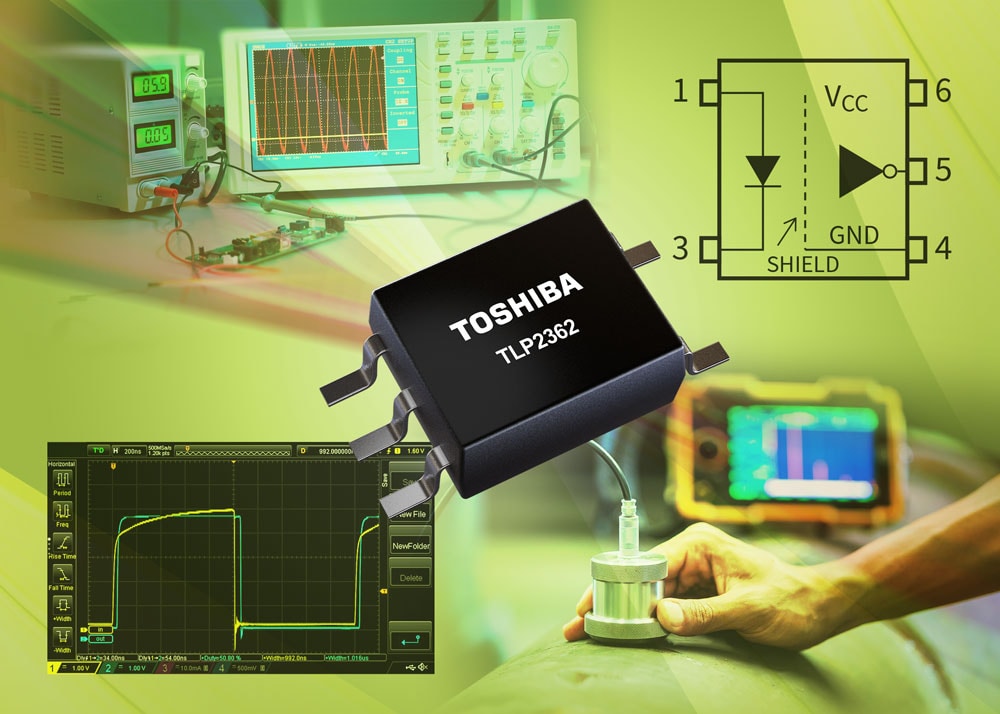

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

Design & Development

Innovation Centre

At the Toshiba Innovation Centre we constantly strive to inspire you with our technologies and solutions. Discover how to place us at the heart of your innovations.

-

Knowledge

Knowledge

Highlighted Topics

Further Materials

Other

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

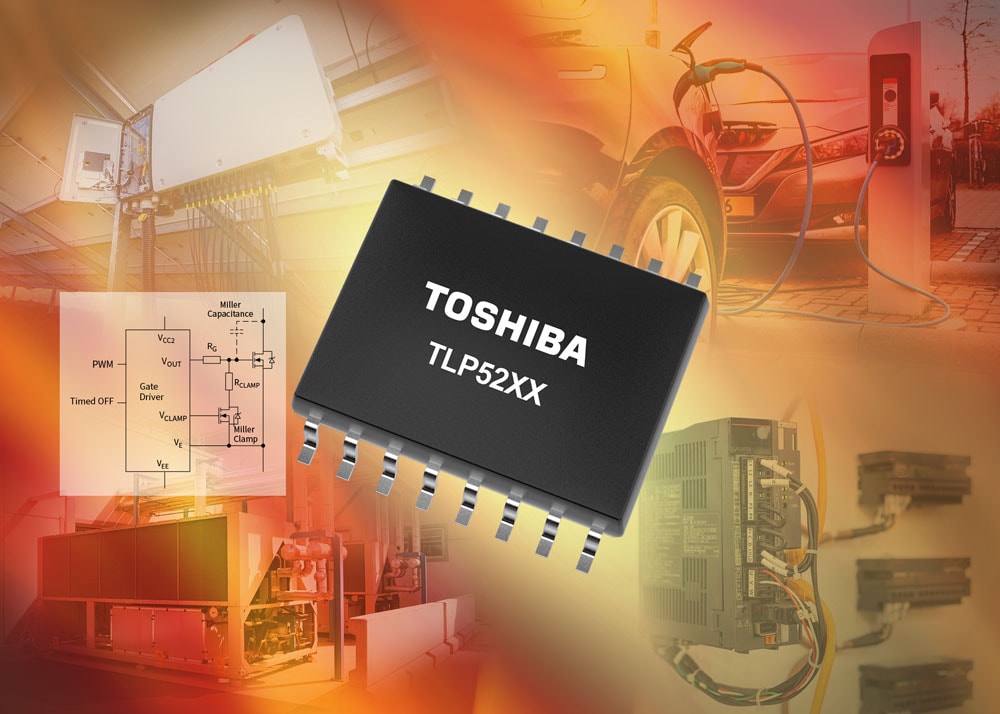

Correct drive for IGBTs and SiC MOSFETs enhances control and protection

The importance of switching devices is growing as many applications (such as EVs and renewable energy) rely on attaining previously unachievable levels of efficiency. Innovations in switching devices are allowing faster operation that, when implemented correctly, allow these lofty goals to be achieved.

Driving the gates of IGBTs, silicon MOSFETs and silicon carbide (SiC) MOSFETs correctly in high-frequency switching applications like EV-charging is vital for efficiency and reliability. Devices such as integrated smart gate drivers simplify this as they often include a Miller clamp and overcurrent detection using a ‘DESAT’ feature.

While IGBTs and Si/SiC MOSFETs are nominally off at VGS = 0V, their gate is often driven to a negative voltage for the OFF state, typically -7V for IGBTs and sometimes -5V for SiC MOSFETs. The reason for this is to prevent injected current entering the gate from the non-linear Miller capacitance, between collector/drain and gate, which occurs as the device switches off.

An alternative approach involves the use of a ‘Miller clamp’ – a separate MOSFET that shorts gate to emitter/source after the main drive signal has transitioned below a pre-determined level. The drive to the Miller clamp transistor must be carefully timed with the PWM OFF-signal to be effective. After the collector/drain has stabilised at its OFF-state voltage, the Miller clamp transistor can be switched off. The timing of this is not critical provided it is off before the next ON-state drive. If the negative gate drive voltage can be reduced or eliminated by using a Miller clamp circuit, the complexity of the required power supply is reduced and some valuable gate drive power is saved, contributing to enhanced efficiency.

Inadequate drive or an overload can cause power device failure, caused by the IGBT or SiC MOSFET coming out of saturation, dropping excess voltage and failing from over-dissipation. The driver can detect this condition by monitoring the collector/drain voltage of the device and if this can be interpreted as a fault, the driver will then immediately force the device off.

The technique is known as de-saturation detection or DESAT. The reaction time must be very rapid, as modern power devices are rated to withstand conditions such as short circuits for only a few microseconds.

The degree of integration now achieved in smart gate drivers allows designers to fit the parts as pre-certified and tested subsystems with performance that would be difficult to achieve with a discrete design. Comprehensive fault detection and reporting is built-in as effectively a single part, and reliability is extremely high. We prepared a whitepaper looking at the configuration of smart gate driver features. Access the paper here: