- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

- Automotive SmartMCD™ (Integreted SoC Conbining Microcontroller and Driver)

- Automotive Brushless Motor Driver ICs

- Automotive Brushed DC Motor Driver ICs

- Automotive Stepping Motor Driver ICs

- Automotive Driver ICs

- Automotive System Power Supplies ICs

- Automotive audio power amplifier ICs

- Automotive Network Communication

Digital Devices

Wireless Devices

※

: Products list (parametric search)

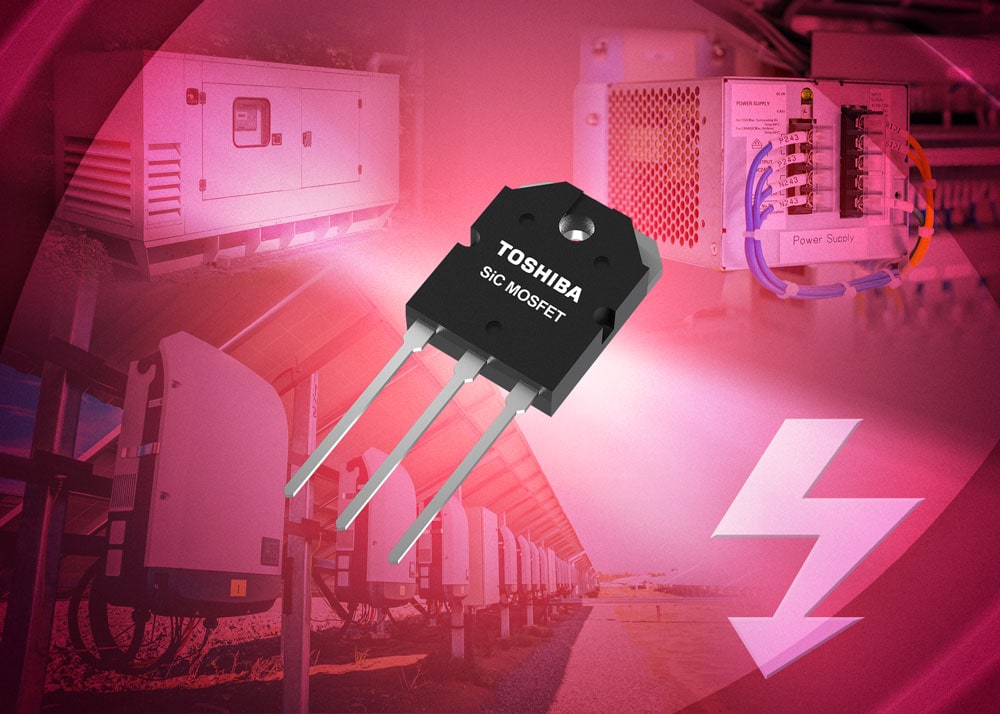

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

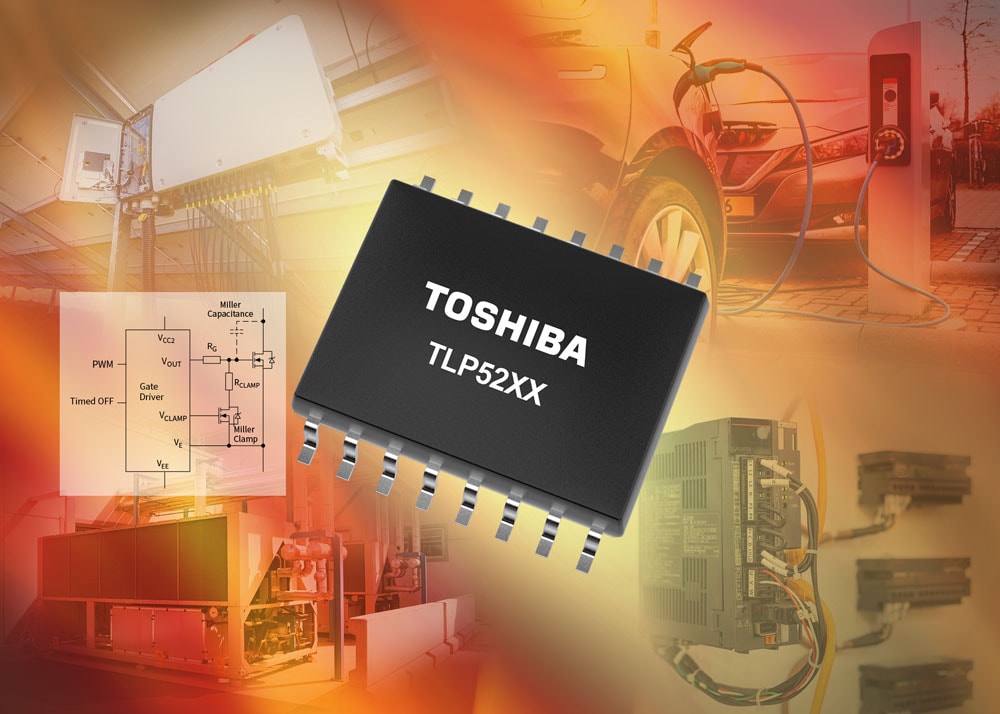

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

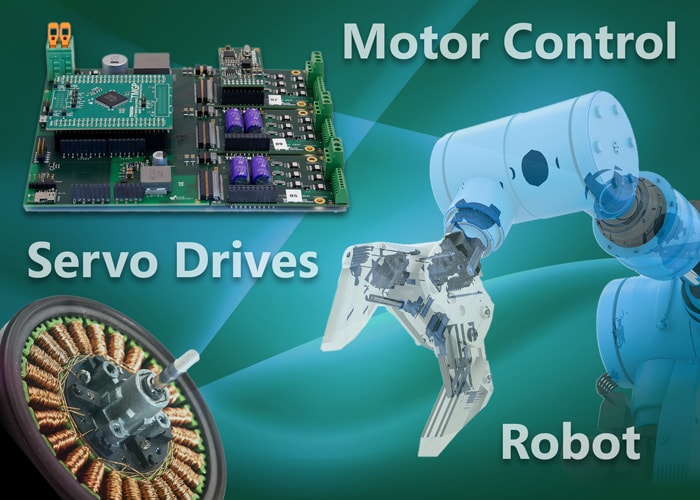

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

Design & Development

Innovation Centre

At the Toshiba Innovation Centre we constantly strive to inspire you with our technologies and solutions. Discover how to place us at the heart of your innovations.

-

Knowledge

Knowledge

Highlighted Topics

Further Materials

Other

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

I2C Bus Interface – An Overview

When it was devised four decades ago, the inter-integrated Circuit (I2C) interface was designed as a serial bus system for short-distance communication between microcontrollers and on-board peripherals. Based on its success, it helped to define system management bus (SMBus) for computer motherboards, and (PMBus) for components within power systems.

With just two signals, a serial data (SDA) line and a serial clock line (SCL), this single-ended synchronous interfacing technology only requires two wires. However, as the protocol calls for bi-directional communication designers require a degree of ingenuity when implementing any isolation circuitry.

I2C is typically used with an MCU or system-on-chip (SoC), and one or more target devices. The controller’s I2C pins are open drain meaning a resistor is required to pull the signals high, but this does avoid bus contention between two controllers.

The SDA signal is bi-directional. When implemented, the controller places its data on the SDA line to first select the target to be addressed. It is then used to select the register to access within that target. Once complete, the target returns the requested data over the SDA line. Targets also use the SDA line to acknowledge correct reception of the request (ACK) by holding SDA low or deny correct reception (NACK) by letting SDA be pulled high.

The SCL line is driven by the controller, defining the communication speed on the bus. Originally, I2C supported 100 kHz but, over the years, incremental improvements have increased this to 5 MHz. A target that requires more time can control the SCL signal together with the SDA - a feature known as clock stretching. Therefore, even with an isolated I2C interface, it is essential that bi-directional communication is supported.

I2C was only ever intended to be used for board-level communication, meaning that latencies within the isolation circuitry can hamper proper operation. According to the specification, the ACK/NACK signal must be valid after a setup time of 0.45µs in fast mode plus operation (1MHz). Also, in fast mode plus a target is expected to set up the SDA signal within 50ns after the falling edge of the previous clock bit.

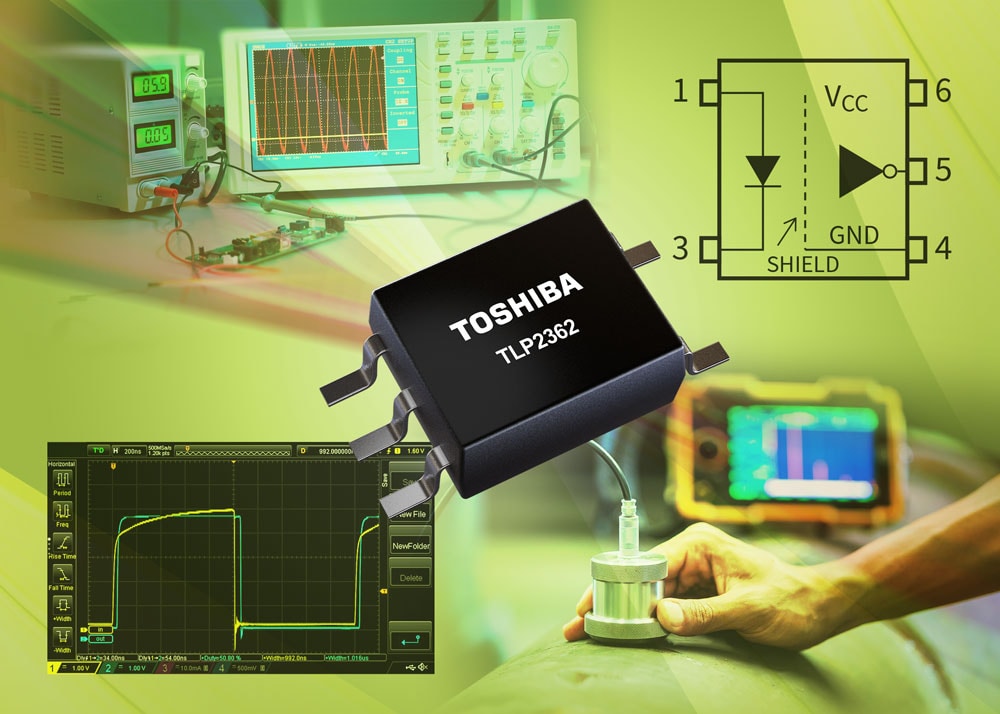

Toshiba offers a range of high speed, low latency optoisolators (such as it TLP2362) that, if put in the right circuit, support bi-directional communication for isolated I2C interfaces.

To view the whitepaper on using optocouplers to isolate the I2C bus, please click here: