-

My ToshibaSemicon

- 반도체 탑

-

애플리케이션Automotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

제품자동차 디바이스

Discrete Semiconductor

다이오드

트랜지스터

로직 IC

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

파워반도체※

: Products list (parametric search)

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTs바이폴라 트랜지스터※

: Products list (parametric search)

다이오드※

: Products list (parametric search)

마이크로컨트롤러모터 드라이버 ICIntelligent Power ICs※

: Products list (parametric search)

전원관리IC리니어 IC※

: Products list (parametric search)

범용로직IC리니어 이미지 센서기타 제품용 IC기타 제품용 IC

※

: Products list (parametric search)

-

개발/설계 지원

-

기술 자료

- 구매처

- 부품 번호 & 키워드 검색

- 상호 참조 검색

- 파라미터 검색

- 재고 확인 및 구매

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

3글자 이상 입력하세요. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

3글자 이상 입력하세요.

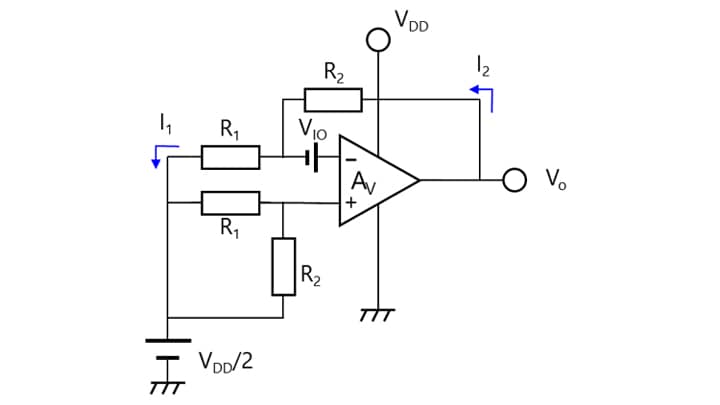

3.1. Input offset voltage (VIO)

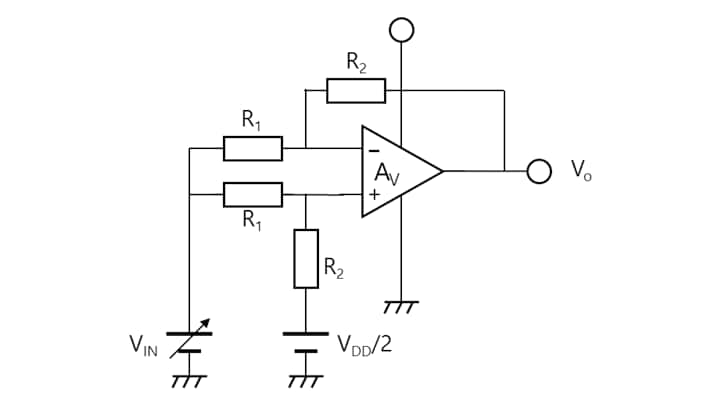

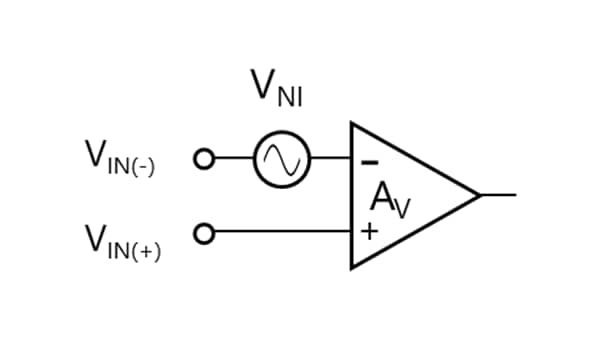

Figure 3-3 shows the ideal op-amp without an offset voltage source (VIO). When a common-mode input voltage is applied to VIN(+) and VIN(-) simultaneously, the output (Vo) voltage theoretically becomes VDD/2. In reality, however, it has a small error from VDD/2. The input offset voltage (VIO) is the voltage applied between VIN(+) and VIN(-) required to reduce the Vo error to zero. The definition of the input offset voltage is similar to that of the common-mode input signal rejection ratio (CMRR) detailed in the next section.

In real-world applications, the input offset voltage multiplied by the closed-loop gain (ACL) is added to the output voltage. Therefore, in the case of a sensor circuit, the maximum input offset voltage must be lower than its minimum sensitivity.

Let’s consider an op-amp with an input offset voltage of VIO. As shown in the test circuit for the input offset voltage shown in Figure 3-3, this op-amp can be regarded as the ideal op-amp with an external VIo voltage source connected to VIN(-).

The VIN(+) voltage becomes VDD/2. From the concept of a virtual short, the VIN(-) voltage also becomes VDD/2.

Therefore, the voltage at the intersection of R1 and R2 becomes VDD/2 – VIO. In the case of the ideal op-amp, I1 = I2.

I1 = (VDD/2 – VIO – VDD/2) / R1 = - VIO / R1 = I2

VO = VDD/2 – VIO + (–VIO / R1) × R2

= VDD/2 – VIO × (R1 + R2) / R2

This can be rewritten as follows to calculate VIO:

VIO = (VDD/2 – VO) × R1 / (R1+ R2)

Note that resistors have some tolerance. For actual measurement, the measured resistance values should be used.

VIO is a differential voltage between VIN(-) and VIN(+). Therefore, when an op-amp is used with a closed loop, the voltage obtained by multiplying this input offset voltage (VIO) by the closed loop-gain is added to the ideal output voltage. Since the VO voltage varies from device to device, it is necessary to consider the maximum offset voltage when creating a circuit design. If it exceeds a system’s tolerance, it is necessary to modify the circuit configuration in such a manner as to reduce the effect of the input offset voltage or select an op-amp with a lower input offset voltage.

The AC-coupled circuit is the simplest form of circuit to reduce the effect of the input offset voltage. Figure 3-4 shows an AC-coupled inverting amplifier. When capacitor C1 is connected in this way, current due to the input offset voltage does not flow through R1. Therefore, the input offset voltage has a DC gain of 1 and thus has less effect on VO.

Related information

Chapter3 Electrical characteristics

Related information

- Products

- Application Notes

- FAQs

- Parametric Search

- Stock Check & Purchase