- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

-

Knowledge

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

Countermeasures for Metastability

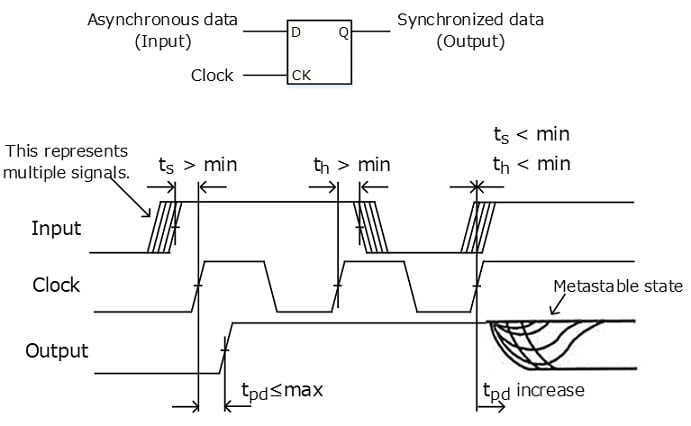

The output of a synchronous sequential circuit can potentially persist in an unstable equilibrium called a metastable state, depending on the timing of a data signal to be latched relative to the clock signal.

A sequential circuit enters a metastable state when its input setup and hold time (ts and th) requirements shown in the datasheet are not satisfied.

Metastability potentially occurs when an active input (e.g., a clock signal) and a passive input (e.g., a data signal) are asynchronous to each other. To prevent sequential circuits from entering a metastable state, the recommended timing conditions shown in the datasheet must be satisfied.

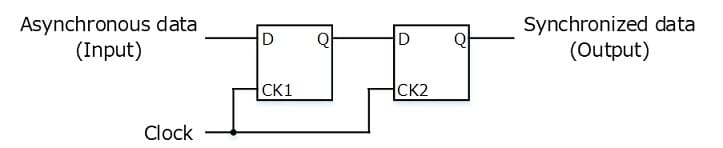

For example, when the CK and D inputs are asynchronous, they can be synchronized as shown below.

In this case, however, care should be exercised as to the cycle period and propagation delay of CK.

If they are close, the data signal might not propagate to the second flip-flop.

The synchronizer shown in Figure 5.3 consists of two flip-flops. The first flip-flop prevents an increase in tpd and a hazard from being transferred to the output of the second flip-flop.

Even in this case, care is needed when the phase difference between CK1 and CK2 is close to the CK-to-Q delay (tpd) of the first flip-flop.

Note: If the two flip-flops cannot operate from the same clock, metastability is avoidable by creating an inverted clock synchronous to CK1 and using it as CK2 (e.g., CK2 = /CK1).

Usage Considerations of CMOS Logic ICs

Products

Related information

- Application Notes

- FAQ