-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

ΔΣ型ADコンバーター

ADコンバーターは、アナログ信号をデジタル信号に変換しますが、ΔΣ型ADコンバーターは電力を効率よく供給する、スマート・グリッド・システムに欠かせない機能です。

はじめに

近年、省エネが私たちの生活において重要な課題となっています。いくつかの先進国では、省エネのために、電力を適正に消費・供給するスマート・グリッド・システムを導入しようとしています。スマート・グリッド・システムでは、電力の使用量を精密に計測してリアルタイムで通信するスマート・メーターが必要となります。当社は、この電力量計算にΔΣ型ADコンバーターを内蔵したマイクロコントローラーを開発しました。

これを機に、MCUパークでは、ΔΣ型ADコンバーターの解説をすることにしました。

実は、Δ∑型ADコンバーターはオーディオ・システムにおいて、信号伝達系統のノイズ除去に使われています。

「1ビット・オーディオ」と呼ばれていますが、この名称をお聞きになった方は多いのではないでしょうか。

従来のADコンバーター

ΔΣ型ADコンバーターの解説をするまえに、それとは異なる方式のADコンバーターを紹介します。

ADコンバーターには用途によっていろいろな変換方式がありますが、並列比較型、逐次比較型、追従比較型が一般的に使われています。それぞれについて簡単に説明します。

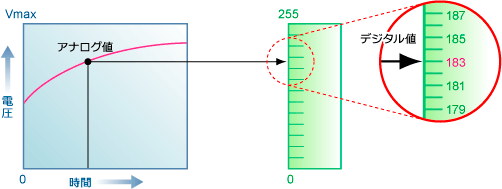

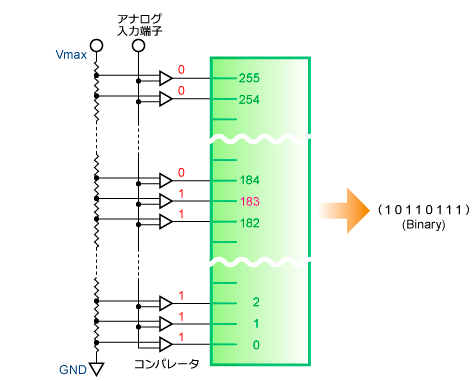

(1) 並列比較型ADコンバーター

アナログ入力の値を、あたかも、物差しで測るように、一気にデジタル値に変換します。変換時間が非常に短いのが特長です。ただし、回路規模が大きく、消費電力も大きいのが欠点です。

回路構成は以下の通りです。

変換最大電圧 Vmax とGND の間に抵抗を直列に接続し、その抵抗の途中から等間隔に出力端子を設けます。各抵抗端子をそれぞれのコンパレーターに入力し、アナログ入力値と大小比較をします。アナログ入力値が抵抗端子の出力よりも大きいときはコンパレーターが1を出力し、反対にアナログ入力端子が小さいときは0を出力します。この方法でアナログ入力値を短時間でデジタル値に変換することができます。

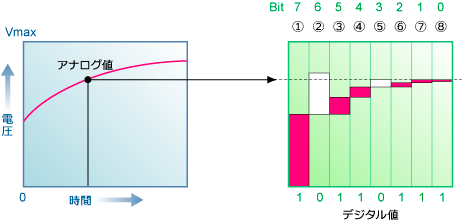

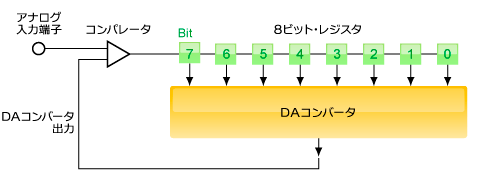

(2) 逐次比較型ADコンバーター

アナログ入力信号と、ADコンバーターが自ら作り出したアナログ信号とを比較して、アナログ・デジタル変換を行います。8ビットの逐次比較型ADコンバーターを例に変換方法を説明します。

まず、ADコンバーターの中にDAコンバーターを搭載します。DAコンバーターはADコンバーターと反対に、デジタル値をアナログ値に変換する回路です。

最初、8ビットのMSB(最上位ビット:ビット7)を1に、他の7つのビットを0にします。つまり、2進数で(10000000)とします。これをADコンバーター内にあるDAコンバーターに入力しますと、その出力は最大出力Vmaxの1/2となります。このDAコンバーターの出力とアナログ入力信号との大小をコンパレーターで比較します。アナログ入力信号が大きい場合はMSBを1のままにしておきます。反対にアナログ信号が小さい場合は0とします。図の例では、入力信号がDAコンバーターの出力よりも大きいので、MSBは1のままとなります。

次に、MSBから2番目のビット(ビット6)を1にします。MSBが1ですので、8ビットの2進数データは(11000000)となります。これを、DAコンバーターに入力し、その出力とアナログ入力信号を比較します。アナログ入力信号が大きいときはそのビットを1に、小さいときは0とします。今の例では、アナログ入力が小さいのでビット6は0となります。さらに、MSBから3番目(ビット5)に移り、同じように(10100000)をDAコンバーターに入力し、比較結果を得ます。

このようにMSBから各ビットを一つずつ変化させコンパレーターで比較することをビット0まで8回行うと、最後に残った2進数がアナログ入力信号から変換されたデジタル値になります。

この逐次比較型ADコンバーターは、回路面積は小さく、消費電流も少ないことから、マイクロコントローラーに内蔵されるADコンバーターに適しています。

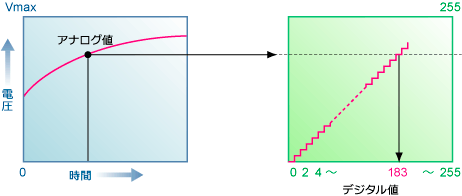

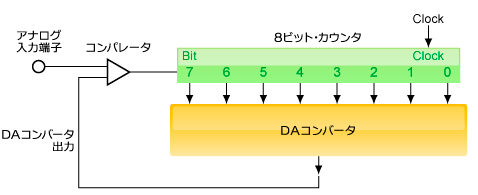

(3) 追従比較型ADコンバーター

アナログ入力信号を、階段を上るように下から追いかけて、高さが一致したときの階段の段数でデジタル値を決定する方式です。

回路構成はDAコンバーターとカウンター、および、コンパレーターからなります。カウンターを1つ進ませるたびに、カウンター出力(デジタル値)をDAコンバーターでアナログ値に変換し、コンパレーターで外部からのアナログ信号と比較します。

カウンターが進んで、あるカウント値で外部アナログ信号と一致した時、そのカウント値がデジタル変換値となります。

追従比較型では高精度の変換が得られますが、変換時間が長いのが欠点です。

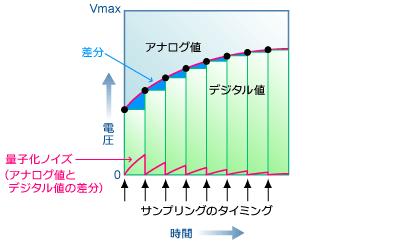

サンプリングと量子化ノイズ

アナログ値をデジタル値に変換するためには、まず、アナログ信号を定期的にサンプリングする必要があります。サンプリングされた値はデジタル値に変換されますが、このとき、デジタル値の最小の単位(LSB)の1個分の値、もしくはその1/2の値の最大変換誤差が生じます。これを量子化誤差(量子化エラー)と呼んでいます。

さらに、別の問題もあります。一つのサンプリングからその次のサンプリングまでの間のアナログ信号はデジタル値に変換されることはありません。したがって、アナログ入力信号と、それをデジタルに変換した信号の波形は一致せず、差分が生じます。一般的に波形を歪(ゆが)めるものをノイズと呼びますが、今話題にしているノイズは外部からやって来たのではなく、アナログ値をデジタル値に変換(量子化)したために生成されたもので、「量子化ノイズ」と呼ばれています。量子化ノイズは先ほどの量子化誤差を含んでいます。

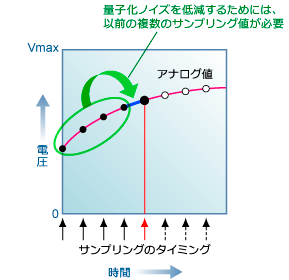

アナログ・デジタル変換では、アナログ値をサンプリングする限り、この量子化ノイズは避けられません。では、どうしたら量子化ノイズを小さくできるでしょうか。すぐに思いつくのはサンプリングの頻度を上げることです。サンプリングの回数を増やせば増やすほど量子化ノイズは減少します。しかし、サンプリングの回数を極端に増やすとアナログ・デジタル変換のための時間が短かすぎて、変換が間に合わなくなります。

ここで視点を変えて、量子化ノイズをもっと低減できる方法がないか、考えてみましょう。

ADコンバーターに入力されるアナログ信号はサンプリングされた値だけですが、サンプリングとサンプリングの間の信号はゆるやかに変化しています。この波形を再現しようとすると、一つのサンプリング・データだけでなく、それ以前のサンプリング・データをいくつか使って滑らかな曲線を作る必要があります。

ΔΣ型ADコンバーターはサンプリング情報を巧みに編集することにより、量子化ノイズを低減して高精度のアナログ・デジタル変換を実現しています。

それでは、いよいよΔ∑型ADコンバーターの紹介をします。

Δ(デルタ)は引き算、∑(シグマ)は足し算を表しています。Δ∑型ADコンバーターは、アナログ入力信号から基準電位を「引き」、その差分を次々に「足し合わせ」てアナログ・デジタル変換を行います。

実際の回路は非常に複雑ですが、ここではもっと単純な回路構成例を使って、Δ∑型ADコンバーターの動作を説明します。

ΔΣ型ADコンバーター

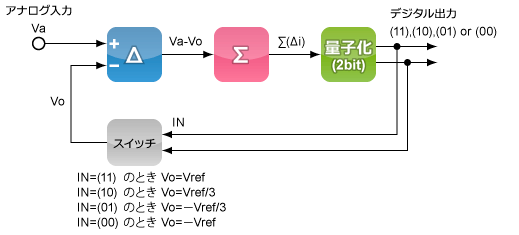

(1) 回路構成

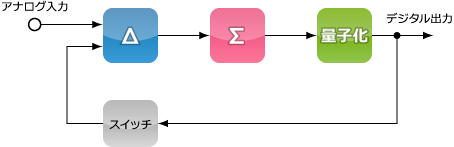

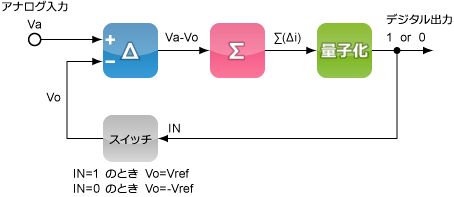

ΔΣ型ADコンバーターはΔΣ変調という方式でアナログ・デジタル変換を行っています。ΔΣ変調は4つの機能ブロックから構成されたシステムで実現されます。入力信号の値とある固定電圧値の差を求める「Δ(減算)回路」、その減算した結果を次々に加えて行く「Σ(加算)回路」(または「積分回路」)、加算結果をある値と比較して大小関係を見つける「量子化回路」、その量子化回路の出力(デジタル値)に応じて動作する「スイッチ回路」です。

(2) ΔΣ変調動作

ΔΣ変調の動作を説明します。

アナログ信号Vaが入力端子から減算回路に入力されます。減算回路のもう一つの入力信号Voの値はVref か –Vref のいずれかですが、最初はVref だとします。すると減算の結果はVa-Vref (=Δ)となり、これが加算回路に入力されます。実は、Vrefはアナログ入力値の最大値か、それよりも大きな値です。したがって、Δはマイナスの値となります。

加算回路の初期値は 0Vであると仮定しますと、加算の結果は0+Δ=Δとなります。

この値は量子化回路に取り込まれ、量子化回路の基準電圧と比較されます。ここで、基準電圧を 0V とします。量子化回路の出力は、入力が0Vより小さい値のときは0、大きいときは1となります。今の場合、量子化回路の入力値はΔ(マイナスの値)ですので量子化回路の出力は0となります。ここまでが、1つのクロック期間に行われます。

次のクロック期間のはじめには、スイッチ回路から-Vrefが出力されます。なぜなら前のクロック期間の量子化回路の出力が0だったからです。次のアナログ入力Va’に対して減算回路の出力の値はVa’-(-Vref)=Va’+Vref (=Δ’)となり、これを受けて加算回路の出力はΔ+Δ’となります。この値が0Vよりも大きい場合(プラスの値)は量子化回路の出力は1となり、0Vよりも小さい場合(マイナスの値)は同回路の出力は0となります。

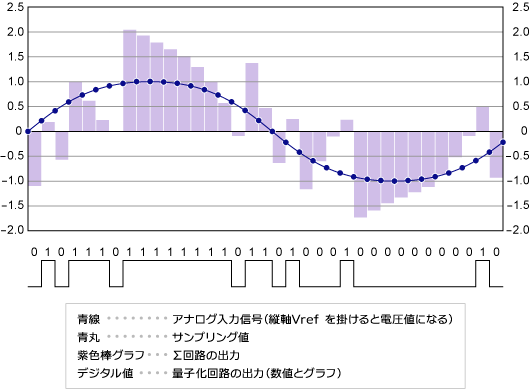

このように、減算、加算、比較(量子化)を繰り返すことにより、デジタル値の1、もしくは0の数列が得られます。この数列の1と0の出現頻度から、入力されたアナログ信号が再現できるのです。

ところで、加算回路の出力(次の図の棒グラフ)を見ますと、入力されたアナログ信号がゆったりと変化しているのとは違って、かなり上下に振動しているのがわかります。特に、入力アナログ信号が0Vと交差するあたりでは棒の上がり下がりが急激に変わります。一方、アナログ入力信号の山の頂の近辺では、一度大きく上に跳ね上がった後、緩やかに減少しています。同じように、アナログ信号の谷の底の部分では、大きく下がった後、徐々に上向きに変化していきます。このように、ΔΣ変調されたアナログ信号(Σ回路の出力)は、絶対値で見れば、入力されたアナログ信号から大きくはずれています。しかし、アナログ入力信号の大きさや変化の情報はしっかり確保していることがわかります。

少し難しいですね。でも、図を見ると、最終的に得られた1と0の数列から、何となく元のアナログ信号を

再現できそうな気がします。つまり、デジタル値で、

1が続くとアナログ入力信号の山の部分、

0が続くと谷の部分、

1と0が交互に出てくると傾斜部分

ということが分かります。

高精度のための技術

簡単な回路で動作原理の説明をしましたが、実際の回路では高精度のアナログ・デジタル変換を実現するためにさまざまな工夫が凝らされています。

まず、アナログ信号のサンプリングの頻度を高くします。一般的にサンプリングの頻度を上げますとADコンバーターの量子化ノイズが減少しますが、それはΔΣ型ADコンバーターにも当てはまります。

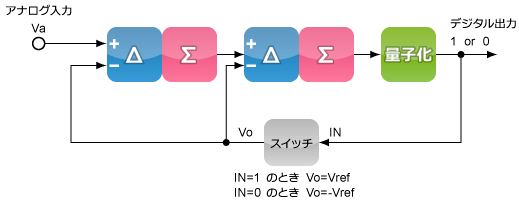

さらに、アナログ入力波形を精度よく再現するためには、サンプリング間の滑らかな変化を捉える必要があります。そのために、ΔΣ変調では、差分を取り、それを加算するという手段を用いていますが、このΔとΣの動作を1段だけでなく、もう1段追加しますと変換精度が向上することがわかっています。前者を1次のΔΣ変調、後者を2次のΔΣ変調と呼びます。通常、ΔとΣを4段にした4次のΔΣ変調を行って精度を確保しています。

また、アナログ・デジタル変換精度を向上させるために、量子化回路の量子化数を増加させる方法もあります。

今までの説明では量子化回路の出力は1か0かの1ビット情報でしたが、ここを量子化回路の入力値にあわせて、たとえば2ビットのデータにすることができます。すると、量子化回路の出力は、(11)、(10)、(01)、および、(00)のいずれかとなり、この4つの値に応じて、スイッチ回路の出力も、それぞれ Vref、Vref/3、-Vref/3、および、-Vref の4つの値を取ることになります。

さらに、この量子化のビット数をもっと増やしますと、アナログ入力信号の変化をより細かく取り込むことができ、変換精度を大幅に向上することができます。

変換精度を向上するために、Δ∑型ADコンバーターが、実に独特な変換方法を用いていることが

わかっていただけたと思います。