- 半導體首頁

-

應用Automotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

產品車用元件

Discrete Semiconductor

Diodes

電晶體

通用邏輯IC

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

功率半導體※

: Products list (parametric search)

隔離器/固態繼電器Photocouplers

Digital Isolators

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTs雙極性電晶體※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

微控制器馬達驅動 ICs智能功率 ICs※

: Products list (parametric search)

電源管理 ICs線性 ICs※

: Products list (parametric search)

通用邏輯 ICs線性影像感測器其他產品其他產品

※

: Products list (parametric search)

-

開發/設計支援

開發 / 設計支援

-

技術知識

- 購買管道

- 型號 & 關鍵字搜尋

- 交叉搜尋

- 參數搜尋

- 線上庫存查詢跟購買

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

型號需要超過三個文字以上 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

型號需要超過三個文字以上

Serial Interface

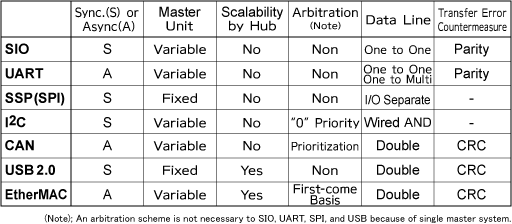

A microcontroller has several kinds of serial interfaces. Toshiba produces TX03 microcontroller series which adopt high performance ARM Cortex™-M3 core as the CPUs. The M360 group in TX03 series is the group of microcontrollers which integrate serial interfaces selectively among SIO, UART, SSP (SPI), I2C, USB, CAN, and EtherMAC. The purpose of this article is to introduce each serial interface briefly.

Synchronous or Asynchronous interface

Synchronous Interface

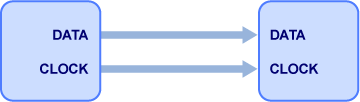

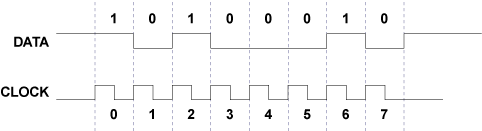

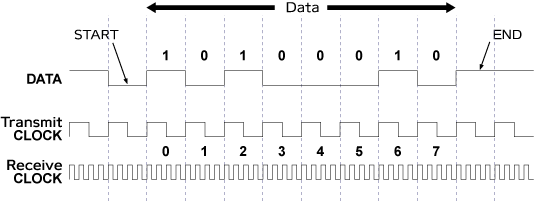

Serial interface transmits or receives a set of binary data through one line or two. A primitive serial interface has only one transmitter and only one receiver and one line for data transfer and another line for a clock signal are connected between them. The transmitter sends a set of data to the receiver with the manner of one bit data by one clock pulse. And the receiver catches the transferred data at the timing of the edge of the clock. This is called a “synchronous” system. This serial interface is quite simple and easy to do serial communication.

Asynchronous interface

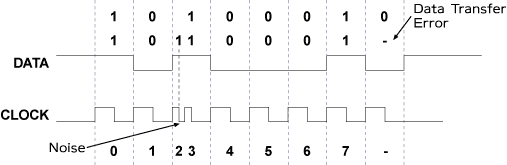

Even though the synchronous interface is simple, it has a drawback of low noise immunity. The data are transmitted and received in synchronization with the clock, so wrong data-transfer may occur if some noise affects the clock signal. For example, it will happen that the clock signal is forced to be low in short time due to some noise while it is in high level. In such a case, the clock may be treated as two pulses, which causes the malfunction that the serial transfer finishes by one clock before. This kind of problem always has to be considered in the synchronous systems.

One of the best countermeasures against the noise effects is to eliminate the clock signal in the system. There are no noise problems on clocks without any clock signals.

One of the side effects is that the receiver can not understand the timing when it should catch the data. This may disable the communication even though the noise problems are eliminated. So there must be some way to get the timing even without the clock signal. The combination of the followings is one solution.

(1) To catch receive data by using higher frequency clock than transmit clock.

(2) To clarify the start and stop timings when a set of data is transferred.

The receive clock has a higher frequency, for example, 4 time higher, than the transmit clock. In this case, 1bit data (1 or 0) is supposed to be valid when the same data is caught three-times continuously or four by the receive clock (‘4 time higher’ is just an example. 16 times is sometimes used.)

And it is common that a start bit ‘0’ is added before a set of transfer data, and a stop bit ‘1’, after the data, in order to comprehend when the content of the data is transferred.

Data transfer without clock signal lines is called asynchronous transfer. The asynchronous communication system has better noise immunity but receiver’s circuits would be more complicated.

Data Format

Serial communication has, usually, a regulation of its data sequence. One example of the sequences is like that at the beginning a start code is followed by an address of the transmitter, an address of the receiver, transfer data, an error detection code, and a stop code at the end, which shows that the transfer data is surrounded by the special function codes. As in this example, a data format is a rule to specify the position of each data and code in the sequence of a transmitted data. Each code and the transfer data must be positioned correctly according to a data format. Please consider a train as another example.

A train consists of a car for train operator, cars for ordinary passengers, priority cars ( like women car ), dining cars, special cars with special fee, and so on. Each train is a combination of those cars and there will be a definite rule of the sequence of cars.

For example, the car for train operator cannot be in the middle of the train, or dining car cannot be at the end of the train. Even though the sequence of the cars is determined by a railway company, the passengers also understand the car sequence, and at the railway station, they will wait for the train at the position where the car they wants to ride on will stop.

This sequence is the format. And if the railway company ignore the sequence and prepare trains with arbitrary sequence of cars, the morning commuting passengers at the railway stations will get into a panic.

Like this example, when a transmitter transfers string data with ignoring the data format, the receiver can not receive the data correctly. Unless comprehending the data format, serial interface network can never be constructed.

Master and Slave

There must be at least two relevant players, a transmitter and a receiver, in the serial communication system. One of them conducts the others. The conductor is called a master, and the others, slaves. (Master and Slave relation is different from Transmitter and Receiver relation.)

The importance of the distinguishing Master from Slave is in the system where many serial interfaces are existing. Those interfaces share the same lines to communicate each other. If there are no conductors and every interface operates individually, the system becomes chaos easily. So only one of them works as a master to conduct others, slaves, which obey the master’s instructions. And the serial data are transferred only between the master and one of the slaves, never between a slave and a different slave.

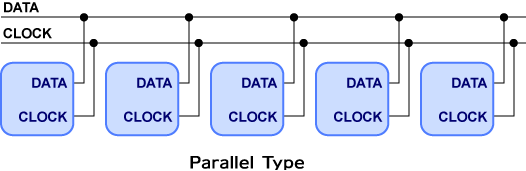

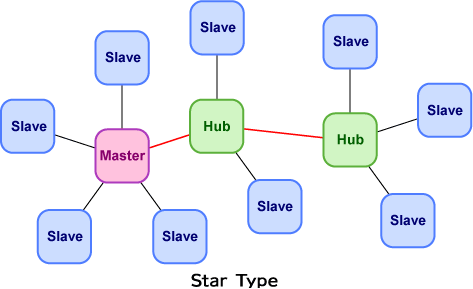

There are two kinds of systems in the master-slave structures. One of them is a system that every interface can become a master occasionally (no more than one can be a master), and the other is that a master is already predetermined and the others can not become masters at all. In the former system every interface shares the same signal line, which makes a parallel structure system (Parallel type). And in the latter, each slave interface is connected to the same master and no lines between slaves. This is called Star type structure.

While Star type system does not have any problems how to determine a master, Parallel type does. One of the solutions of the problems is prioritization of each interface to be a master. When an interface competes another, the interface with higher priority wins to be a master. This will avoid the ugly conflict among the interfaces.

System Scalability

Many serial interfaces can be connected to one signal line in Parallel type structure. There is, however, a limitation on the number of the interfaces sharing the line. Too many interfaces degrade transfer speed, or make lower priority interfaces never become a master due to sever competition. So usually, 128 or 256 is the limitation number in Parallel type systems.

Star type is scalable by using a hierarchy structure. A slave interface is connected to a system through a buffer named a ‘hub’. And a hub can connect to another hub, too. Though the expansion is simply done in such manner, this hub-to-hub hierarchy would be no more than five stages, as an example, in some Star types.

Countermeasure to Transfer Error

When transmitting a data over a long distance, the data may not be the same as the original transmitted data affected by noises. There may be another transfer error caused by accidental collision of outputs of a plural of interfaces, or by some malfunction of the interfaces.

One of the countermeasures for noise problem on the data line is to send a pair of complementary data with 2 wire signal structure. The receiver checks the ‘difference’ between one wire voltage and the other wire one.

And parity check is a simple method to detect if an error has occurred or not while transferring the data. One parity bit is added at the end of a set of transfer data so that the number of “1” in the transfer data becomes even number, and the receiver does parity check when receiving the data by examining the number of “1” is even number or not. More sophisticated error check is CRC (Cyclic Redundancy Code) methodology. CRC is a sum of the transfer data which is added at the end of the transfer data by the transmitter, and the receiver calculates the sum of the received data and compares both sums. If those two sums are identical, the transfer was successful. If, not, there must be some error in the received data. When the receiver detects transfer errors, the transmitter is asked to send the data again.

As explained above, there are so many kinds of serial interfaces. In a table such serial interfaces are summarized as SIO, UART, SSP (SPI), I2C, CAN, USB, and EtherMAC which are described in next chapter.