- General Top

- SEMICONDUCTOR

- STORAGE

- COMPANY

-

My ToshibaSemicon

- Semiconductor Top

-

ApplicationsAutomotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

ProductsAutomotive Devices

Discrete Semiconductor

Diodes

Transistors

Logic ICs

Analog Devices

- Automotive SmartMCD™ (Integreted SoC Conbining Microcontroller and Driver)

- Automotive Brushless Motor Driver ICs

- Automotive Brushed DC Motor Driver ICs

- Automotive Stepping Motor Driver ICs

- Automotive Driver ICs

- Automotive System Power Supplies ICs

- Automotive audio power amplifier ICs

- Automotive Network Communication

Digital Devices

Wireless Devices

※

: Products list (parametric search)

Power SemiconductorsSiC Power Devices

※

: Products list (parametric search)

Isolators/Solid State RelaysPhotocouplers

Digital Isolators

Solid State Relays

Fiber Optic Transmitting Modules

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTsBipolar Transistors※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

MicrocontrollersMotor Driver ICsIntelligent Power ICs※

: Products list (parametric search)

Power Management ICsLinear ICs※

: Products list (parametric search)

General Purpose Logic ICsLinear Image SensorsOther Product ICsOther Product ICs

※

: Products list (parametric search)

-

Design & Development

-

Knowledge

- Where To Buy

- Part Number & Keyword Search

- Cross Reference Search

- Parametric Search

- Stock Check & Purchase

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

require 3 characters or more. Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

require 3 characters or more.

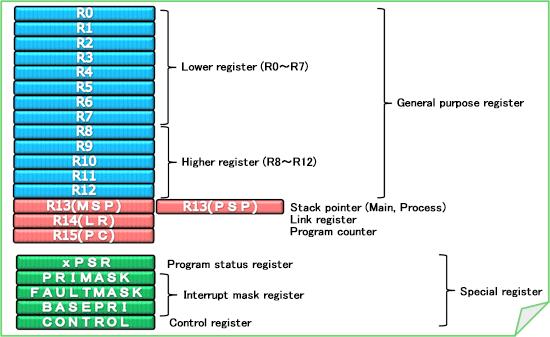

2-10-1. Operation Mode and Stack Pointer (1)

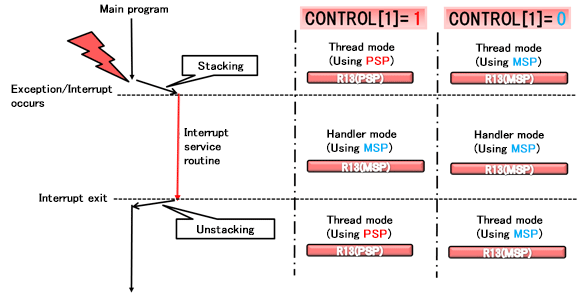

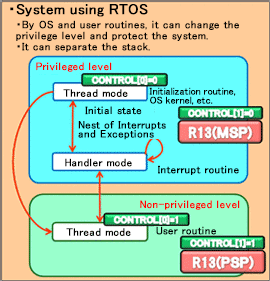

Arm® Cortex®-M3 has two privileged levels (Privilege/Non-privilege) and two operation modes (Thread/Handler).

For embedded usage, a basic configuration with only privileged level or a configuration to switch between Privilege and Non-privilege can be selected.

At the privileged/non-privileged level, by switching between the main stack (MSP) and process stack (PSP) assigned to register R13, the stack area can be separated and managed by processing functions such as the OS kernel and user routines.

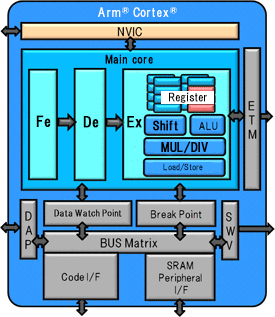

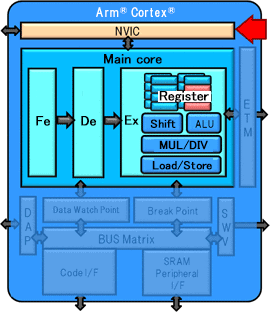

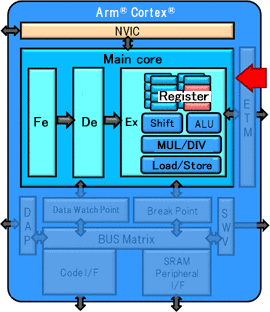

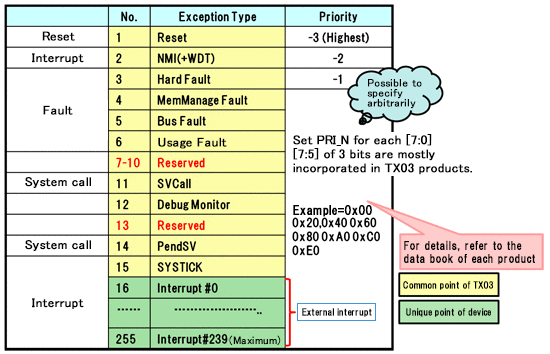

Chapter 2 Arm® Cortex®-M3

* Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.