- 半導體首頁

-

應用Automotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

產品車用元件

Discrete Semiconductor

Diodes

電晶體

通用邏輯IC

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

功率半導體※

: Products list (parametric search)

隔離器/固態繼電器Photocouplers

Digital Isolators

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTs雙極性電晶體※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

微控制器馬達驅動 ICs智能功率 ICs※

: Products list (parametric search)

電源管理 ICs線性 ICs※

: Products list (parametric search)

通用邏輯 ICs線性影像感測器其他產品其他產品

※

: Products list (parametric search)

-

開發/設計支援

開發 / 設計支援

-

技術知識

- 購買管道

- 型號 & 關鍵字搜尋

- 交叉搜尋

- 參數搜尋

- 線上庫存查詢跟購買

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

型號需要超過三個文字以上 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

型號需要超過三個文字以上

A small noise is superimposed on the output voltage of an LDO. What can I do to reduce the noise?

For noise-sensitive loads such as analog circuits and IC power supplies, use an LDO with low output noise voltage (VNO) and a high ripple rejection ratio (R.R.). The sources of noise that appear at the output of an LDO can be broadly divided into two categories. One is the inherent noise generated within an LDO, which includes:

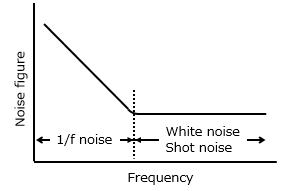

- 1/f noise:

Also called flicker noise or pink noise, 1/f noise is considered to be caused by defects on the semiconductor surface, etc. It is called 1/f noise because the noise level is inversely proportional to frequency.

- Popcorn noise:

Also called burst noise, popcorn noise is considered to be caused by lattice defects in semiconductor, etc. It is called popcorn noise because it produces an acoustic noise that sounds like popping popcorn when it enters an audio speaker. Popcorn noise has considerable adverse effects on applications that are very sensitive to noise such as CMOS sensors.

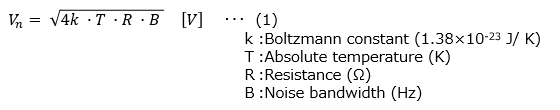

- White noise:

Also called thermal noise, white noise is caused by the thermal motion of electrons. It is not dependent on frequency. The white noise voltage is expressed as:

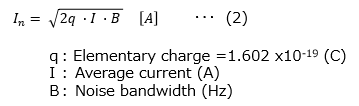

- Shot noise:

Shot noise occurs whenever carriers cross the potential barrier of a p-n junction. It is generated because the resulting current flow is discontinuous. As is the case with white noise, shot noise is not dependent on frequency, and is expressed as:

The other type of noise source is the ripple noise superimposed on the input voltage (supply voltage) of an LDO. Although an LDO internally suppresses ripple noise, some ripple still appears at the output. The ability of an LDO to suppress ripple in the input voltage to its output is called the power supply rejection ratio (PSRR) or the ripple rejection ratio (R.R.). Regarding ripple rejection ratio, also see the section “How can a low-noise power supply be created using an LDO regulator?” in the Frequently Asked Questions (FAQs) page on our website.

相關信息

The following documents also contain related information.