- 半導體首頁

-

應用Automotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

產品車用元件

Discrete Semiconductor

Diodes

電晶體

通用邏輯IC

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

功率半導體※

: Products list (parametric search)

隔離器/固態繼電器Photocouplers

Digital Isolators

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTs雙極性電晶體※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

微控制器馬達驅動 ICs智能功率 ICs※

: Products list (parametric search)

電源管理 ICs線性 ICs※

: Products list (parametric search)

通用邏輯 ICs線性影像感測器其他產品其他產品

※

: Products list (parametric search)

-

開發/設計支援

開發 / 設計支援

-

技術知識

- 購買管道

- 型號 & 關鍵字搜尋

- 交叉搜尋

- 參數搜尋

- 線上庫存查詢跟購買

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

型號需要超過三個文字以上 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

型號需要超過三個文字以上

使用分立半導體裝置進行設計時的熱管理

在設計中,有多種行之有效的方法可以應對目前分立半導體裝置的高溫問題。模擬技術對於衡量每種方法的效果至關重要。本文將介紹我們的熱模擬結果。希望這份文件能幫助您在設計過程中最大程度地減少發熱的問題。

簡介

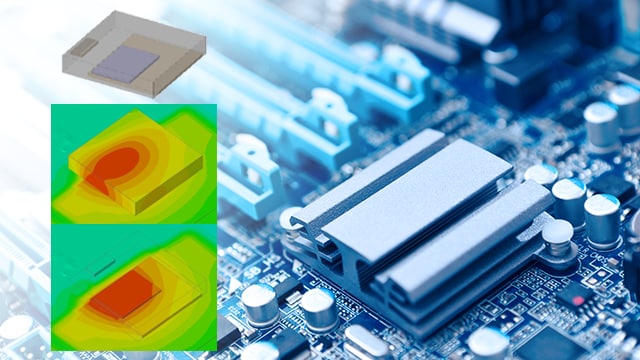

半導體晶片的溫度呈上升趨勢並不奇怪。這種熱量可能會對性能和功能性造成嚴重影響。例如,圖1說明為達到最佳熱性能,對錶貼封裝需求的不斷增加。

雖然有多種熱設計方法可以支援散熱,但哪種方法最為有效呢?

分立半導體裝置溫度上升的趨勢有幾個原因。其中一個原因是,電子產品尺寸減少導致自身散熱減少。另一個原因是,高密度電路板組件導致環境工作溫度升高。此外,在努力提高工作速度的同時,發熱量也在增加。

第1章:減輕發熱問題的設計對策

有多種方法可以緩解發熱問題。例如,多層電路板會影響電子元件的熱設計,因為產生的大部分熱量會透過熱傳導散佈到電路板的頂部和底部表面以及內部結構中。增加層數是增加功率耗散的有效方法。然而,這種方法主要對於4至8層電路板有效,並且會影響成本。

散熱器直接安裝在電路板上是一種對電路板組件進行散熱的方法。然而,散熱量的大小與散熱器的尺寸和散熱器的輻射率直接相關。

雖然增加散熱器的尺寸看起來是一種非常有效的散熱方法,但必須在尺寸與有限的成本之間進行平衡。採取增強散熱器輻射率的措施,例如陽極氧化鋁的表面處理,也是相當有效的,但受成本限制。

參考連結:

分立半導體裝置熱設計的提示與技巧 (PDF:1.4MB)

第2章:銅線層、 TIM和通孔

銅線層的使用顯著增加了電路板的熱導率。此外,增加銅線的厚度進一步增加了可以有效散熱的表面積,從而增強了電路板的整體熱導率。

當多個發熱元件排成一排時,熱幹擾特別明顯。如果裝置之間的距離太近,發熱問題會更加棘手。雖然增加裝置之間的距離會有所幫助,但在一定距離之後就不會再有更多的幫助了。另一個因素是導熱界面材料( TIM )。使用較薄的TIM有助於更有效地散熱,但對於較小的表面積,使用TIM會更具挑戰性。

通孔是用來建立印刷電路板各層之間電氣連接的孔。位於漏極走線架正下方的通孔可非常有效地散熱。同時,外圍通孔雖然效率不高,但在防止熱傳導到周圍區域方面效果良好。

第3章:模擬不同方法的效果

上述方法對於解決發熱問題的效果並不相同,它們的效果可能會根據設計條件而有明顯的變化。因此,我們進行了模擬,以評估每種熱設計方法的效果,並確定哪些參數能夠產生最佳結果。

有關模型和模擬的詳細資訊請參閱應用說明「分立半導體裝置熱設計的提示和技巧-第2部分」 。請注意,這些模擬的一個最大優勢是能夠使用在物理測量中無法實現的模型和條件。

此熱設計評估的裝置模型如下圖2所示,採用了SOP Advance 、 TSON Advance和DSOP Advance晶片封裝。

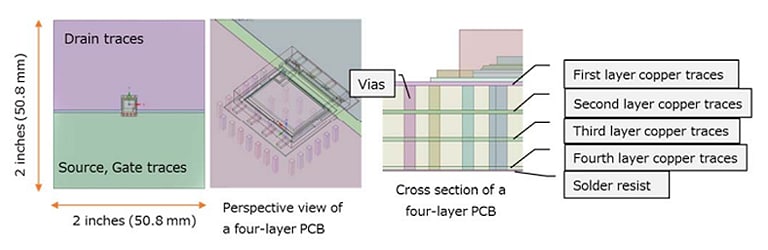

以2吋方形對電路板進行建模,只有背面的阻焊層被建模。正面的阻焊層則是透過增加板材的輻射率(例如,玻璃環氧樹脂FR4 )來進行模擬。選擇這種方法是為了在減少表面網格密度的同時,保持與阻焊層相同的效果。

此電路板的厚度大約是1.6mm ,基於最常用的電路板。模擬中使用的標準電路板以四層建模,使用銅作為走線材料,所有銅線的厚度設定為70μm進行評估。

參考連結:

分立半導體裝置熱設計的提示與技巧-第2部分 (PDF:1.1MB)

第4章:通孔與散熱器建模

將通孔建模為熱通孔, 0.25mm正方形,並設定在作為封裝主要熱路徑的汲極線上。將設置在銅線正下方的通孔建模為內通孔;將週邊的通孔建模為外通孔。在所有模擬中,除非已參數化,否則都會使用相同形狀的散熱器,並使用長方體進行建模。

在熱幹擾模型中,將三個裝置範例設定在共同的汲極線上,並使用與前述單一裝置模擬相同尺寸的線路板。

在所有模型中, TIM的物理屬性值相同,且只有其厚度上有通孔。 TIM的效果透過將其設置在( 1 )銅線和裝置之間以及( 2 )銅線和散熱器之間進行評估。

第5章:模擬結果

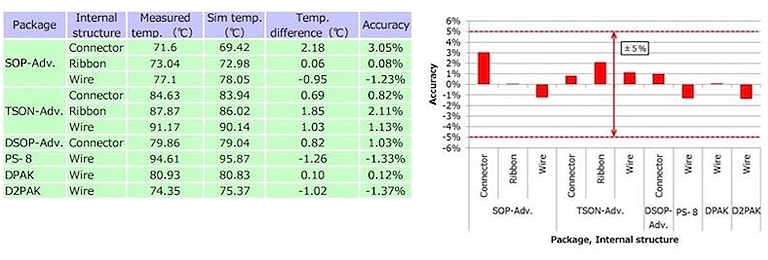

如圖3所示,模擬精度在±5%的可接受範圍內。

5-1 :多層PCB

圖4說明了多層PCB的效果。模擬結果顯示,當電路板層數從4層增加到8層時,晶片溫度降低了7% 。主要問題在於成本增加。

5-2 : PCB走線厚度

將走線厚度從70μm增加到105μm ,晶片溫度降低6%

5-3 :散熱器尺寸

在無散熱器的設計中,增加1cm高的散熱器可使晶片溫度降低12% 。當對高度為2cm的散熱器進行建模時,板溫降低了19% 。這種特定的方法比僅依賴電路板來散熱要有效得多。

5-4 :散熱器輻射率

透過使用陽極氧化鋁處理表面,可使散熱器的輻射率從0.04增加到0.8 。使用這種散熱器時,晶片溫度降低了12% 。雖然它非常有效,但這種表面處理會顯著影響成本。

5-5 :熱干擾

當連續三個裝置時, 3mm間距導致晶片溫度上升3% ;然而,當間距為12mm時,溫度並沒有上升。

5-6: TIM

當表面積較小時,使用較薄的TIM有助於散熱;然而,當表面積較大時,就不一定了。

5-7 :通孔位於汲極走線架正下方

將通孔設置在漏極走線架正下方,與沒有通孔的PCB相比,散熱效果非常顯著。增加三個通孔時,晶片溫度降低了9% ,增加五個通孔時,溫度降低了12% 。

5-8 :外圍通孔

與沒有通孔的電路板相比,增加六個通孔使晶片溫度降低了7% ,而增加十個通孔使溫度降低了10% 。值得注意的是,週邊通孔的效果不如設置在漏極走線架正下方的通孔。另一方面,外圍通孔的使用確實很有好處:它們可以防止熱量傳導到周圍區域。

第6章:東芝半導體解決方案

並不是所有的標貼封裝都具有相同的熱設計和性能,因此我們一直在積極研發在封裝中提供卓越熱性能的解決方案,包括MOSFET封裝、 SOP Advance封裝以及在模擬中使用的TO - 247封裝。

我們的半導體元件具有最先進的封裝技術,採用的便是上述經過驗證的方法。此外,我們還提供一個簡化3D模型(簡化CFD模型),該模型適用於熱模擬,主要針對MOSFET ,以幫助您更好地了解設計的溫度分佈,並找到有效的降低溫度的方法。

參考連結 :

下載PDF文件

請點選按鈕下載PDF檔案。

相關連結

請參考下面的PDF文件以了解更多關於熱設計的資訊。