-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

はじめに

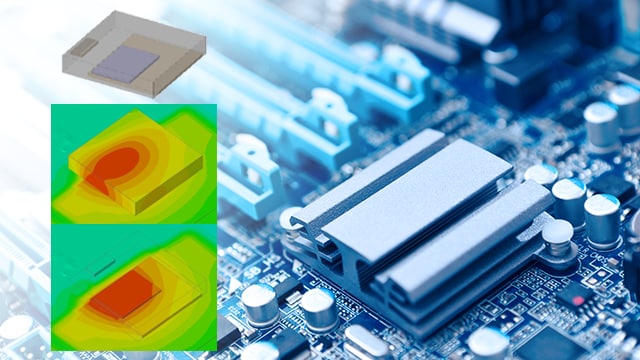

半導体チップの温度が上昇する傾向にあるのは当然のことです。その熱は、性能や機能性に深刻な問題を引き起こす可能性があります。例えば、図1は、最適な熱性能を発揮する表面実装パッケージの必要性が高まっていることを示しています。

放熱をサポートするさまざまな熱設計アプローチがありますが、さてどれが最も効果的なのでしょうか。

ディスクリート半導体デバイスの温度が上昇傾向にある背景には、いくつかの原因があります。ひとつは、電子機器の小型化による自己放熱の減少であり、もうひとつは、高密度基板実装にともなう周囲動作温度の上昇です。さらに、動作の高速化にともなって熱発生も増加しています。

第1章: 熱問題を軽減する設計対策

熱問題を軽減する方法はいくつかあります。例えば、多層PCBは電子機器の熱設計に影響を与えます。なぜなら、発生する熱のほとんどは、熱伝導によってPCBの上面と下面、そして内部に分散されるからです。層数を増やすことは、電力放散を増加させる方法として実証されています。ただし、これは主に4~8層を使用した場合に効果があり、しかもコストに影響します。

PCBに直接取り付けられた放熱器は、PCB上の部品から発生する熱を放散させるひとつの方法です。しかし、放熱量は放熱器のサイズと放熱器の放射率に直接関係しています。

放熱器のサイズを大きくすることは、放熱には非常に効果的なアプローチに思えますが、サイズとコスト制約とのバランスを取る必要があります。また、アルマイト表面処理など、放熱器の放射率を高めるための対策も大変効果的ですが、やはりコスト制約が付いてきます。

参照リンク:

ディスクリート半導体熱設計の勘どころ (PDF:1.6MB)

第2章: 銅パターン層、TIM、ビア

銅パターン層を使うことで、基板自体の熱伝導率が大幅に高まります。さらに、銅パターン厚を増やすと熱が効果的に放散される表面積がさらに増えるため、基板全体の熱伝導率が高まります。

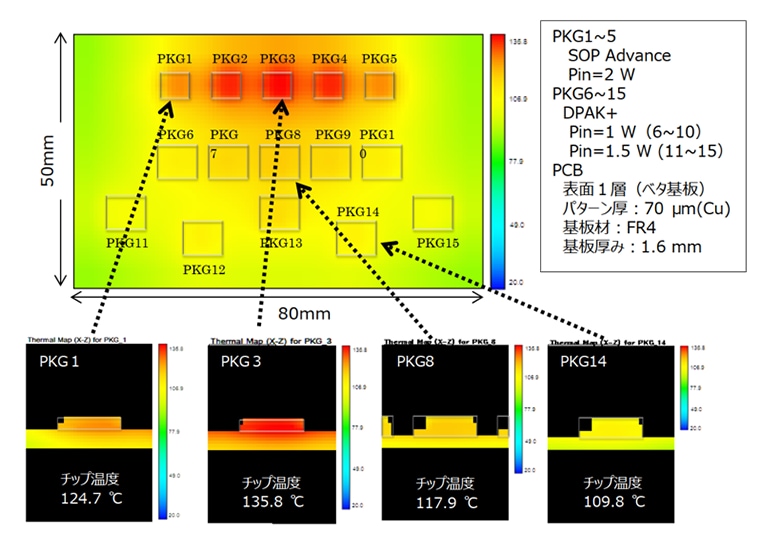

熱干渉は、複数の発熱デバイスを配置した場合に特に顕著になります。デバイスが近すぎると、発熱がより問題となります。また、デバイスの間隔を離すことは一助にはなりますが、それ以上の効果が得られない距離もあります。もうひとつの要因はTIM (Thermal Interface Material: 熱伝導材料) です。薄いTIMの使用はより効果的な放熱の一助にはなりますが、小さい面積にTIMを使用する場合は、最適化は困難です。

ビアは、プリント回路基板の層間の電気的接続を確立するためにプリント回路基板に設けられた穴です。ドレインフレーム直下のビアは放熱効果が高いです。一方、周辺のビアは、放熱効率は劣りますが、周囲への熱伝導を防ぐ効果があります。

第3章: さまざまなアプローチの効果をシミュレーションする

発熱問題への対処は、上記の方法がすべて同じというわけではなく、設計条件によって効果が大きく異なる場合があります。そのため、当社ではシミュレーションを行い、それぞれの熱設計手法がどの程度有効で、どのようなパラメータが最良の結果をもたらすかを評価しました。

モデルとシミュレーションの詳細については、アプリケーションノート「ディスクリート半導体熱設計の勘どころ 2」をご参照ください。これらのシミュレーションの最も強力な利点の1つは、物理的な測定では実現不可能なモデルと条件を使用できることです。

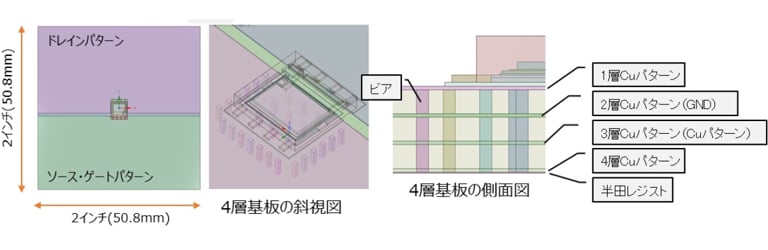

この熱設計評価用のデバイスモデルは以下の図2に示すもので、当社のSOP Advance、TSON Advance、DSOP Advanceのチップパッケージを使用しています。

PCBは2インチ角でモデル化し、裏面の半田レジストのみをモデル化しました。表側に存在する半田レジストは、基板材料 (たとえばガラスエポキシFR4) の放射率を上げることでシミュレーションしました。この方法は、半田レジストと同じ効果を維持しながら表面メッシュの密度を下げることを意図して選択されました。

このPCBの厚さは、最も一般的に使用されている約1.6mmとしました。シミュレーションに使用される標準PCBは、4層でモデル化、パターン材料には銅が使用され、また銅パターン厚はいずれも70μmに設定されています。

参照リンク:

ディスクリート半導体熱設計の勘どころ 2 (PDF:1.5MB)

第4章: ビアと放熱器のモデリング

ビアは0.25mm角のサーマルスルーホールとしてモデル化され、パッケージ内の主要な熱経路となるドレインパターン上に配置しました。銅パターンの直下に配置されたビアはインナービアとしてモデル化され、一方、周辺部のビアはアウタービアとして使用されました。放熱器は、特にパラメータ化された場合を除き、すべてのシミュレーションにおいて同形状の直方体でモデル化されたものが使用されました。

熱干渉モデルでは、3つのデバイスを共通のドレインパターン上に配置し、前述の単一デバイスのシミュレーションと同じサイズのプリント基板が使用されました。

すべてのモデルで、TIM には同じ物性値を使用し、厚みはビアのみとしました。TIMの効果は、(1) 銅パターンとデバイスの間、および (2) 銅パターンと放熱器の間に配置して評価しました。

第5章: シミュレーション結果

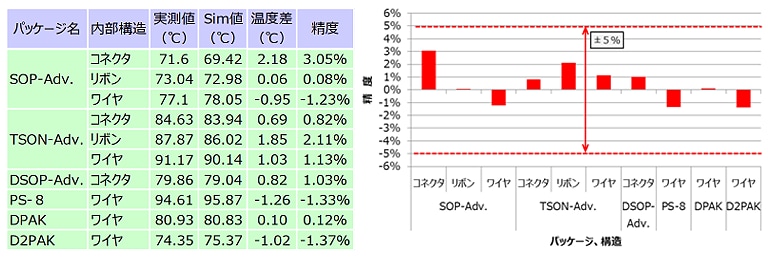

図3に示すように、シミュレーションの精度は±5%の許容範囲内であることが分かりました。

5-1: 多層PCB

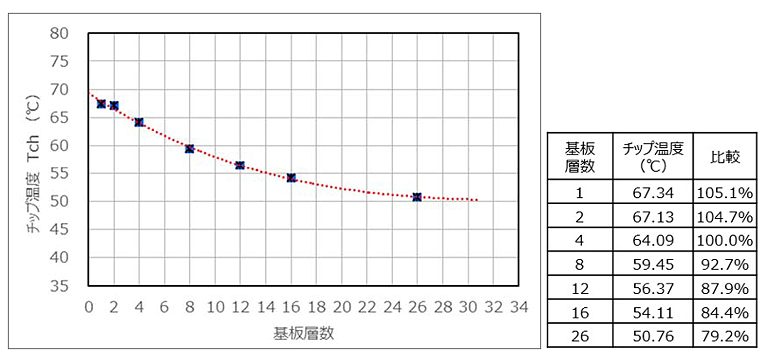

多層PCBの効果を図4に示します。シミュレーションの結果、PCBの層数を4層から8層に増やすと、チップ温度が7%低下することが分かりました。ここでの主な問題はコストの増加です。

5-2: PCBパターン厚

パターン厚を70μmから105μmにすることで、チップ温度は6%低下しました。

5-3: 放熱器サイズ

放熱器なしの設計では、高さ1cmの放熱器を追加することでチップ温度が12%低下しました。高さ2cmの放熱器をモデル化した場合、基板温度は19%低下しました。この特別なアプローチは、放熱をPCBだけに依存するよりもはるかに効果的です。

5-4: 放熱器の放射率

放熱器の放射率は、表面をアルマイト処理することで0.04から0.8に高めることができます。このような放熱器を導入した場合、チップ温度が12%低下しました。非常に効果的ですが、この表面処理はコストに大きく影響します。

5-5: 熱干渉

3つのデバイスを並べた場合、3mmの間隔ではチップ温度が3%上昇しましたが、12mmの間隔では温度上昇は見られませんでした。

5-6: TIM

表面積が小さい場合は、より薄いTIMの使用で効果がありますが、表面積が大きい場合はあてはまりません。

5-7: ドレインフレーム直下のビア

ドレインフレーム直下にビアを配置すると、ビアのないプリント基板と比較してかなり効果的であることが立証されました。ビアを3つ追加した場合はチップ温度が9%低下し、5つ追加した場合は12%低下しました。

5-8: 周辺ビア

ビアのないプリント基板と比較した場合、ビアを6本追加するとチップ温度は7%低下し、10本追加すると10%低下しました。しかし、周辺ビアは、ドレインフレーム直下に配置されたビアよりも効果が低かったことは注目に値します。一方で、周辺ビアには、周囲への熱伝導を防ぐという優れた利点があります。

第6章: 東芝デバイス&ストレージソリューション

表面実装パッケージは、熱設計と性能に関してすべてが同じというわけではありません。したがって当社では、本シミュレーションで使用したパッケージ (MOSFET、SOP Advance、TO-247) のような、優れた熱性能を提供するソリューションの開発を積極的に進めてきました。

当社では、ここまで述べてきたような実証済みの手法を取り入れた最先端パッケージの半導体部品を取り揃えています。また、当社はMOSFETを中心に熱シミュレーションに適した簡略化した3Dモデル (簡易CFDモデル) を公開しております。

参照リンク:

PDFをダウンロード

以下ボタンから本記事をPDFでダウンロードできます。

関連リンク

熱設計について、もっと詳しくお知りになりたい方は以下PDF記事をご覧ください。