- 半導體首頁

-

應用Automotive

Body Electronics

xEV

In-Vehicle Infotainment

Advanced Driver-Assistance Systems (ADAS)

Chassis

IndustrialInfrastructure

BEMS/HEMS

Factory Automation

Commercial Equipment

Consumer/PersonalIoT Equipment

Healthcare

Wearable Device

Mobile

Computer Peripherals

-

產品車用元件

Discrete Semiconductor

Diodes

電晶體

通用邏輯IC

Analog Devices

Digital Devices

Wireless Devices

※

: Products list (parametric search)

功率半導體※

: Products list (parametric search)

隔離器/固態繼電器Photocouplers

Digital Isolators

※

: Products list (parametric search)

MOSFETsIGBTs/IEGTs雙極性電晶體※

: Products list (parametric search)

Diodes※

: Products list (parametric search)

微控制器馬達驅動 ICs智能功率 ICs※

: Products list (parametric search)

電源管理 ICs線性 ICs※

: Products list (parametric search)

通用邏輯 ICs線性影像感測器其他產品其他產品

※

: Products list (parametric search)

-

開發/設計支援

開發 / 設計支援

-

技術知識

- 購買管道

- 型號 & 關鍵字搜尋

- 交叉搜尋

- 參數搜尋

- 線上庫存查詢跟購買

This webpage doesn't work with Internet Explorer. Please use the latest version of Google Chrome, Microsoft Edge, Mozilla Firefox or Safari.

型號需要超過三個文字以上 Search for multiple part numbers fromhere.

The information presented in this cross reference is based on TOSHIBA's selection criteria and should be treated as a suggestion only. Please carefully review the latest versions of all relevant information on the TOSHIBA products, including without limitation data sheets and validate all operating parameters of the TOSHIBA products to ensure that the suggested TOSHIBA products are truly compatible with your design and application.Please note that this cross reference is based on TOSHIBA's estimate of compatibility with other manufacturers' products, based on other manufacturers' published data, at the time the data was collected.TOSHIBA is not responsible for any incorrect or incomplete information. Information is subject to change at any time without notice.

型號需要超過三個文字以上

Calculating the Operating Supply Current and Power Dissipation

Calculating the power dissipation of a CMOS logic IC

Power dissipation should be calculated from both of the following:

- Static supply current

- Dynamic supply current

Power can be obtained by multiplying current by the voltage applied to an IC.

Static power dissipation: PS

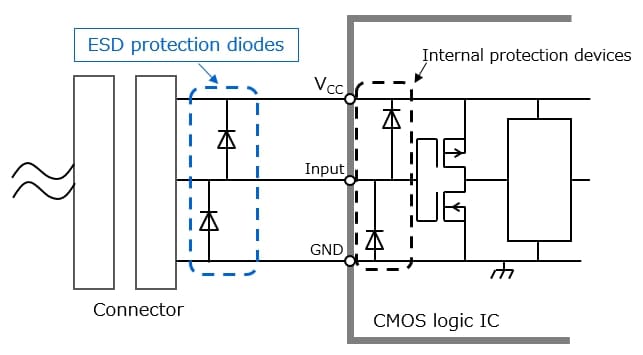

While CMOS logic is in a static state (i.e., while its input voltage remains almost unchanged), little current flows in it except tiny leakage current that flows across the internal reverse-biased pn junction (known as static supply current, ICC). Static power dissipation is ICC multiplied by the supply voltage.

PS = VCC x ICC

VCC: Voltage applied to a logic IC

ICC: Static supply current shown in the datasheet

Dynamic power dissipation: PL+PPD

Dynamic supply current is the current that flows in CMOS logic ICs while its input transitions between High and Low. This current flows during the charging and discharging of capacitance. It is necessary to consider both parasitic capacitance (internal equivalent capacitance) and load capacitance.

Dynamic power dissipation is dynamic supply current multiplied by the voltage applied to the p-channel or n-channel MOSFET.

For the sake of simplicity, the following calculation assumes that this voltage is equal to VCC at which dynamic supply current becomes the maximum.

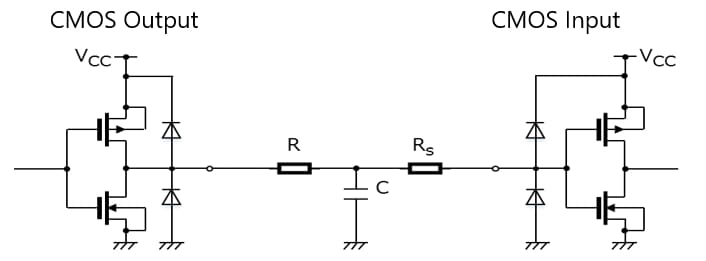

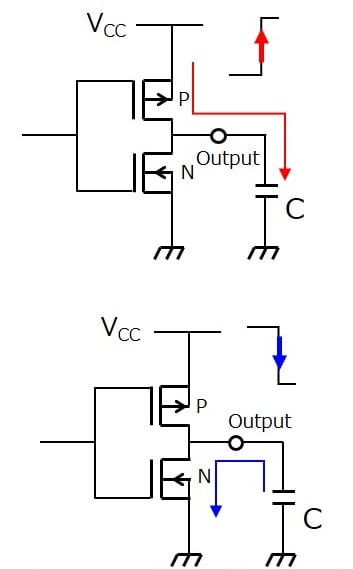

Dynamic power dissipation due to load capacitance (CL): PL

PL means power dissipation when an external load is charged and discharged as shown by the right-hand figure.

The amount of charge (QL) stored on the load capacitance is calculated as follows:

QL = CL * VCC

CL: Load capacitance

Let the output signal frequency be fOUT (= 1/TOUT). Then, the average current (IL) is expressed as follows:

IL = QL / T = CL * VCC * fOUT

Hence, dynamic power dissipation (PL) is:

PL = VCC * IL = CL * VCC^2 * fOUT

If an IC has multiple outputs, its dynamic power dissipation can be calculated as follows:

PL = VCC^2 * Σ (CLn* fOUTn)

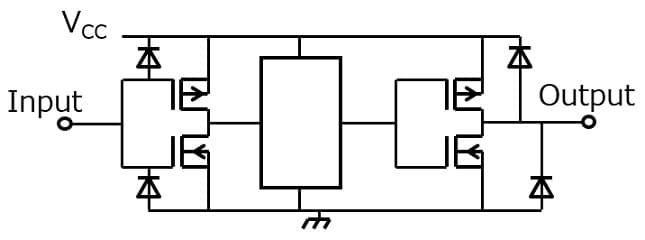

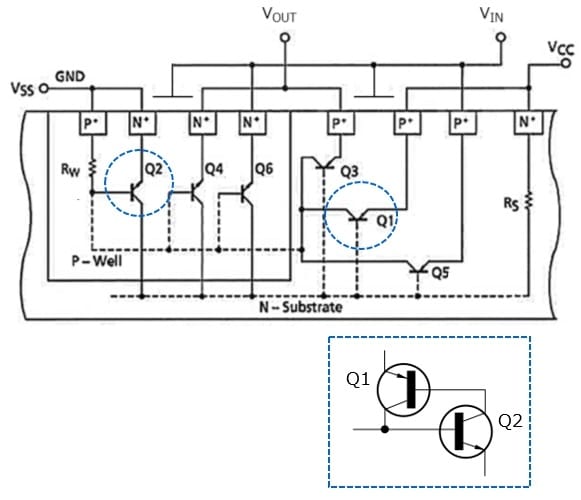

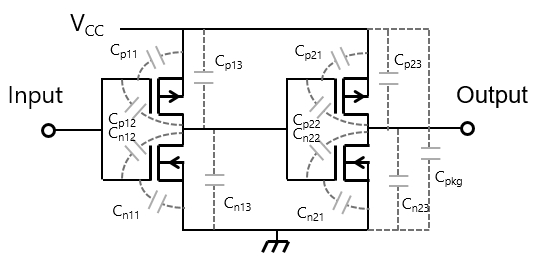

Dynamic power dissipation due to internal equivalent capacitance (CPD): PPD

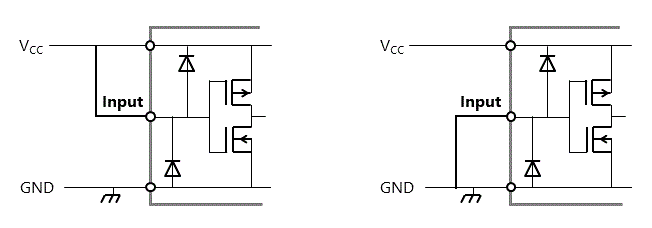

CMOS logic ICs have various parasitic capacitances as shown by the right-hand figure. These capacitances are equivalently expressed as CPD. (Actually, CPD is calculated from power dissipation at relatively high frequency (1 MHz) under a zero-load condition.)

PPD is the power dissipated by the equivalent capacitance of an IC and can be considered in the same manner as PL.

Note, however, that PPD is calculated at input frequency (fIN):

PPD = VCC * IL = CPD * VCC^2 * fIN

Total power dissipation (PTTL) can be obtained as the sum of static power dissipation (PS) and dynamic power dissipation (PL + PPD):

PTTL= PS + PL + PPD

CMOS邏輯IC的使用注意事項

Products

Related information

- Application Notes

- FAQ