-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

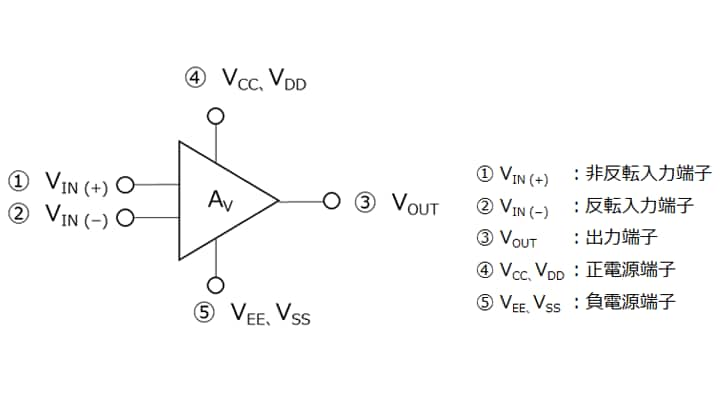

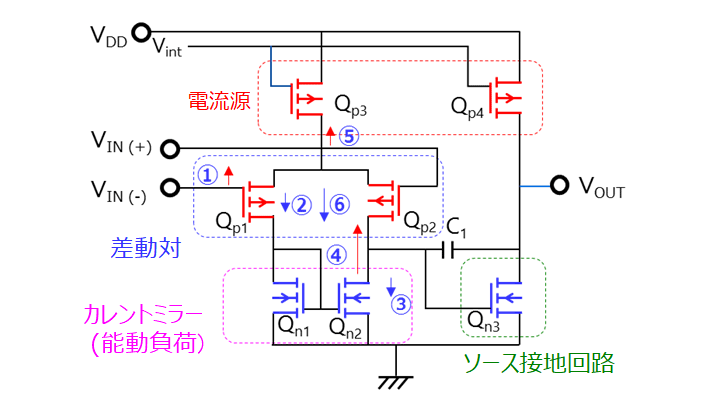

1-3. オペアンプの内部動作

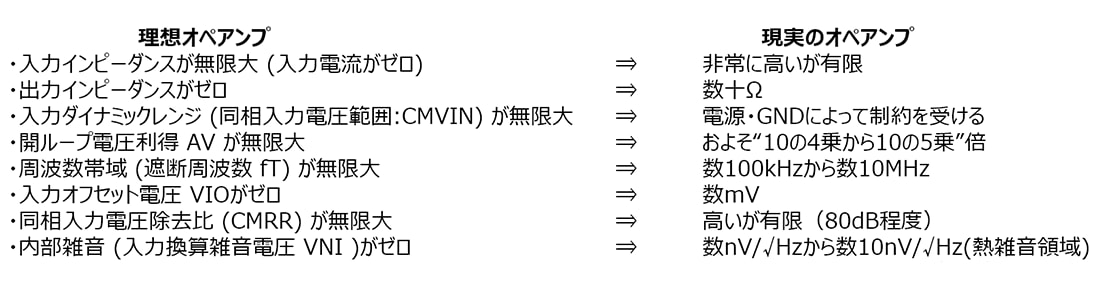

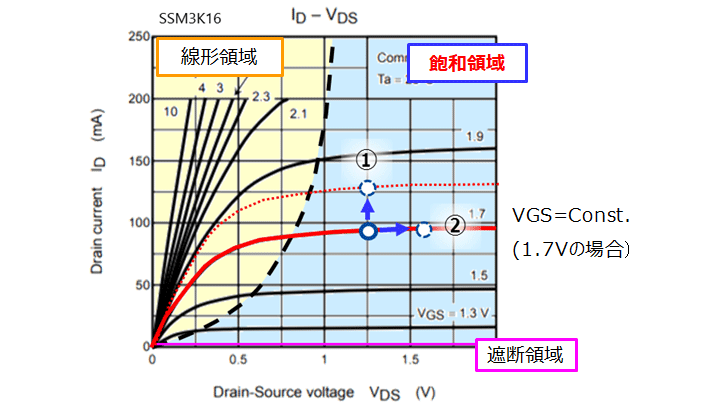

CMOSオペアンプがオペアンプとして正常に動作するためには、オペアンプ簡易等価回路(図 1-2)を構成するMOSFETが飽和領域で動作する必要があります。飽和領域は図 1-3に示す範囲になります。

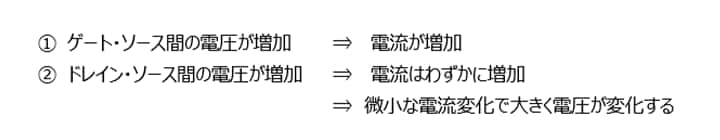

飽和領域でMOSFETは以下のように動作します。

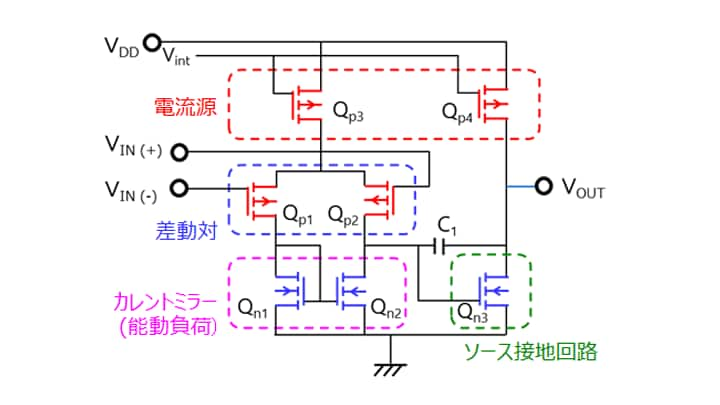

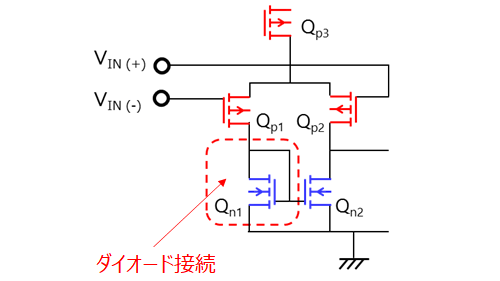

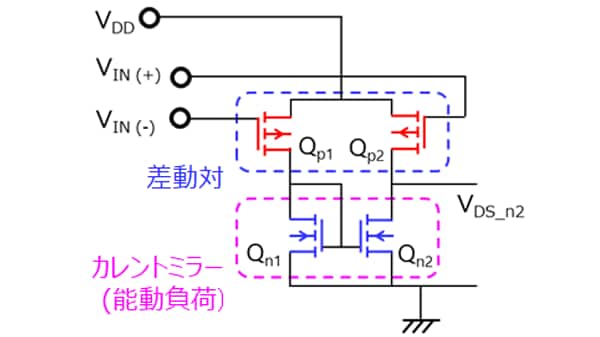

オペアンプ簡易等価回路の各部の働きは以下のようになります。オペアンプ簡易等価回路の各部の働きは以下のようになります。

- 差動対:VIN(+)端子VIN(-)端子に加えられたそれぞれの入力電圧の差分を取り出し増幅します。

- カレントミラー:差動対を構成しているQp1とQp2に等しい電流を流します。このカレントミラーは差動対から見ると負荷抵抗として働きます。カレントミラーの出力(差動対から見たドレイン端子)は通常の抵抗では構成するのが困難なハイインピーダンスとなっています。これにより初段の差動アンプは高い利得を実現できます。このようなトランジスタなどで構成する抵抗負荷を能動負荷と呼びます。

- 電流源:差動対とソース接地増幅回路の電流を決めます。ソース接地回路に対しては能動負荷として働きます。

- ソース接地回路:出力に外付けされる負荷の駆動電流を確保するとともに、初段の差動増幅回路の利得を補います。

具体的な動作の前に、カレントミラー回路のQn1のドレイン電圧について簡単に述べます。

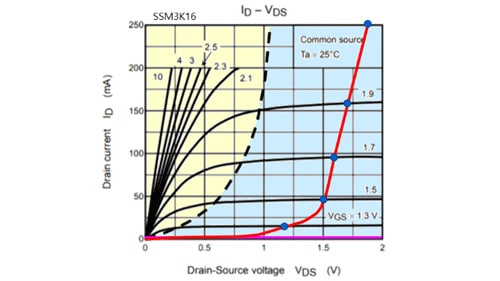

Qn1ドレイン・ソース間電圧VDS_n1とドレイン・ゲート間電圧VDG_n1は等しくなっています。このVDS = VDGの条件をMOSFET ID-VDSカーブに書き込むと図 1-4のような曲線になります。この曲線はダイオードのIF-VF曲線に似ているのでダイオード接続と呼ばれます。図 1-4はディスクリートのNch-MOSFETの曲線なのでチャネル面積が広く、電流が大きくなっていますが、IC内で使用されるMOSFETの場合は電流が2桁~3桁小さな電流になります。

図を見てわかるように、電流の大きな十分に立ち上がった部分(VDS = 1.5V以上)では、電流の変化が小さければ電圧はほとんど動きません。具体的な動作の前に、カレントミラー回路のQn1のドレイン電圧について簡単に述べます。

更に、上部の電流源の働きに関して考えてみます。差動回路部分に電流源が無い状態の図 1-6の回路を考えます。後段のソース接地回路は変わらないとします。

差動対のVIN(+)端子とVIN(-)端子に同じ電圧 (VDD – VIN) が加えられています。従って、VSG = VIN となります。この時のQp1のドレイン電圧は、ドレイン電流ID_p1を流した時に、VSD_p1+VDS_n1=VDDとなる電圧に落ち着きます。このID_p1がカレントミラー回路でコピーされるので、Qp2とQn1で構成される回路も同じ電圧関係になります。

仮にこの両端子に加えられた入力電圧がΔV上昇した電圧 (VDD – VIN + ΔV) になったとします。この回路にはカレントミラーがあり差動対には同じ電流は流れます。ただし上部の電流源は無いので差動対に流れる電流はそれぞれ同じだけ減少します。このためソース接地回路に出力されるQn2のドレイン・ソース間電圧も下がることになります。

これはソース接地回路のQn3のゲート・ソース電圧VGS_n3が下がることと等価です。このソース接地回路には電流源Qp4があるので、VGS_n3が下がり電流が減少しようとする分、ドレイン・ソース間電圧VDS_n3を広げ電流を一定に保ちます。つまり出力電圧VOUTは上昇することになります。VIN(+)とVIN(-)に入力される電圧が同相で同じ電圧の入力であるにも関わらず、出力電圧が変化することになります。オペアンプは規格内の同相入力(同じ入力電圧)が印加された場合、出力は一定であることが必須条件です。この回路ではこの条件を満たせないことがわかります。

次に図 1-2の電流源Qp3のある回路で同じことを考えてみます。仮にこの両端子に加えられた入力電圧がΔV上昇した電圧 (VDD – VIN + ΔV) になったとします。この回路には電流源がありますので、電流は変わりません。電流が変わらないので、Qn1のVDS_n3は変化しません。同様にVDS_n2も変わらないので、出力は一定になります。同相入力では出力が一定になることがわかります。

(ΔVの変化はQp3のVSD_p3が変化し吸収します。電流源のソース・ドレイン間電圧が変わりますので、電流は変化しますが、図 1-3に記したようにVDSの増減に対する電流IDの変化は微小なので大きくは変化しません。)

このように差動対の上部にある電流源が同相入力時の出力電圧を一定化する役割を果たしています。

次に差動対入力 VIN(+)端子とVIN(-)端子に異なる電圧が加えられた時を考えます。

- 差動対の両端の入力に同じ電圧 (VDD – VIN) が加えられている状態から、VIN(-)側だけ+ΔV電圧が上がったとします。

- VSG_p1は小さくなり、ID_p1はΔIp1減少します。ただし、先に説明しましたが、Qn1はダイオード接続されていますので、VDS_n1は変化せずQp1のドレイン電圧は一定です。

- この減少した電流はカレントミラーによりQn2のドレイン電流ID_n2にコピーされます。

- 電流源Qn3のドレイン電流ID_p3の電流は変わりませんのでこのままでは矛盾が生じてしまいます。このため、Qn2を流れる電流を増加するために、Qn2のドレイン電圧VDS_n2は大きくなります。

- VDS_n2が大きくなると、単純に考えるとVSD_p2は小さくなり、またID_p2も小さくなってしまいます。しかしながら、電流源電流ID_p3は変わっていません。ただでさえΔIp1減少しているので、むしろ増える必要があります。このため、Qp2のソース電圧は上昇します。

- Qp1のソース・ゲートの電位差VSG_p1が広がり、Qp1のドレイン電流ID_p1が大きくなります。

- この電流がQn2にコピーされ・・・・・

このような動作をすることで最終的に、Qn2のドレイン電圧VD_n2は、初期状態から上昇することになります。

この上昇した電圧が次段のソース接地回路に伝達されることになります。

ソース接地回路ではVGS_n3が大きくなり、電流ID_n3が増大する方向に進みますが、こちらも電流源Qp4により制約を受けます。VGS_n3が増大して、電流ID_n3が増加しないために、Qn3のドレイン・ソース電圧VDS_n3は減少します。

このようにしてVIN(-)の電圧が上昇すると、VOUTの電圧は減少することになります。

関連情報

関連情報

- 製品ページ

- アプリケーションノート

- オペアンプFAQ

- オペアンプのパラメトリックサーチはこちら

- オペアンプの購入はこちら