-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

負荷が重くて、VCE(sat)が設計値まで下がりません。何を考えたらよいですか?

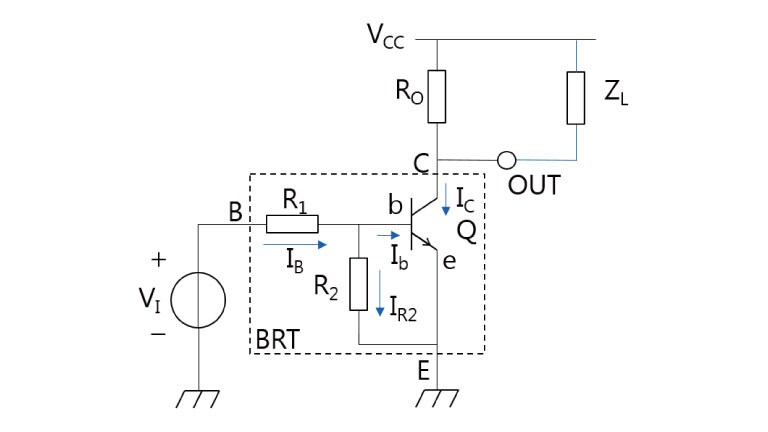

図-1 に簡単なBRT動作回路図を示します。BRTのプルアップ抵抗としてRO、負荷のインピーダンスをZLとして記載しています。ここでは簡単のため、ZLを実数のみのインピーダンス(抵抗)として考えます。

ZLを接続したときに、 Qがオンしているときのコレクタ・エミッタ間電圧は次段の回路で必要な“L”電圧を満足する必要があります。

まずZLの無い回路を考えます。

ZLの無いとき、コレクタ電流 ICと内蔵トランジスタ Qのコレクタ・エミッタ間飽和電圧(VCE(sat))は

VCE(sat) ≒ RO * IC

次にZLを接続したときBRTのコレクタから見た合成インピーダンス Zは以下になります。

Z = RO // ZL = RO * ZL / ( RO + ZL )

この合成インピーダンスZによるコレクタ・エミッタ間電圧 VCEは下記になります。

VCE = Z * IC

このVCEが次段の回路の“L”電圧を満足していれば問題はありませんが、要求よりも高くなってしまったときはコレクタ電流を増やすために内蔵トランジスタのベース電流 Ibを増やす必要があります。

Ibを増やす方法としては、以下の方法があります。

1. 入力電圧VIを高くする

2. R1の抵抗値をより小さな抵抗値のBRTに変更する

3. R2の抵抗値をより大きな抵抗値のBRTに変更する