-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

ESD(Electrostatic Discharge)試験とはどのようなものですか?

ESD(Electrostatic Discharge)試験とは、半導体デバイスや電子機器が静電気放電(ESD)にさらされた際に、どの程度の耐性を持つかを評価する試験です。ESD試験は評価対象や目的の違いにより、デバイスレベル試験とシステムレベル試験に大別されます。

ESDについては、以下のFAQに説明があります。

> 静電気放電(ESD : Electrostatic Discharge)とは何ですか?

デバイスレベル試験

デバイスレベル試験は、ICやディスクリート部品などの半導体デバイス単体を対象としたESD試験です。

製造、実装、ハンドリングなどの工程で想定される静電気放電に対して、デバイスが劣化や破壊を起こさないことを確認する目的で実施されます。

デバイスレベルESD試験の主な目的は、被試験デバイス(DUT)が半導体の製造・実装工程で想定されるESDストレスによって劣化または破壊されるかどうかを評価することです。

このため、評価結果は基本的に破壊の有無によるPass / Fail(Go / No-Go)判定となります。

代表的なデバイスレベルESD試験には以下があります。

- Human Body Model(HBM)

人体が静電気を帯びた状態で、ICや部品に触れた瞬間に放電する状態を想定した試験 - Machine Model(MM)

半導体製造装置や金属治具などが帯電し、低インピーダンスでデバイスに放電する状態を想定した試験 - Charged Device Model(CDM)

デバイス自身が帯電し、接地された金属などに触れた瞬間にデバイス自身が放電する状態を想定した試験

HBM/MMはコンデンサーにチャージした電荷を被測定素子に放電する試験、CDMはデバイスにチャージして放電する試験です。試験は原則としてデバイスの端子を対象に行われ、ESDに対する保護は各デバイスに内蔵されたESD保護回路によって担われます。

システムレベル試験

システムレベル試験は、電子機器や装置を実使用状態に近い形で評価するESD試験です。例えば、USB端子にケーブルを接続する、コネクターやタッチパネルに人が触れるといった、日常環境で想定されるESD事象を模擬します。

代表的な規格として IEC 61000-4-2 があり、コネクター、タッチセンサー、アンテナなど、外部に露出したI/O端子を主な試験対象とします。

システムレベルESD試験では、デバイスレベル試験と比較してより大きなピーク電流を伴うESD波形が印加されます。そのため、デバイスに内蔵されたESD保護回路だけでは十分な保護が難しく、外付けのESD保護ダイオード(TVSダイオード)などを併用した対策が一般的に行われます。

IEC 61000-4-2とESD保護ダイオードについては、以下のFAQに説明があります。

> IEC61000-4-5とは何ですか?

> 静電気保護用ダイオード(ESD保護ダイオード)とは何ですか?

システムレベル試験における評価の考え方

システムレベルESD試験では、単に機器が破壊されないことだけでなく、機能動作への影響も重要な評価対象となります。

具体的には、以下のような観点で評価が行われます。

- 試験中および試験後に正常動作を維持できるか

- 一時的な誤動作や機能低下が発生するか

- 誤動作が発生した場合に自動的に復帰するか

- リセット操作などの手動復帰が必要か

- 恒久的な故障や機能喪失が発生するか

このように、システムレベルESD試験では機器のイミュニティ(耐性)を段階的に評価する考え方が用いられ、必ずしも「破壊するか/しないか」のGo / No-Go判定だけで評価されるものではありません。

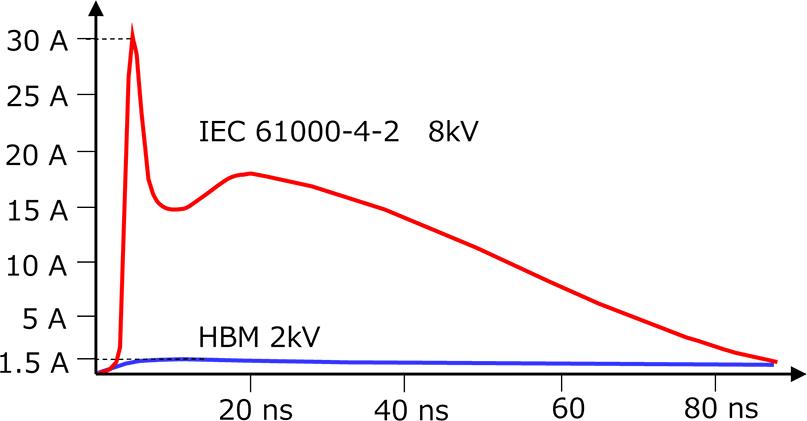

ESD試験波形とTLP測定について

図1は、デバイスレベル試験(HBM)とシステムレベル試験(IEC 61000-4-2)における試験波形の一例を比較したものです。試験条件(インピーダンスなど)が異なるため単純な比較はできませんが、システムレベル試験ではピーク電流が非常に大きいことが分かります。これは、システムレベル試験が一般使用環境で発生し得る制御の難しいESD事象を想定し、より厳しい条件を規定しているためです。

このように、デバイスレベル試験とシステムレベル試験ではESD波形や電流条件が大きく異なりますが、これらの規格試験は、規定された条件下においてデバイスや機器がESDストレスに耐えられるかを評価することを目的としています。

一方で、ESD保護設計においては、単なる合否判定だけでなく、ESDストレスが印加された際にデバイスやESD保護素子がどのような電圧・電流特性を示すかを把握することが重要になります。このようなことを背景に、近年ではICのI/O端子やESD保護素子に対して、ESDのような短パルスを印加した際の電気的特性をデータシートなどに提示する例が増えています。

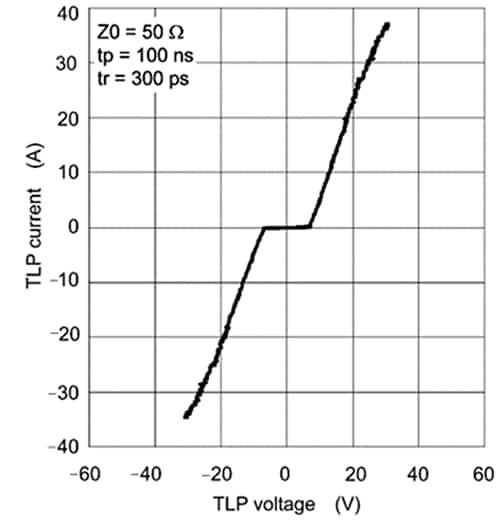

このような特性評価手法の一つが TLP(Transmission Line Pulse)測定です。

TLP測定は、素子のESDストレスに対する電気的耐性やクランプ特性を把握し、ESD保護設計(保護素子選定など)に活用するための評価手法であり、システムレベルESD試験そのものを代替するものではありませんが、設計段階での有効な指標となります。

当社のESD保護ダイオード製品においても製品やシリーズによっては、図2に示すTLP波形を参考値としてデータシートに掲載しています。

TLP試験については以下のFAQも参考にしてください。

> TLP試験とは

関連リンク

TVSダイオード (ESD保護用ダイオード) の製品ラインアップについては、以下のページ、ドキュメントをご参照ください。