-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

オペアンプの同相入力電圧 (CMVIN) とは

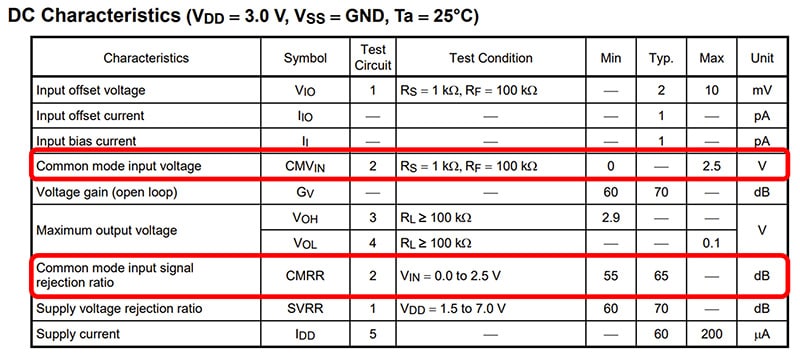

オペアンプ データシートの電気的特性には同相入力電圧 (Common mode input voltage : CMVIN) が定義されています。この項目はオペアンプのIN(+)端子とIN(-)端子に同じ信号を入力したときにデータシートの電気的特性 (CMRRなど) を満足する入力電圧です。

同相の信号を入力することは無いと考える方もいると思いますが、オペアンプは負帰還をかけて使用されることが多く、IN(+)とIN(-)の2つの入力端子は仮想短絡の考え方から同相 (または微弱な電位差を持つ信号) が入力されることと同等になります。

この同相入力電圧範囲を超えて入力を行うと、差動アンプのゲインが減少して信号が歪むことになります。更に大きな信号を入力すると、最大定格の差動入力電圧を超え劣化や素子の破壊につながります。

一般的なオペアンプの入力等価回路は差動対、電流源、カレントミラー (能動負荷) で構成されています。 (図-1参照) 基準バイアスVB1により設定された電流源により差動対に電流が流れ込む電流が決まります。カレントミラー回路があるので基本的にはQn1とQn2に同じ電流を流します。この電流がQn1とQn2に流れ、この電流に対応したVDS_qn2がIC内部出力段に伝達されます。

ここで入力電圧がそれぞれΔV下がったとします。Qp2とQp3のVSGが大きくなりドレイン電流は増加しようとします。電流源も電流を増加させるためにVDS_qp1が増加します。このため、Qp2とQp3のVSGが下がり増加前のVSGに戻る事になります。

このようにオペアンプは同相の信号が入力された場合に変化しないことになります。

ただし、この動作は全てのMOSFETが飽和領域で動作することが条件になります。

次にMOSFETが飽和で動作する条件を考えます。

図-2にNch MOSFET (SSM3K16) のID-VDSカーブを示します。飽和領域では“VDSが変化しても電流はほぼフラット (ΔV / ΔI = ハイインピーダンス) な特性を示します。飽和領域で動作するためには下記の条件を満たす必要があります。Vthはゲートに電圧を印加して電流が流れだすときのVGSになります。

VDS > VGS - Vth ・・・①

ここでGNDからVIN(+)の式を立てて同相入力電圧の最小値VIN(+)_minを考えます

VIN(+) = VGS_qn1 + VSD_qp2 – VSG_qp2 ・・・②

VIN(+)_minではQp2のソース電圧が下がりQp2が飽和領域と線形領域の切り替わる直前の状態 (ピンチオフ電圧) になっています。この電圧値をVSD_qp2_min とし、電流が流れ始めるQp2の閾値電圧をVth_qp2とすると、この電圧では飽和の条件①式から下式が成り立ちます。

VSD_qp2_min = VSG_qp2 – Vth_Qp2 ・・・③

②式に③式を代入して

VIN(+)_min = VGS_qn1 – Vth_qp2 ・・・④

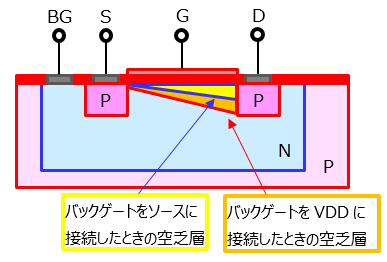

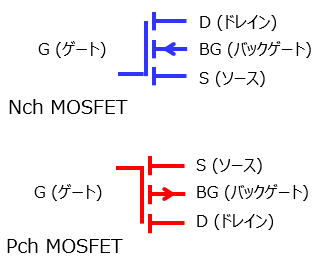

ここまでMOSFETは3端子として扱ってきましたが、図-3に示すように実際にはバックゲートと呼ばれる第4の端子があります。 (一般的なディスクリート素子ではバックゲートはソース端子と内部接続しています。)

この端子にPch MOSFETであればソースより高い電圧を印加することにより空乏層は広がり、Vthが高くなります。従ってQp2、Qp3のバックゲートをVDDに接続することにより④式のVthは大きくなります。更にプロセスを最適化することにより、ピンチオフ点の電圧 (④式の VGS_qn1) を下げることにより VIN(+)_minをゼロとすることができます。

次にVDDから式を立てVIN(+)_maxを考えます。

VIN(+) = VDD – VSD_qp1 – VSG_qp2 ・・・⑤

VIN(+)が入力されるとQp2のソース電圧が上がりVSD_qp1は飽和状態の最小電圧VSD_qp1_minとなります。これ以上の電圧になるとQp1は線形領域に入りドレイン電流が低下、利得が低下します。

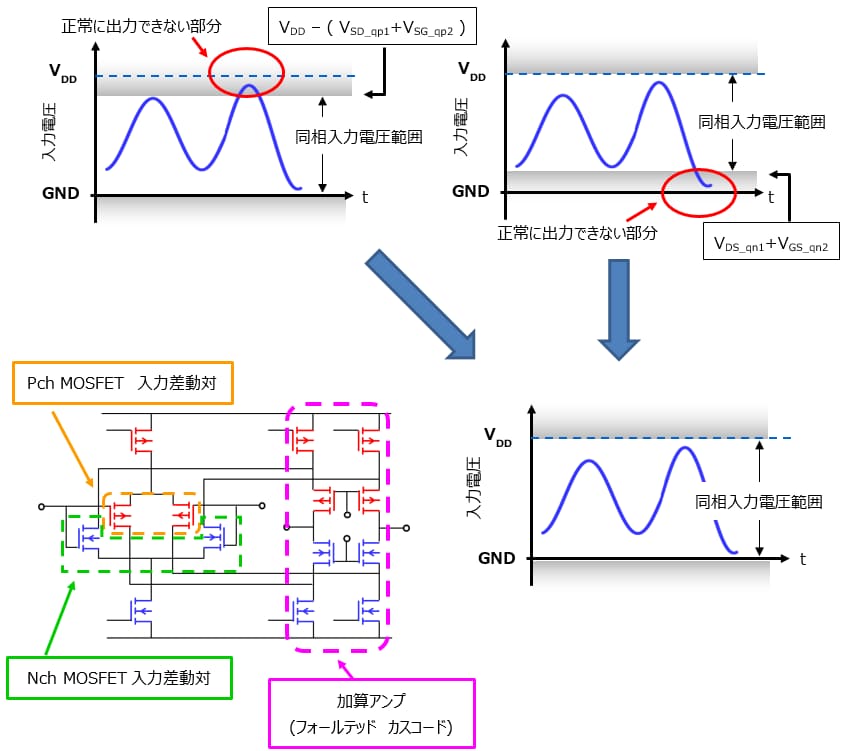

従って、入力の差動対がPch MOSFETで構成されているオペアンプはGNDからVDD – ( VSD_qp1 + VSG_qp2 )まで、同様にNch MOSFETで構成されたオペアンプではVDS_qn1 + VGS_qn2からVDDまでが使用可能な範囲 (同相入力電圧範囲) となります。

これらオペアンプの持つ同相入力電圧範囲に対して、入力差動としてNch MOSFETとPch MOSFET差動対を並列に持つフルレンジオペアンプがあります。 このタイプのオペアンプであればGNDから電源までのほぼ全範囲が同相入力電圧範囲となります。

関連リンク

以下の資料にも関連する説明がありますので、ご参照ください。