MOSFETの動作原理と仕組み|遮断・線形・飽和領域をわかりやすく解説

MOSFETの動作について教えてください

MOSFETは電子回路で広く使われる半導体素子です。本FAQでは、MOSFETの動作領域(遮断・線形・飽和)、しきい値電圧やピンチオフ電圧の意味、オン・オフのメカニズムを初心者にも理解しやすいように説明します。

特に、飽和領域の理解にはMOSキャパシターの動作が深く関係しており、その仕組みについても詳しく解説します。さらに、横型・縦型構造の違いについても触れます。

補足:しきい値電圧(Vth)について

本FAQで記載するVthはMOSFETのゲートしきい値電圧を指します。ゲート・ソース間電圧がこの値を超えるとチャネルが形成され、MOSFETがオンします。なお、BJTで使われる「熱電圧(約26mV)」とは異なる概念です。

MOSFETの概要

MOSFETはドレイン、ソース、ゲートの3端子を持ち、ゲート・ソース間の電圧でオン・オフを制御します。

動作領域としては3つあります。オフ状態である遮断領域、2つのオン状態である線形領域と飽和領域です。

ゲート・ソース間の電位差がしきい値(スレッショルド電圧 Vth)以上であればゲート直下に反転層が形成されオンとなります。ドレイン・ソース間電圧がピンチオフ電圧 VPより低ければ線形領域で、高ければ反転層の一部が空乏層となり飽和領域でオンします。飽和領域ではVDSによらずドレイン電流はほぼ一定となります。

より詳しく理解するためは、後述するMOSキャパシターの理解が必要です。

MOSFETには横型と縦型の構造がありますが、ここでは横型構造を中心に説明します。

縦型と横型の違いについては、FAQ: MOSFETの構造を参照ください。

MOSFETの動作領域

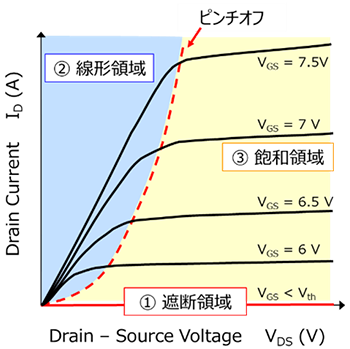

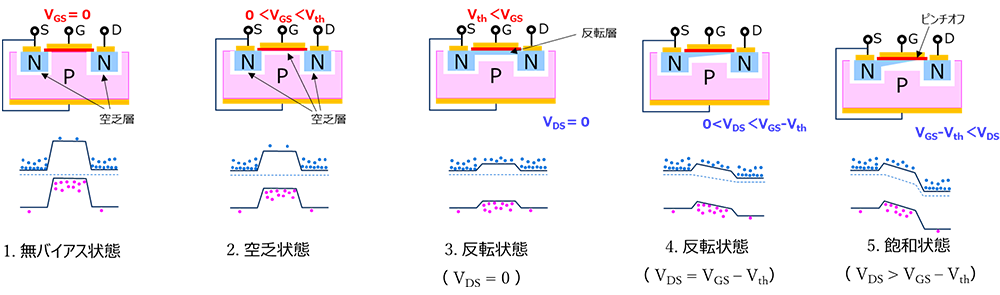

MOSFETには以下の3つの動作領域があります。これらの領域はMOSFETの静特性として知られている 図-1 ID-VDSカーブ上に示されるそれぞれの範囲を指しています。

- 遮断領域(カットオフ領域):

ドレイン・ソース間電圧VDSを上げてもドレイン電流IDは流れません。. - 線形領域(リニア領域):

VDSに比例してIDが流れます。 - 飽和領域(サチュレーション領域):

IDはVDSには比例しません。ゲート・ソース間電圧に依存するほぼ一定のIDが流れます。

図-1 MOSFETの静特性と動作領域

MOSFETのVDS-ID静特性を示したグラフです。遮断領域、線形領域、飽和領域の3つの動作領域を重ねて表示し、線形領域と飽和領域の境界となるピンチオフ電圧も示しています。

MOSFETのオン・オフ条件(しきい値、ピンチオフ電圧)

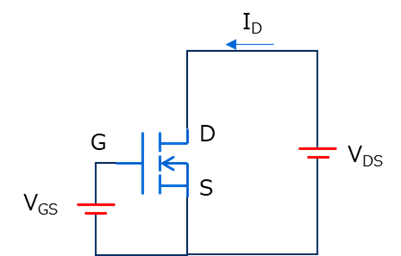

図-2に示す回路でドレイン・ソース間にVDSを印加し、ゲート・ソース間の電圧を徐々に上げていくと、ゲート直下に反転層が形成され、MOSFETはオンします。このオンするときの電圧をゲートしきい値電圧(スレッシュホールド電圧)Vthと呼びます。

印加するVDSの電圧によってリニア領域と飽和領域に分けられます。(図-1)

- オフ条件:

VGS < Vth → MOSFETはオフ(遮断領域) - オン条件:

VGS ≥ Vth → MOSFETはオン

・0 < VDS ≦ VGS – Vth : 線形領域でオンします

・VDS ≧ VGS – Vth : 飽和領域でオンします

この境界となる電圧をピンチオフ電圧VP (VP = VGS - Vth)と呼びます。

図-2 静特性測定回路

MOSFETのVDS-ID静特性を測定するための基本回路図です。ドレイン・ソース間にVDSを印加し、ゲート・ソース間にVGSを加えて動作領域を確認します。

注意:ここでいうVthはMOSFETのゲートしきい値電圧です。ゲート電圧がこの値以上になると反転層が形成されオン状態になります。BJTの熱電圧とは異なるので混同しないでください。

MOSFETの物理構造とバックゲート

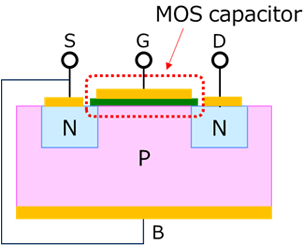

最も単純な横型N-ch MOSFETは図-3に示すようにp型基板、2か所のp型基板に埋め込まれたn型領域、そして2か所のn型領域をつなげる形で半導体と絶縁された金属板で構成されています。この金属板と絶縁膜、p型基板がMOSキャパシターとして動作します。

それぞれの領域には電極がついており、n型領域の2つの端子はソース(S)とドレイン(D)、MOSキャパシターの端子はゲート(G)と呼ばれる。裏面端子はバックゲート (またはボディ) と呼ばれ、ディスクリート素子では通常は内部で通常ソースに接続されています。従って、MOSFETを使用するときには考慮することはほとんどありません。

バックゲートはMOSFETを構成するサブストレート(Well、Bulk)に接続される端子です。この端子はN-ch MOSFETであればMOSFETに印加される最低電位以下の電位に、P-ch MOSFETであれば最高電位以上の電位に接続されることになっています。この端子がこの条件を満たさないと、例えばN-ch MOSFETであれば、ソース端子(S)とバックゲート(B)間のpn接合がオンして、MOSFETとしての動作(ゲート電圧によるオン・オフ)をしません。一般的な用途の場合、ソース端子はN-ch MOSFETでは最低電位、P-ch MOSFETでは最高電位で使用されます。このため、ディスクリート素子では内部でソースとバックゲートが短絡された状態でパッケージングされています。

図-3 横型N-ch MOSFET 簡易断面図

基本構造図です。ドレイン(D)、ソース(S)、ゲート(G)、バックゲート(B)の4端子を示し、ゲート電極とp型基板の間に絶縁膜を挟んだMOSキャパシタ―の位置も示しています。

N-ch MOSFETの動作

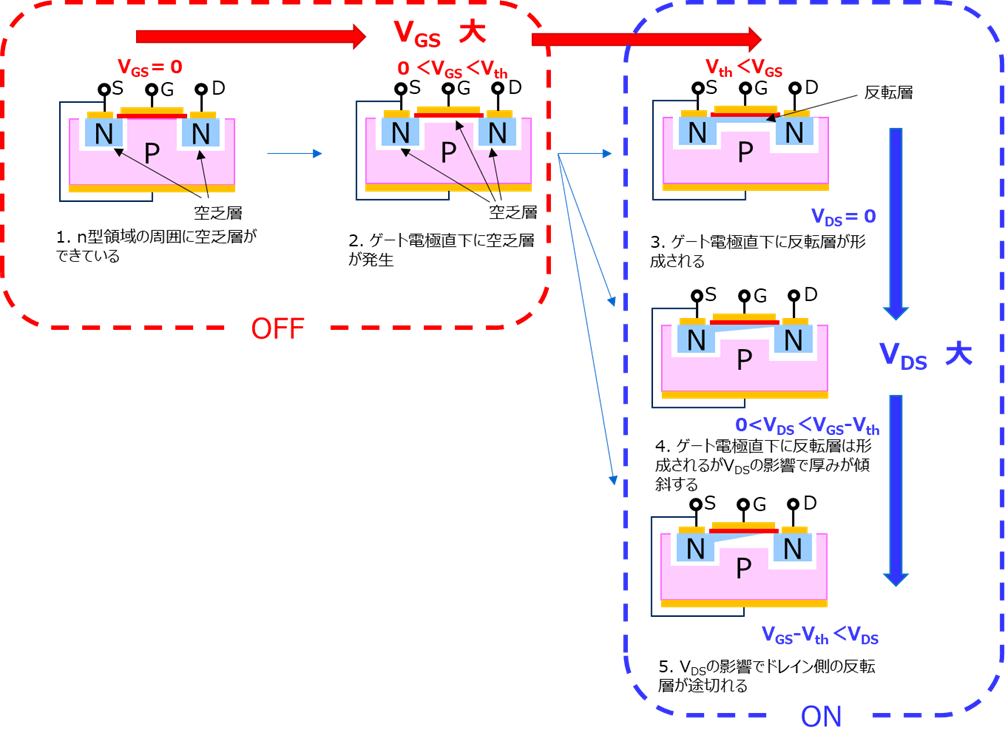

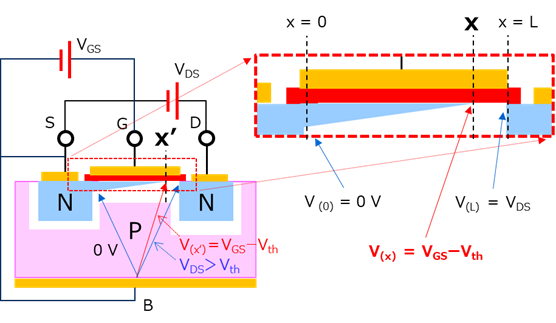

図-4 横型N-ch MOSFETの動作

MOSFETの動作状態の変化を示しています。VGSの増加により、無バイアス状態から空乏状態、反転層の形成までの過程を示し、その後VDSを加えて線形領域(反転層がドレインまで連続)と飽和領域(反転層がドレイン側で途切れる)を図示しています。

MOSFETはゲート・ソース間の電位差によって、ドレイン・ソース間にチャネル層(反転層)が形成されオンします。オン・オフの各状態について図-4を用いて説明します。

- 無バイアス状態 VGS = 0: 埋め込まれたn型領域とp型基板の間に内部電位によって空乏層が生じています。

- 空乏状態 VGS < Vth: ゲートに正の電圧が印加されると、電極側はプラス、半導体側はマイナスに帯電しP型半導体の正孔と相殺してゲート直下に空乏層が生じます。

この状態までがオフ状態です。 - 反転状態 VGS ≧ Vth: 更にゲート電圧が増加すると、ゲート電極直下に電子が集まり反転層が形成される。

これによりn型半導体と同様の状態となり、S-G間はこの反転層によって接続されます。反転層はN-ch MOSFETの場合、自由電子が過多の状態ですので、n型半導体と同じ性質を持ちます。この反転層によってドレイン・ソース間に電流が流れるチャネルが形成されます。

この反転状態をMOSFETがオンの状態と呼びます。MOSFETのオン状態は図-1に示す線形領域と飽和領域の2つの状態があります。それぞれの状態はドレイン・ソース間の印加電圧VDSによって決まります。 - 線形領域でオン 0 < VDS ≦ VGS – Vth : 反転層はドレインに近づくに従って浅くなっていますが、ドレイン・ソース間で途切れなく形成されています。従って、VDSにほぼ比例する形でIDが流れます。

- 飽和領域でオン VDS ≧ VGS – Vth : 反転層はドレインに近い部分で途切れています。ドレイン電流(ソースから注入された電子)は反転層とドレイン間の空乏層を通って流れます。ただし、ドレイン電流はVGSが固定の場合、ほぼ一定の電流となります。

MOSキャパシター

もう少し深く理解をするためには、MOSキャパシターの理解が重要です。

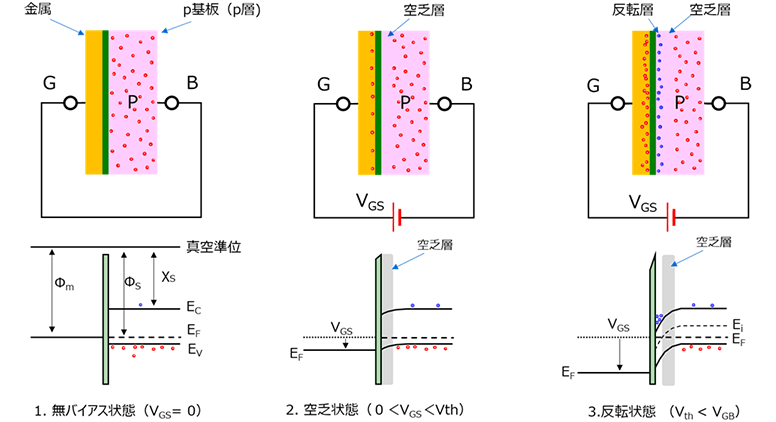

MOSキャパシターは図-3の点線で囲まれた部分です。図-4で説明した1~3の各状態でのMOSキャパシターとエネルギーバンドの状態を図-5に示します。MOSキャパシターはエネルギーバンド図に合わせて左に90°回転させた形で記載しています。

N-ch MOSFETのMOSキャパシターは絶縁膜を挟んだ金属電極とp基板によって構成されます。このMOSキャパシターはMOSFETのゲートに相当する電極(G)とバックゲート(B)間の電圧によって状態が変化します。バックゲートとソースは短絡されており同電位であるので、ここではMOSFETで通常使用されるVGSをパラメータとして用います。

図-5 MOSキャパシタ―とエネルギーバンド図

MOSキャパシタ―の構造と3つの動作状態を示しています。上段は金属電極・絶縁膜・p型基板からなるMOSキャパシタ―の断面図で、無バイアス、しきい値電圧未満のバイアス、しきい値電圧を超えるバイアスの3状態を表示しています。下段には、それぞれの状態に対応するエネルギーバンド図を示し、フラットバンド、空乏、反転の変化を説明しています。

- 無バイアス状態です。図のようなエネルギーの状態になります。この状態では、絶縁膜直下には何も生じていません。この例では金属の仕事関数Φmとp型半導体の仕事関数ΦS(フェルミ順位と真空準位の差)が同じこととして記載しているため、バンド曲がりが生じていない状態(フラットバンド状態)となっていますが、通常は異なるためバンド曲がりが生じます。尚、仕事関数の差分(ΦSーΦm)をフラットバンド電圧と呼びます。

- 空乏状態です。0<VGS<Vth の電圧を印加しているので、バンド曲がりが発生しています。 印加した電圧によりp型を構成している不純物(Bなど)が電子を捕獲しp型半導体側にのみ空乏層が形成される。(ゲート側をプラスで電圧を印加しているのにゲート側が下がるのは、エネルギーバンド図が電子を基準としているためです。)

- 反転状態です。Vth<VGS が印加され更にバンドが曲がります。絶縁膜近傍ではこの曲がりによってるとフェルミ準位EFが真性フェルミ準位Eiより高くなる状態が生じp型からn型に反転します。この部分にp型の少数キャリアである電子が蓄積されます。

このようにMOSキャパシターは電極(G)とバックゲート(B)間に印加する電圧VGSによって、状態が変化します。MOSFETのオン・オフは反転状態とそれ以外の状態を切り替えることで行われます。ただし、ここでは考慮していないドレイン・ソース間に印加する電圧により、もう一つの状態が生じます。これが飽和です。

MOSFETの飽和

MOSFETのオンの状態には、線形と飽和の2つの状態があります。(図-1参照)ゲート電圧VGSがしきい値Vthを超えてオンした状態で、ドレイン電圧VDSを上げていくと、ある電圧で反転層(チャネル)のドレイン側が空乏化し、反転層が途切れます。この境界となる電圧をピンチオフ電圧VPと呼び、VP = VGS - Vthで表されます。飽和状態の条件は VDS ≥ VGS - Vth です。

飽和状態に入ると、VDSを高くしてもドレイン電流IDはほぼ一定となります。なぜ一定となるのかを説明します。

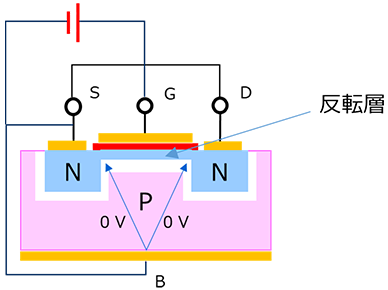

VGS > Vth で VDS = 0Vの時は、ゲートとp型半導体の間の電位差はソース近傍もドレイン近傍も同じで、均等に反転層が形成されます。(図-6参照)

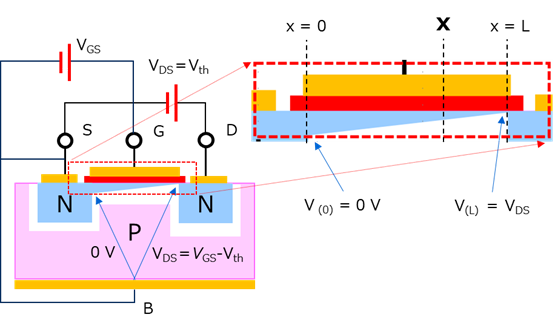

図-6 反転状態のN-ch MOSFET

(VDS = 0、VGS > Vth)

ゲート電圧により均一な反転層が形成され、ドレインとソースが接続されます。

VGS >Vth でドレイン・ソース間に電圧 VDSが印加されている場合、ソース側は0V、ドレイン側はVDSとなります。VDSを印加すると、反転層内の電位はソースからドレインにかけて連続的に変化します(図-7参照)。

図-7 反転状態のN-ch MOSFET

(VDS=VGS-Vth、VGS>Vth)

ピンチオフ直前のN-ch MOSFET(VGS > Vth、VGS − VDS = Vth)。反転層がソース側で厚く、ドレイン側で薄い。

ソースからドレインまでの距離をLとすると、位置xにおける電位V(x)によりゲートと基板間の電位差は次の式で表されます。

VGS(x) = VGS – V(x)

この電位差がVth以上なら反転層が形成され、未満なら反転層は形成されず空乏層となります。

- VGS – V (x) ≧ Vth : 反転層

- VGS – V (x~L) < Vth : 空乏層

x’ で VGS – V(x’) = Vth となる場合の図を図-8に示します。

図-8 飽和状態のN-ch MOSFET

(V(x')=VGS –Vth、VGS>Vth)

ピンチオフ点を示し、ソースからドレインまでの各点に対しバックゲートからの電位を表示している。

x’でVGS - V(x’) = Vthとなる位置はピンチオフ点と呼ばれます。ピンチオフ点からドレイン端までの間は空乏層となります。空乏層はキャリアがほとんど存在しませんが図-9のエネルギーバンド図に示すように、ソースからドレイン方向には拡散障壁がありません。このため、電子は空乏層の電界で加速されてドレインに到達します。

図-9 MOSFETの各状態におけるソース・ドレイン間のエネルギーバンド図

図-9 MOSFETの各状態におけるエネルギーバンド図。飽和状態ではピンチオフ点以降に障壁がなく、電子が電界で加速されることを示します。

したがって、ドレイン電流はソースからこのx‘まで反転層に印加されている電圧(VGS – Vth)と、その区間のチャネル抵抗で決まります。この抵抗を Rch(sat) とすると、飽和時のドレイン電流は次の式で表されます。

ID(sat) = (VGS − Vth) / Rch(sat)

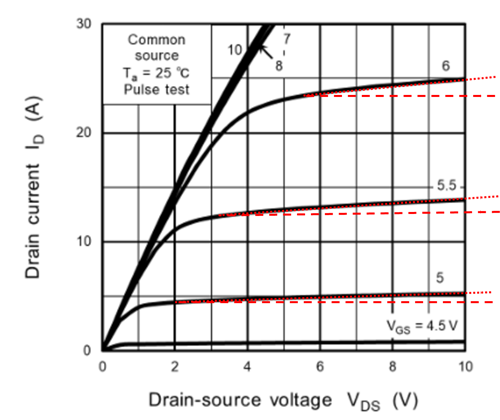

このため、飽和状態ではドレイン電流はVDSにほぼ依存しません。ただし、VDSが増加するとピンチオフ点がソース側に移動し、チャネル長が短くなるため、Rch(sat)が減少し、IDはわずかに増加します(チャネル長変調効果)。実際の製品での増加状態を図-10に示します。

図-10 N-ch MOSFET ID-VDSカーブ(TK155A60Z1)

図-10 N-ch MOSFET(TK155A60Z1)のID-VDSカーブ。飽和領域で電流は理想的には一定ですが、実際にはVDS増加でわずかに増加します。赤点線は理想値を示します。

【補足】

短チャネル製品とチャネル長変調効果 チャネル長変調効果によるドレイン電流の増加は、短チャネルMOSFETほど顕著になります。これは、ピンチオフによる実効チャネル長の変化率が短チャネルでは相対的に大きいためです。短チャネルの製品とは、MOSFETのチャネル長が非常に短く設計されたデバイスで、最新の微細プロセス技術を用いたロジックICや高速スイッチング用途のMOSFETが該当します。チャネル長が短いほど、λ(チャネル長変調係数)が大きくなり、飽和領域での電流増加の傾きが大きくなります。

関連リンク

製品ラインナップについては、以下のページ・ドキュメントを参考にしてください。

パラメトリック検索

MOSFET

FAQ

その他

※ このFAQ内で使用している社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。