MOSFETにはどのような構造がありますか?(横型MOSFETと縦型MOSFET)

MOSFETには大きく分けて横型MOSFETと縦型MOSFETがあります。

これらは電流の流れる方向が、表面に平行(横方向)であるか垂直(縦方向)であるかで分類されます。

- 横型MOSFETの特徴:ソースとドレインが同一平面(上部)に配置され、電流は横方向に流れます。構造が単純で端子がすべて上部にあるため、ICやLSIなどの集積回路に広く使用されます。

- 縦型MOSFETの特徴:ソースが上部、ドレインが下部に配置され、電流は垂直方向に流れます。高耐圧化が容易で、大電流に対応できるため、電源回路に多く採用されています。

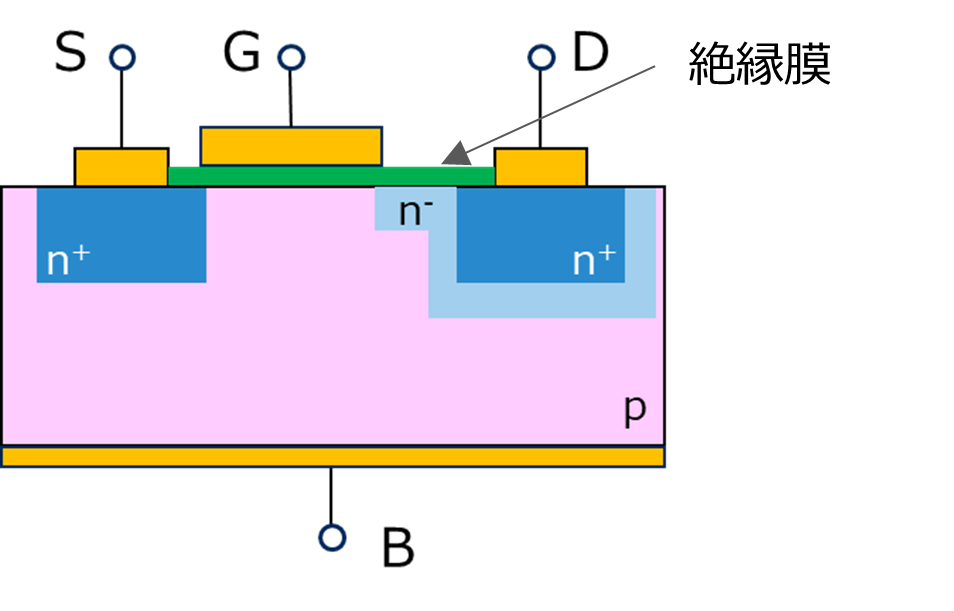

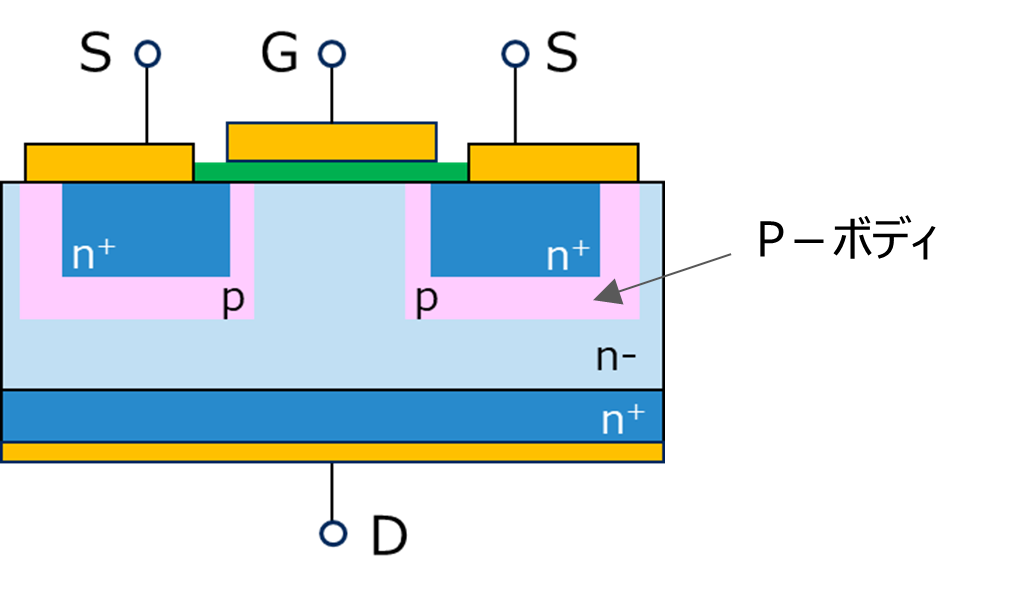

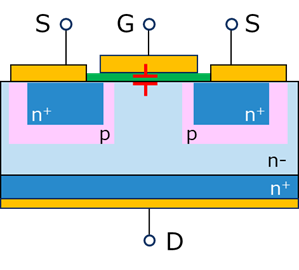

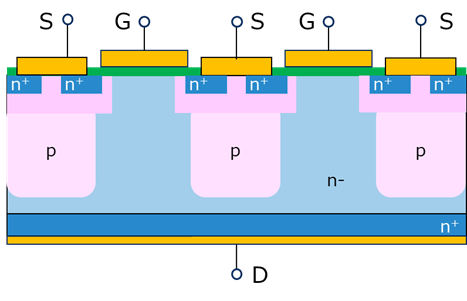

ここでは主流であるN-ch MOSFETを中心に説明します。N-ch MOSFETでは、p型基板(ボディと呼ばれる)の中にソースとドレインとなる2つのn型領域が形成されています(図-1 aを参照)。その上には、薄い酸化膜を介してゲート電極が配置され、ゲートはソース・ドレインとは電気的に絶縁されています。各領域には電極がありn型領域の2つの端子はソース(S)とドレイン(D)、制御端子である絶縁膜上に配置された電極はゲート(G)と呼ばれます。なお、ボディ端子はほとんどの場合、ソース電極(最低電位)に接続されます。

ゲート電圧が印加されると、ゲートとボディ間の電位差によって基板表面に反転層が形成されます。この反転層がソースからドレインへの電流経路(チャネル)となります。さらに、ドレイン・ソース間に電圧VDSが加わると、チャネルには電位勾配が生じ、ドレイン側の電位はソースより高くなります。この電位差が大きくなると、チャネルのドレイン側がピンチオフし、チャネルは途中で途切れます。ドレイン端には空乏領域が広がり、キャリアはこの領域を電界によりドリフトし、ドレインに到達します。これがMOSFETの飽和動作です。

飽和の詳細は、FAQ「MOSFETの動作」をご参照ください。

横型MOSFETと縦型MOSFETの基本的な構造を図-1に示します。

- 横型構造: 3つの端子(ドレイン・ソース・ゲート)が全て上面に配置されています。裏面はボディ(B)と呼ばれる端子で、通常はソースに接続されます。ドレインからソースに流れるドレイン電流は横方向に流れます。端子が全て上部にあり構造が単純であることから、IC化が容易でCMOSロジックICなどのICやLSIに多く使用されています。また、低容量であることから、RFアンプなどで使用されるMOSFETとして横型構造が用いられます。

- 縦型構造: 上面には2つの端子(ソース・ゲート)が配置され、ドレインは裏面に配置されます。横型MOSFETのボディに相当する層(P-ボディ)は上面でソースと接続されています。ドレインからソースに流れるドレイン電流は縦方向に流れます。高耐圧化が可能で、中・高耐圧の多くのデバイスのほとんどはこの構造になっています。

汎用的な横型構造プロセスとしてはプレーナーゲート構造が挙げられます。縦型構造では特性を大幅に向上させたトレンチゲート構造やスーパージャンクション(SJ)構造などの縦型構造が主流です。また、最近ではRESURF(Reduced Surface Field)原理を応用したフィールドプレート(FP)構造が開発されています。

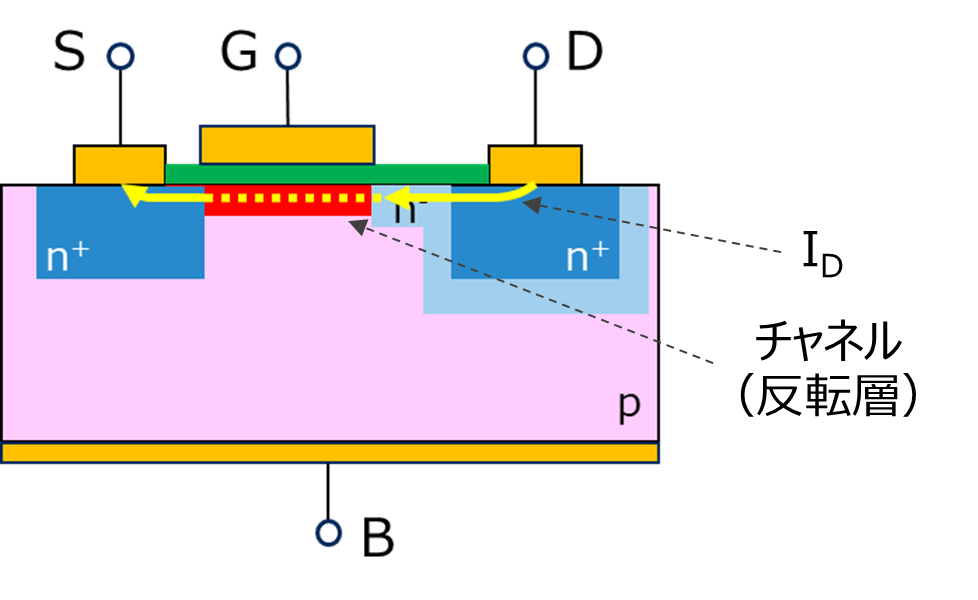

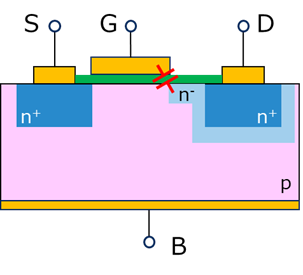

a) 横型構造

表面にソース(S)、ゲート(G)、ドレイン(D)の端子、裏面にボディ(B)の端子があります。ドレイン側のn+層の外側にはn-層が取り囲むように描かれ、耐圧を維持するためにゲート直下でソース側に少し伸びています。

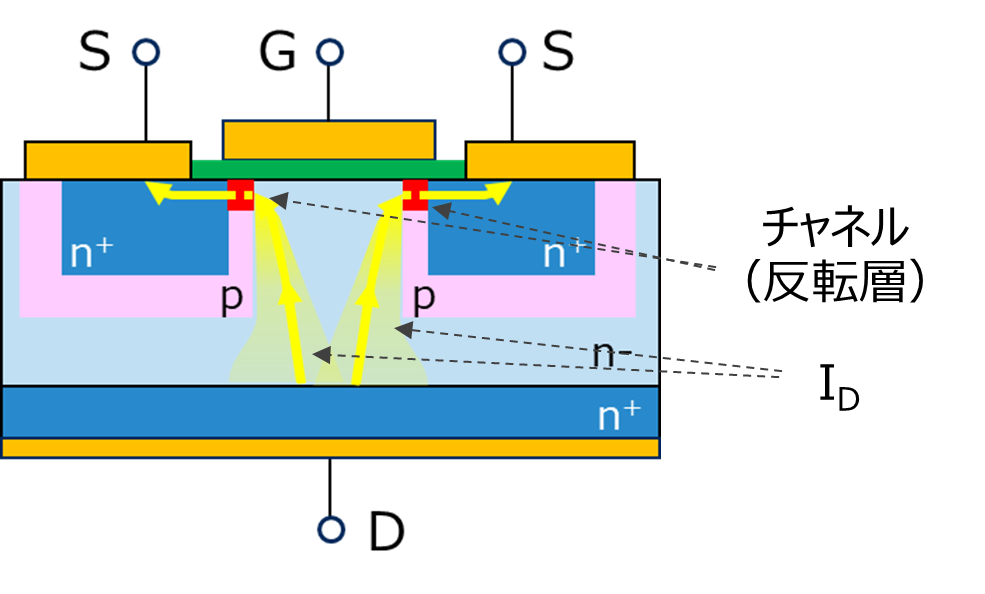

b) 縦型構造

表面にソース(S)とゲート(G)、裏面にドレイン(D)の端子があります。ソースのn+層を取り囲むようにp層があり、この部分はp-ボディと呼ばれます。

図-1 N-ch MOSFETの構造(縦型と横型)

この図はN-ch MOSFETの横型構造と縦型構造の簡易断面図を示しています。

それぞれの構造によるMOSFETの特徴:

横型構造

- プロセスが単純でゲート・ドレイン・ソース端子が全て上面にあることからIC化が容易

- ゲート・ドレイン間容量CGDが小さく高速のアプリケーションに向いている

- 高耐圧・高電流の素子を形成することが困難(実用レベルではVDSS < 100~200V)

縦型構造

- 裏面がドレインとなるためIC化するためには、ドレインを上面に引き出すなどの処理が必要

- ゲート・ドレイン間容量CGDが大きい

- ドレイン側の電流が広く裏面方向に拡散するため低オン抵抗化が容易

- ドレイン・ソース間電圧VDSSの高耐圧化が容易

MOSFETの高耐圧化

MOSFETのドレイン・ソース間の耐圧はn-ドリフト層(ドレイン)の不純物濃度を下げることによって高くすることができます。ただし、この不純物濃度を下げると耐圧は上昇しますが、同時にオン抵抗は高くなってしまいます。

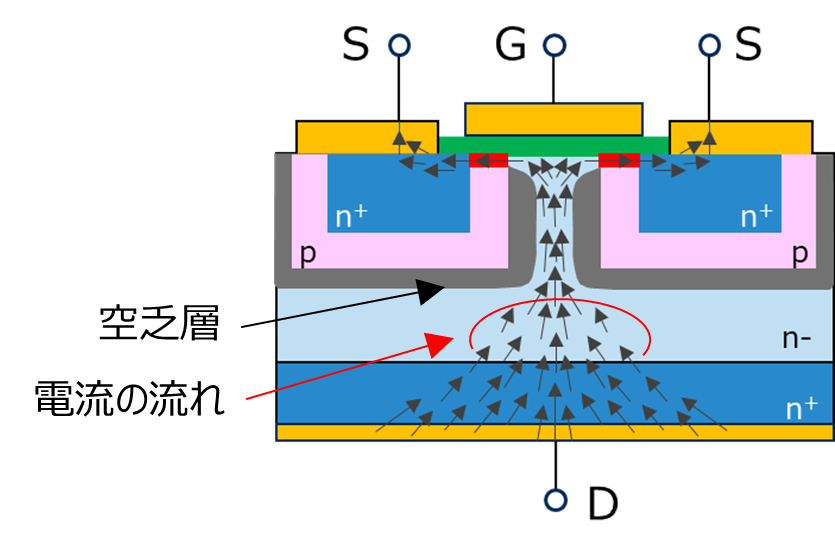

横型構造: ドレインとの間に低濃度のn-層を設けることで、ある程度は耐圧を上げることが可能です。オン時にはドレイン・ソース間に流れるドレイン電流IDは、ドレインからこのn-層の表層を通り反転層を経由してソースに流れます(図-2 a 黄色のライン)。不純物濃度の低いn-層はオン時には抵抗体になるため、高耐圧で低抵抗化するためには広い面積が必要となります。

縦型構造: 裏面がドレイン電極です。この広範囲なドレインからIDは反転層に向かって流れます(図-2 b 黄色のライン)。横型構造と同様にn-層の濃度を下げることで高耐圧化が可能となります。横型構造と異なり、抵抗体となるn-層に広く電流が流れるため、横型構造に比べ狭い面積で低いオン抵抗(≒ 高電流対応)を実現できます。同様に、同じオン抵抗であれば縦型は高い耐圧VDSSを実現できます。

a) 横型構造

ドレインからソースへ電流が横方向に流れます。電流はn+ドレイン領域からn-層を経由し、ゲート直下の反転層(チャネル)を通ってソースに到達します。

b) 縦型構造

ドレインからソースへ電流が縦方向に流れます。電流は裏面のドレインからn-層を通り、ゲート酸化膜と接するp-ボディのゲート酸化膜直下に形成される反転層を経由してソースに到達します。

図-2 横型・縦型N-ch MOSFET オン時の電流経路

この図は、図1で示した横型構造と縦型構造のN-ch MOSFETにおけるオン状態でのドレインからソースへの電流の流れを示しています。

MOSFETの入力容量Cissと帰還容量Crss

縦型構造は横型構造に比べて、入力容量Cissや帰還容量Crssが大きくなります。

縦型構造と横型構造で最も異なる点は、図-3に示すようにゲート・ドレイン間の容量です。横型構造ではゲート電極に対向する部分はボディのp層です。したがってゲートがドレインと対向する部分はごくわずかです。これに対し、縦型構造ではゲート電極に対向する部分はドレインのn-層です。このため縦型は横型に比べCGDが大きくなります。

ゲート・ソース間容量をCGS、ゲート・ドレイン間容量をCGD、ドレイン・ソース間容量をCDSとすると、回路設計などで用いられる入力容量Ciss、帰還容量Crss、出力容量Cossは下式で表されます。

- Ciss = CGS + CGD

- Coss = CDS + CGD

- Crss = CGD

このため縦型構造は横型構造に比べCissやCoss、Crssが大きくなります。

a) 横型構造

横型構造では、ゲートとドレイン側のn⁻層との間に容量が形成されますが、その対向面積は小さいためCGDは小さくなります。

b) 縦型構造

縦型構造では、ゲートと対向するn⁻層の面積が広く、ゲート・ドレイン間容量CGDが大きくなります。

図-3 N-ch MOSFET ゲート・ドレイン容量 CGD(縦型構造と横型構造)

この図は図-1の構造図を用いて、横型構造と縦型構造におけるゲート・ドレイン間容量CGDがどの部分に生じるかを示しています。

このようなことを背景に、横型MOSFETは無線通信機の出力(RFアンプ)に、縦型はスイッチング電源やDC-DCコンバータ、ロードスイッチなどの電源回路に使用されています。縦型構造に関しては、性能改善のために更なるプロセス改善が進められています。このプロセス改善の目的の一つはオン抵抗低減です。

MOSFETのオン抵抗

以下にMOSFETのオン抵抗(RDS(ON))について説明します。

MOSFETのドレイン・ソース間の耐圧 VDSS とオン抵抗 RDS(ON) では、VDSS を上げると RDS(ON) が上がる関係にあります。また抵抗 R は、断面積 S と長さl、抵抗率 ρ を使って以下のように示されます。

R = ρ x l / S

従って、l を短く、S を広く、ρ を低くすれば抵抗は低くなります。半導体の場合、抵抗率 ρ は不純物濃度を N、移動度を μ、電子電荷を q とすると下式になります。

ρ = 1 / ( q x μ x N )

ρ を下げるためには N、μ、q を大きくすれば良いわけですが、qは物理定数、μは材料・物性に強く依存し、プロセスで自由に増やすのは容易ではありません。したがってρを下げるには主に濃度Nを上げることが有効です。唯一濃度 N を高くすることで抵抗が下がることがわかります。

MOSFET オフ時にドレイン・ソースに逆バイアス VDSS を印加した場合、この逆バイアスに比例して空乏層が伸びます。また、不純物濃度 N が低くなるほど、空乏層はより遠くまで伸びることになります。空乏層内では、多数キャリアは存在せず不純物イオン(固定電荷)のみが存在していると考えます。この固定電荷に起因する電界の合算値が臨界電界 Ecritical を超えるとアバランシェ降伏が生じます。このアバランシェ降伏が生じない最大電圧が耐圧 VDSS です。このように、N を上げると R は下がるが、同時に VDSS も下がる、N を下げると R は上がるが、VDSS は上がるというトレードオフの関係は主に不純物濃度 N によります。

N-ch MOSFETではゲート・ソース間にオン電圧を印加すると、ゲート直下のp層に反転層が形成します。この反転層はp層でありながら電子が過多な状態となっており、n層と同様の状態になっています。この反転層(チャネルとも呼ばれます)により、ドレインとソースが導通しMOSFETはオンとなります。オンの状態には線形領域と飽和領域がありますが、ここでは線形領域におけるオン抵抗について説明します。飽和領域などのMOSFETの動作に関する説明は、以下のFAQを参照ください。

MOSFETの動作について教えてください

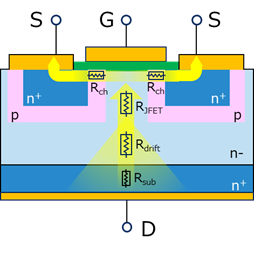

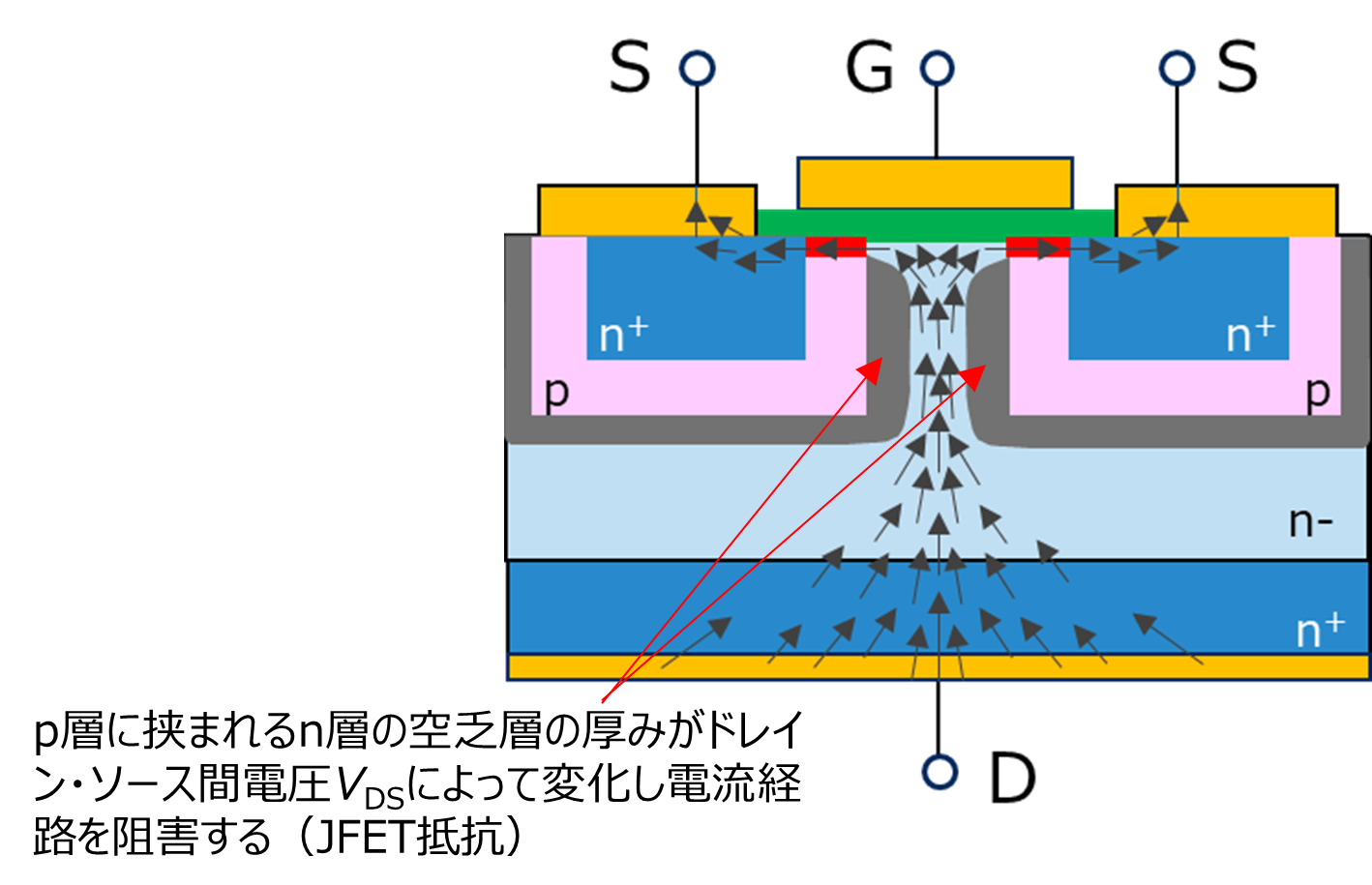

ドレインからソースに流れる電流の経路を図-4 aに示します。この電流が流れる領域によって抵抗の生じる要因が異なります。これらは図-4 bに示す抵抗に分けられます。それぞれの抵抗について少し説明します。

- チャネル抵抗 RCH: チャネル領域の抵抗でチャネルの幅と長さ、キャリアの移動度や密度によって変わります。

- JFET抵抗 RJFET: p層に挟まれる部分のpn接合の空乏層の厚みはドレイン・ソース間電圧 VDS によって変化します。これにより電流経路の幅が変わり、抵抗値も変化します。この振る舞いがJFETに似ていることからJFET抵抗と呼ばれます。なお、JFET抵抗は縦型MOSFETに特徴的な成分で、ソース間に挟まれたp層の空乏層によって電流経路が狭まることで発生します。

- ドリフト抵抗 Rdrift: P領域から基板であるn+領域までのn-層による抵抗。n-層は高耐圧MOSFETでは耐圧を決める部分で高耐圧になるほど濃度は低く、抵抗は高い。

- 基板抵抗 Rsub: 基板領域の抵抗。n-層の濃度と深さ、電流の流れる経路や広がり方によって変わります。

前に述べたように、RDS(ON)とVDSSはトレードオフの関係にあります。従って、VDSS = 40V のMOSFETと VDSS = 600V のMOSFETではオン抵抗(RDS(ON))に占めるこれらの抵抗の比率が異なります。特に主にVDSSに影響するドリフト領域の抵抗Rdriftの占める割合は、高耐圧のMOSFETほど大きくなります。

その割合は、同じプレーナーゲートタイプのMOSFETの場合(製品によって変わるので精度のある数字ではありませんが)以下のようになります。

40V:RCH = 10%、RJFET = 40%、Rdrift=40%、Rsub =10%

600V:RCH = 1%、RJFET = 20%、 Rdrift=80%、Rsub =0%

従って、ターゲットとする耐圧によってオン抵抗を低減する手法も異なります。

- 低耐圧MOSFET:チャネル抵抗とJFET抵抗の低減 →トレンチゲート構造

- 高耐圧MOSFET:ドリフト抵抗の低減 →スーパージャンクション構造

a) 電流の流れ

オン状態では、裏面のドレインから電流が流れ、ソース間に向かって流れます。

b) オン抵抗RDS(ON)

オン抵抗は、チャネル抵抗RCH、JFET抵抗RJFET、ドリフト抵抗Rdrift、基板抵抗Rsubに分けられます。JFET抵抗は縦型構造で顕著な抵抗です。

図-4 縦型N-ch MOSFET オン時の電流の流れとオン抵抗

縦型N-ch MOSFETにおけるオン状態の電流経路と、オン抵抗を構成する要素を示しています。

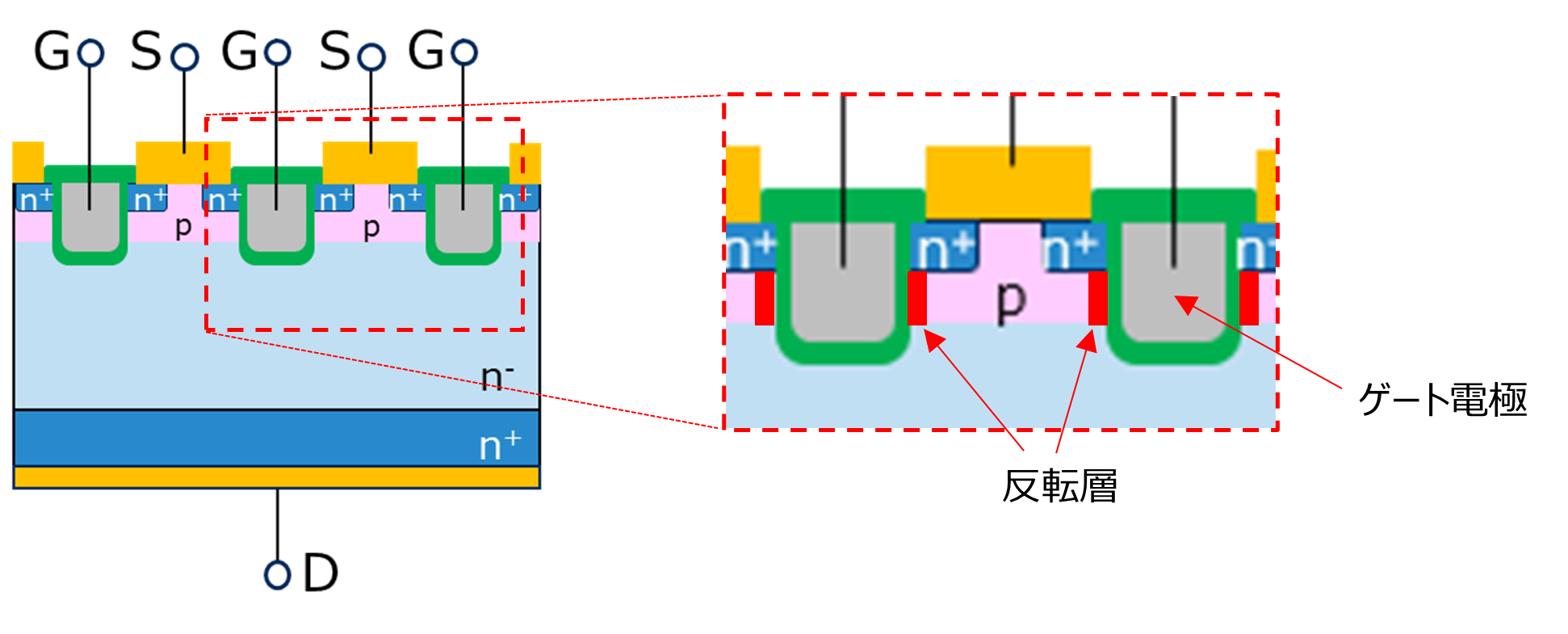

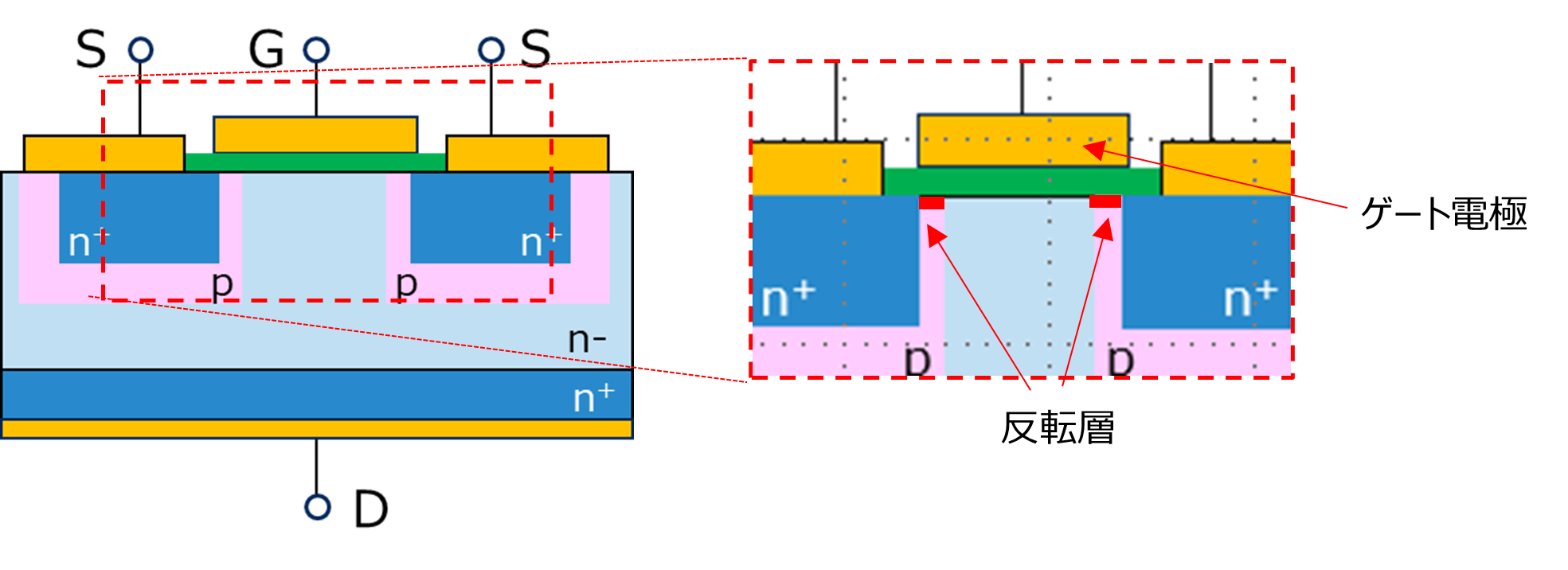

トレンチゲート構造

従来構造であるプレーナーゲート構造(ここまで縦型構造として扱ってきたものと同じ構造です)と最も異なる点は、ゲートの配置です。プレーナーゲート構造では、デバイス表面にゲート電極を乗せるように配置していましたが、トレンチゲート構造ではデバイスの表面から溝を掘りゲート電極を埋め込む構造となっています。(図-5 トレンチゲート構造とプレーナーゲート構造)反転層は従来の横方向に対し、縦方向に形成されることになります。このことによって、下記の利点があります。

- 微細化が可能で単位面積当たりのチャネル数を増やすことができます。これによりチャネル抵抗を著しく低減できます。

- 電流経路を阻害するJFETが構造的になくなり、大幅に削減されます。

- プレーナー型に比べて電流密度が高く、同じ面積のチップでより多くの電流を流すことができます(図-6)。

- ゲート電荷はプロセス設計にも依存しますが、低下する傾向があります。

a)トレンチゲート構

造トレンチ構造の簡易断面図です。反転層はゲートに沿う形で縦方向に形成されます。これにより、チャネル密度を高め、チャネル抵抗を低減できます。また、JFET抵抗の影響も軽減できます。

b) プレーナーゲート構造

これまで説明してきた縦型構造です。反転層は表面に沿って横方向に形成されます。このため、電流経路が狭まりやすく、JFET抵抗の影響を大きく受けます。

図-5トレンチゲート構造とプレーナーゲート構造 (N-ch MOSFET)

N-ch MOSFETにおけるトレンチゲート構造とプレーナーゲート構造の断面を比較しています。最も異なる点は、反転層の形成方向であり、プレーナー構造では横方向、トレンチ構造では縦方向に形成されます。

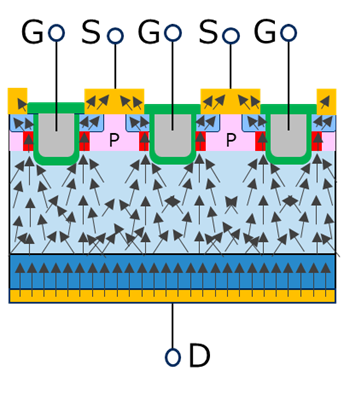

a) トレンチゲート構造

電流は縦方向に広く流れ、JFET抵抗の影響はほとんどありません。

b) プレーナーゲート構造

電流は横方向に狭い経路を通るため、JFET抵抗の影響を大きく受けます。

図-6 トレンチゲート構造とプレーナーゲート構造における電流の流れ

この図は、トレンチ構造とプレーナー構造の電流経路を比較し、JFET抵抗の影響度合いを示しています。

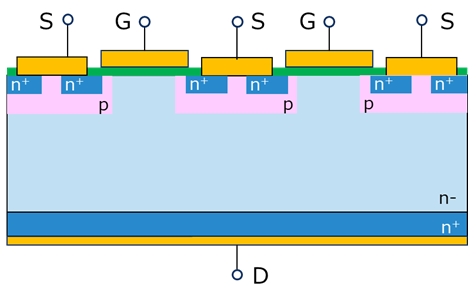

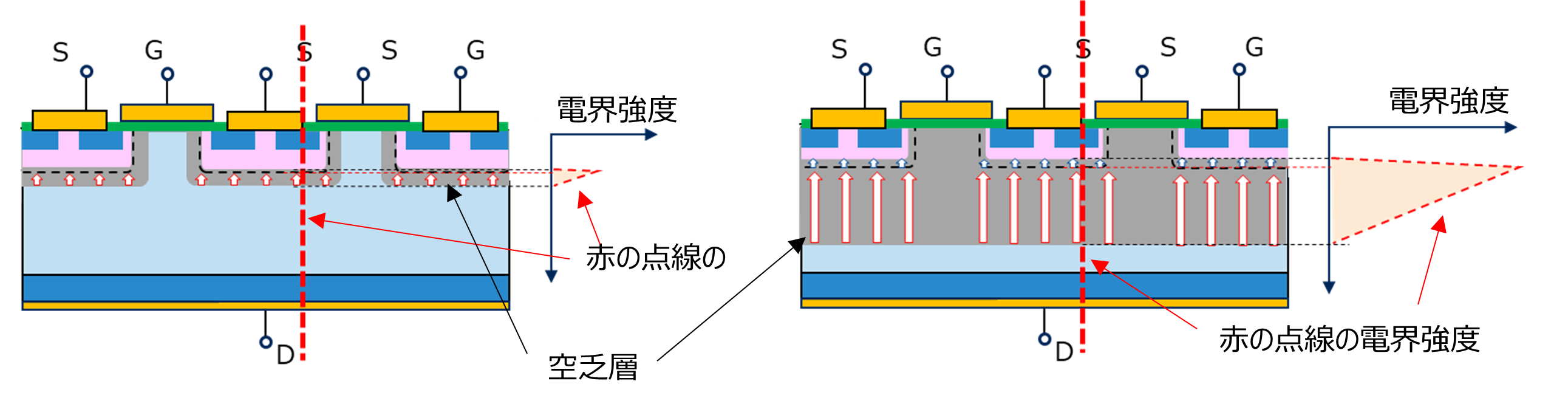

スーパージャンクション構造

MOSFETの高耐圧化を図るためには、ドリフト領域(n-層)の濃度を下げ、同時にn-層の厚みを増す必要があります。しかし、これによりMOSFETのオン抵抗を構成するドリフト抵抗が増加する問題が生じます。この解決策としてスーパージャンクション構造が採用されています。

従来のプレーナー構造は平面的な構造であるため、電界はn層(n-層)とp層の境界面で最も高くなります。これに対し、スーパージャンクション構造はn-層の一部にp層(Pピラー層)を柱状に形成し、P-N層を交互に配置する構造です。このため、n層(n-層)とp層の境界面は縦方向(深さ方向)に存在します。このpn接合に沿って空乏層が広がり、高電圧が印加されるときには、この柱状部分が完全空乏化します。

電界強度は従来構造と同様に境界面で最も高くなりますが、電界は縦方向(柱状に沿って)に分散され均一化されます。これにより、同じ不純物濃度でドレイン・ソース間に従来構造より高い電圧(ドレイン・ソース間電圧 VDS)を印加することが可能となります。これは、同じ耐圧(VDSS)であれば、より低オン抵抗(RDS(ON))のMOSFETが実現できることを意味します。

a) プレーナーゲート構造

従来の縦型構造で、n層とp層の境界面は平面的に存在します。高耐圧化のためにはドリフト層(n⁻層)の不純物低濃度化と厚みを増す必要がありますが、この構造では電界が境界面に集中しやすく、オン抵抗低減には構造的な制約があります。

b) スーパージャンクション構造

n層内に柱状のp層を形成し、P-N層を交互に配置する構造です。高電圧印加時には柱状部分が完全空乏化し、電界が均一化されます。

図-7 スーパージャンクション構造とプレーナーゲート構造(N-ch MOSFET)

この図はMOSFETの高耐圧化を実現するための構造比較を示しています。スーパージャンクション構造では、n層内にp層(Pピラー)を柱状に形成し、P-N層を縦方向に交互配置することで、電界を横方向に分散しやすい構造となり、高耐圧化と低オン抵抗の両立を可能にします。

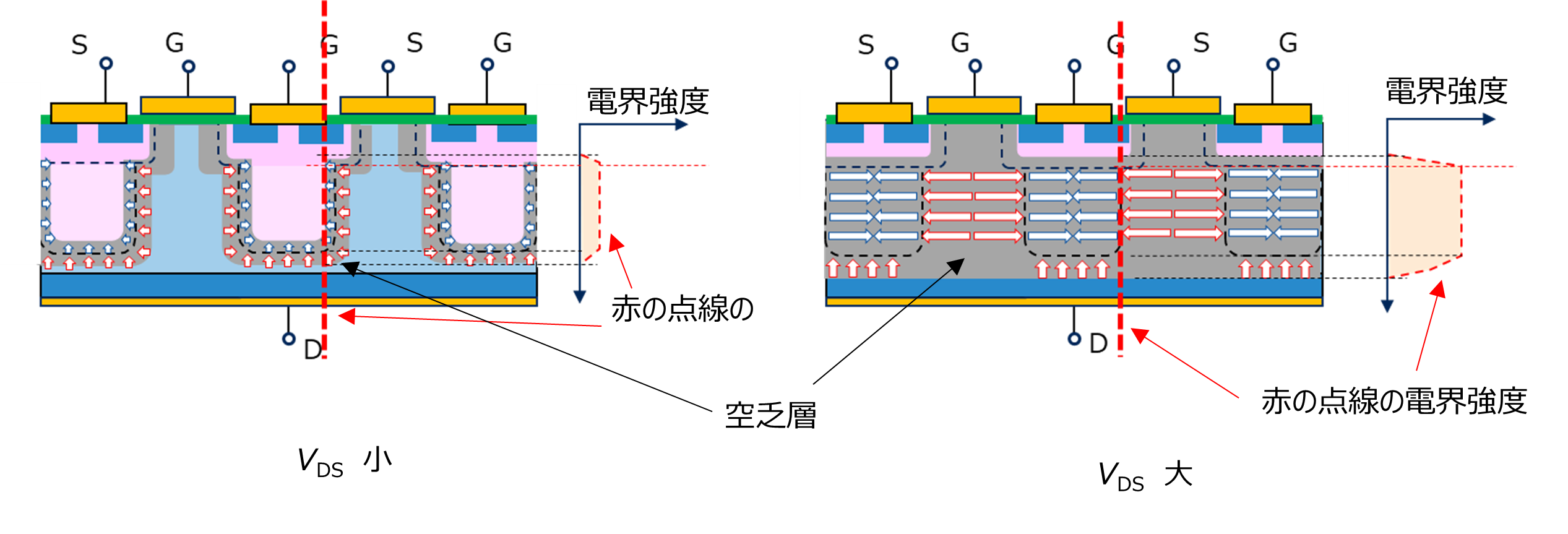

a) プレーナーゲート構造

・VDS小:空乏層はドリフト層(n⁻層)に部分的に広がり、電界は接合付近に集中します。

・VDS大:ドリフト層全体が空乏化しますが、電界は依然として境界面に集中しやすく、高電圧時の性能に制約があります。

b) スーパージャンクション構造

・VDS小:空乏層はまだ完全に広がっておらず、電界は局所的に分布します。

・VDS大:交互に配置された P-N 層全体が完全空乏化し、電界が横方向に分散して均一化されます。これにより電界集中が抑えられ、高耐圧化が可能になります。

図-8 スーパージャンクション構造とプレーナーゲート構造 MOSFETオフ時の電界の状況

この図はオフ状態でドレイン・ソース間電圧VDSが小さい場合と大きい場合の電界分布を比較しています。赤点線に沿ってソースからn-層→p層→n-層を通る電界強度を各図の右側に示しています。

関連リンク

製品ラインアップやその他のドキュメントについては、以下のページ・ドキュメントを参考にしてください。

パラメトリック検索

MOSFET

FAQ

その他

※ このFAQ内で使用している社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。