-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

はじめに

データストレージに対する需要の増大に対応するため、データセンター (図1) の拡張と新設が求められています。しかし、無計画な拡張は、最終的に電力需給の逼迫を招くため、データセンターの消費電力を抑制することが、併せて求められています。

データセンターの消費電力を削減する非常に効果的な方法のひとつは、サーバーラックに48Vバスラインを使用することです。とはいえ、このような新しいアーキテクチャーは、慎重に選択された高効率のMOSFETを使用しないと実用にはなりません。

第1章: オープン・ラック・アーキテクチャーの電力損失への対処

より優れた効率を達成するために、オープン・コンピュート・プロジェクト (OCP) が提案するオープン・ラック・アーキテクチャーでは、従来の12Vバスラインではなく48Vバスラインを使用することで、電力損失に対処しています。

この仕組みを理解するには、まず、電線における電力損失はI2Rで計算されることを思い出してみましょう。ここで、Rは抵抗、Iは電流です。この電流と抵抗の単純な関係に基づくと、同じ値の抵抗に対し、より低い電流を流せば、より少ない電力損失となり、より高い効率につながります。

オープン・ラック・アーキテクチャーにおいて、同じ量の電力が12Vバスラインを通してサーバーラックに供給される時と48Vバスラインを通して供給される時の電力損失を考えてみましょう。48Vバスラインを通過する電流は、12Vバスラインを通過する電流の1/4しかありません。したがって、48Vバスラインと12Vバスラインの抵抗が同レベルであると仮定すると、48Vバスは12Vバスの1/16の電力しか損失がありません。

参照リンク:

第2章: ハーフブリッジDC-DCコンバーターを使用したオープンラック

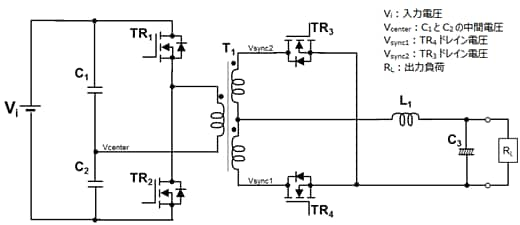

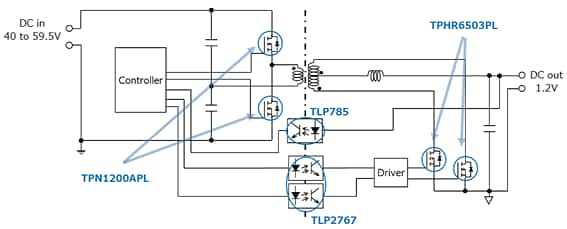

理論を踏まえたオープン・ラック・アーキテクチャーの実現のため、図2に示すようなハーフブリッジDC-DCコンバーターの採用を考察します。このようなコンバーターは、48Vのバスライン電圧を効率的に1.2Vに降圧することができ、システムの総消費電力を削減します。

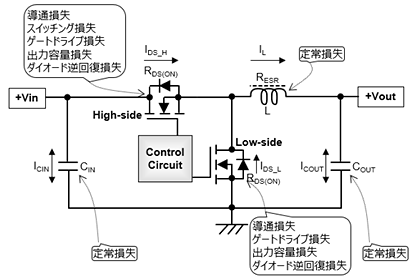

ハーフブリッジDC-DCコンバーター上のMOSFET動作に起因する損失は、スイッチング損失に加え、ゲートドライブ損失、出力容量損失、ダイオード逆回復損失、導通損失があり、これらすべてがDC-DCコンバーターの効率に影響を与えます。

ここで単純化のために、MOSFET二つで構成される図3に示す非絶縁型降圧DC-DCコンバーターに置き換えてこれら損失を考えます。ハーフブリッジDC-DCコンバーターの損失を考える場合は、図3のHigh-side MOSFETを図2の1次側素子 (TR1、TR2) に、図3のLow-side MOSFETを図2の2次側素子 (TR3、TR4) に置き換えてください。

非絶縁型降圧DC-DCコンバーターの各MOSFETには図3に示した損失が発生します。これらの損失は、適切なMOSFETを選択することで大幅に削減できます。

第3章: 当社のアプローチ

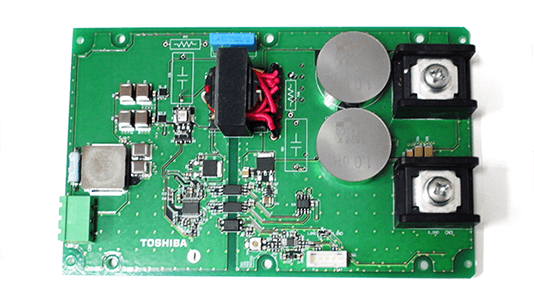

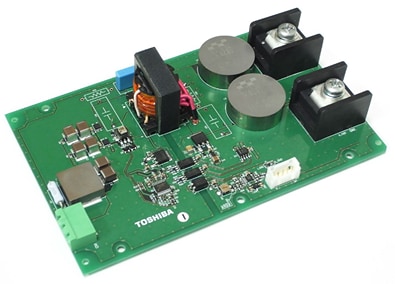

当社は、図4に示す48VバスラインをサポートするハーフブリッジDC-DCコンバーターのリファレンスデザインを開発し、48Vバスシステムで最高の効率レベルを達成するために必要とされる、効果的で実用的なMOSFETについて検討してみました。

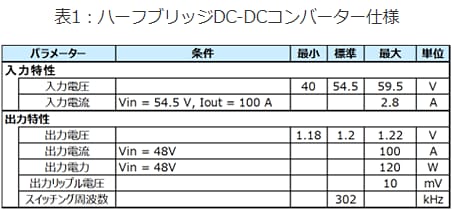

このハーフブリッジDC-DCコンバーターの仕様を表1に、ブロック図を図5に示します。

適切なMOSFETを選択することで、わずか160mm×100mmの基板サイズにて、トータル効率92.8% (Vin=54.5V、30%負荷時) を達成しました。

1次側で影響が大きいスイッチング損失の観点では入力容量が小さいMOSFETが優位ですが、最大負荷時には平均で3A程度の電流が流れるため定常損失の影響も無視できません。そこで、入力容量とオン抵抗のバランスに優れたTPN1200APLを採用しました。

2次側はMOSFETがオンする前に内蔵ダイオードが動作するためスイッチング損失の発生は非常に小さく、導通損失の占める影響が支配的です。従って、当社ラインアップの中で0.41mΩと最もオン抵抗の小さいTPHR6503PLを採用しました。

第4章: 消費電力削減のまとめ

OCPが提案するオープン・ラック・アーキテクチャーは、48Vバスラインを使用することで消費電力を削減し、効率を高めています。48VバスシステムをサポートするハーフブリッジDC-DCコンバーターは、効率的な実装のためのひとつのアプローチです。

DC-DCコンバーターでは、搭載するMOSFETを慎重に選択する必要があります。そこで当社が設計した小型で高効率のDC-DCコンバーターリファレンスデザインでは、1次側にTPN1200APL、2次側にTPHR6503PLというMOSFETを採用しています。

当社では、VDSSが30Vから250Vまでの高品質で高効率なMOSFETをラインアップしており、さらにVDSSクラスごとにさまざまなオン抵抗タイプを用意しています。DC-DCコンバーター設計の際は、ぜひ当社MOSFETをご検討ください。

参照リンク:

本記事の製品、ブロック図、基板情報、使用方法などより詳しい情報を以下よりご覧いただけます。

PDFをダウンロード

以下ボタンから本記事をPDFでダウンロードできます。