-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

静電気保護用ダイオード(ESD保護ダイオード)基板設計上の注意点はありますか?

静電気放電(ESD)は非常に短い時間で印加されるパルスです。高周波であることを意識して基板設計を行わないと性能を十分に発揮できません。ここでは気を付けるべきポイントを説明します。

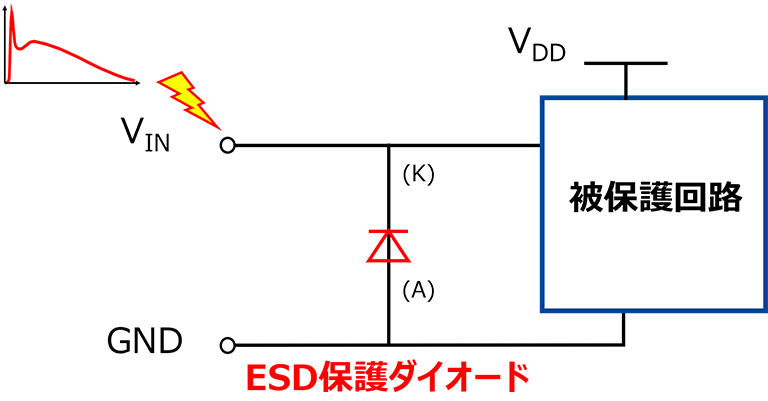

静電気放電(ESD)対策としてESD保護ダイオードが良く使用されます。ESD保護ダイオードはESD侵入時に低抵抗で素早くオンし、ESDなどの異常な入力から被保護素子を守るデバイスとして知られています。

他の保護デバイスでも同じことが言えますが、素子の配置やパターン設計など基板設計でいくつかの点にご注意いただくことがあります。詳しい説明は後に述べますが、基板設計に対しては以下の点に注意して設計ください。

- ESD保護素子をできるだけコネクターの近くに配置(L1/L3のパターンをできるだけ短くする)

- 保護素子分岐後のL2を短くする。 VIAホールはインダクタンスが大きいので用いない。

- ICとESD侵入口(コネクターなど)を接続するGNDインピーダンスは低くする(L5)

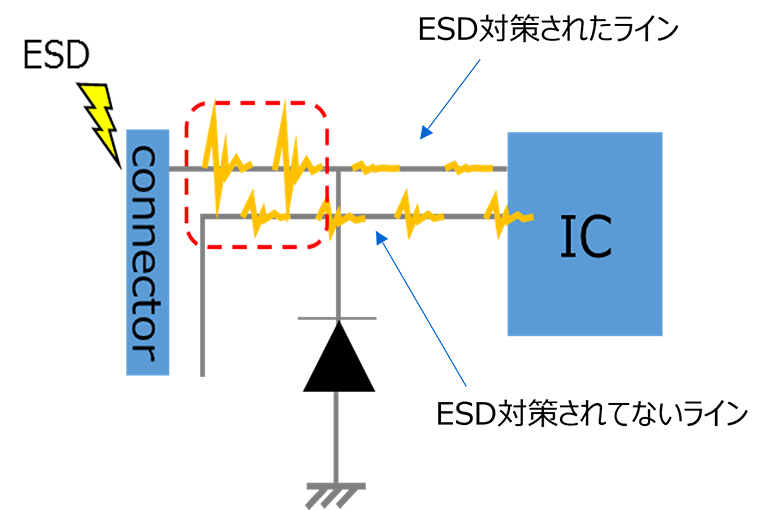

- ESD侵入口(コネクターなど)に接続されたESD対策のされたラインと対策されていないラインを並走させない。特にESD侵入口からESD保護素子が接続された部分までの間のラインの並走に注意が必要です。(図-6)

ESD保護ダイオードはツェナーダイオードとして知られるダイオードと同様にpn接合ダイオードの逆バイアス特性を利用したダイオードです。pn接合ダイオードに逆バイアスを印加すると、ある一定の電圧(降伏電圧 VR)でなだれ降伏(アバランシェ降伏)が生じます。この特性を利用し、ESDなどの異常電圧が侵入したときにのみ素早くオンし、ESDによる被保護素子に加えられるエネルギーを軽減しています。

当社のESD保護ダイオードは長年培われたツェナーダイオードの技術をESD保護に対し最適化し、低容量で低ダイナミック抵抗(動的抵抗)を実現しています。

図-1はESD保護ダイオードの挿入例です。ESDはUSBコネクターやHDMI端子などの外部に露出した端子から主に侵入します。従って、これらI/O端子に接続されている信号ラインや制御ラインとGND間に挿入します。ESDが侵入したときの電圧をVESDとすると、この電圧が被保護回路とESD保護回路に印加されます。被保護回路のESD侵入時の電流IProtは内部回路にもよりますが、VESDが高ければ大きく、低ければ小さくなります。ESD侵入により被保護回路は劣化・破壊することがありますが、この原因は電圧・電流・エネルギーなどケースバイケースです。いずれにしてもVESDが小さいことが守る性能を高めることになります。

VESDを小さくするためにはクランプ電圧VCが低く、ダイナミック抵抗(動的抵抗)RDYNの小さいデバイスを選択することが重要です。

クランプ電圧・ダイナミック抵抗に関しては

FAQ:“静電気対策に使用されるESD保護ダイオードはどのように動作しますか?”、“静電気保護用ダイオード(ESD保護ダイオード)の選択方法について教えてください。”を参照ください。

静電気対策に使用されるESD保護ダイオードはどのように動作しますか?

静電気保護用ダイオード(ESD保護ダイオード)の選択方法について教えてください。

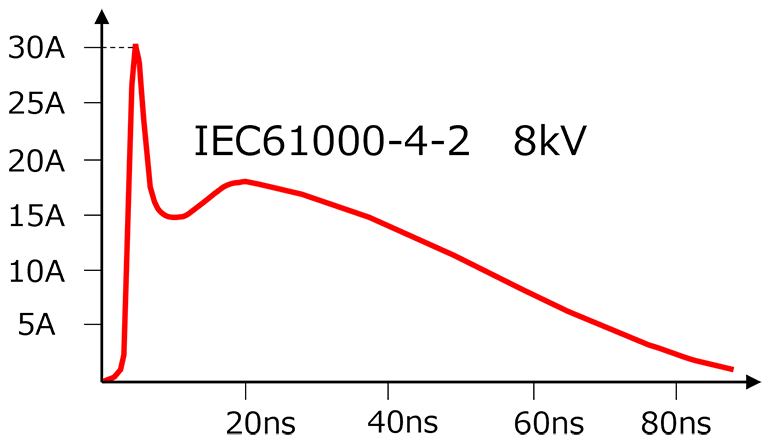

しかしながら、最適なデバイスを選択しても終わりではありません。この考え方は直流では問題ありませんが、高周波では不足です。ご存知のように静電気放電(ESD)は高周波的なパルスです。例えば、ESD試験として知られるIEC 61000-4-2の試験波形例を図に示します。

このような高周波のパルスに対しては、基板設計が重要です。配線(パターン)やVIAホール(スルーホール)はインダクタンスとして働きます。従って、想定されるESD侵入口(コネクターなど)に対し、ESD保護ダイオードはできるだけ短い配線でVIAホールを経由しないで接続する必要があります。

また、忘れがちなのですが、GNDはできるだけインピーダンスの低い(太い)配線で接続しなければなりません。ここで少し図を用いて説明します。

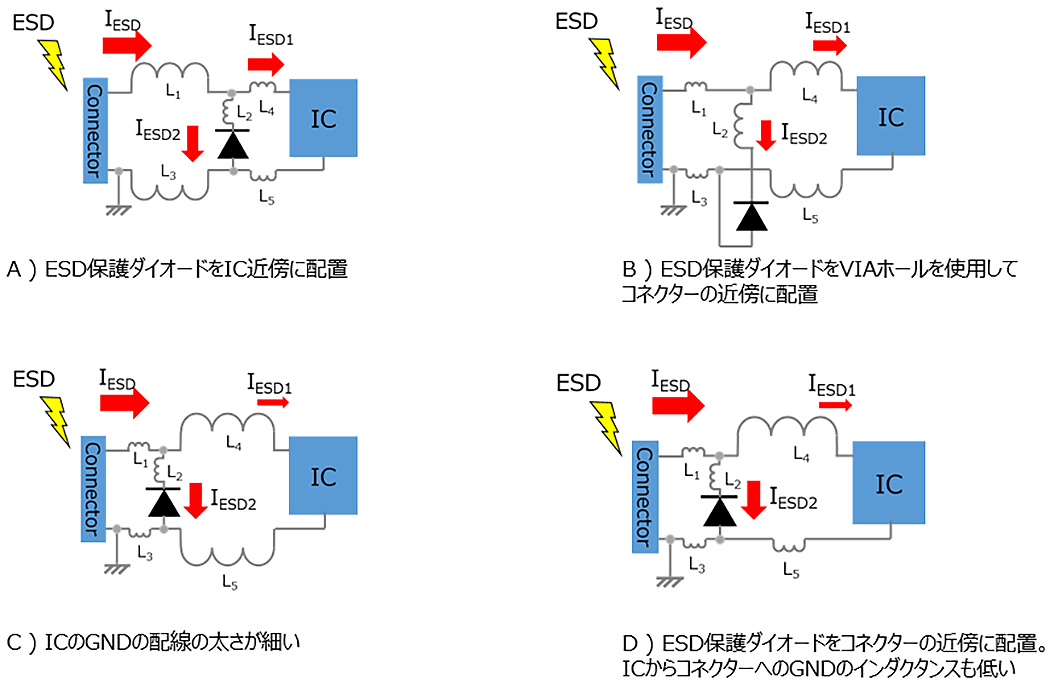

ESD保護ダイオードの配置として、4つのタイプを考えます。

A)ESD保護ダイオードをIC近傍に配置

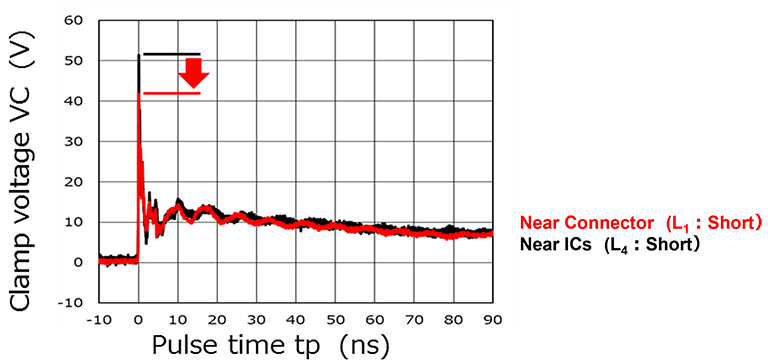

ESD保護ダイオードとICに対する配線インピーダンスはほぼ同じです。侵入した高周波のESDパルスはインダクタンスの影響を受けてESD保護ダイオードとICに印加されます。インダクタンスの影響でパルスの立ち上がりがなまりESD保護ダイオードのオンが若干遅くなります。IC近傍に配置した場合とコネクター近傍に配置した場合、図-3に示すように当社の測定では侵入直後のIC端の電圧(1st Peak Voltage)が異なっています。

B)ESD保護ダイオードをVIAホールを使用してコネクターの近傍に配置

VIAホールの大きさや数にもよりますが、ESD保護ダイオードまでの配線を伸ばすことと等価になります。可能な限りVIAホールは用いない方が得策です。

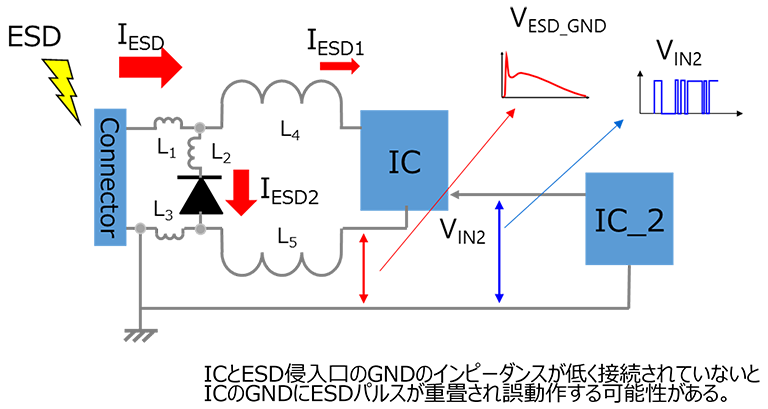

C)ESD保護ダイオードをコネクターの近傍に配置しているが、ICのGNDからコネクターGNDへのインダクタンスが高いL1とL3によるESDパルスの立ち上がりの問題はありません。ただし、L5が大きい場合、誤動作する可能性があります。図-4に示すように、ESDが侵入したときESD保護ダイオードによるクランプ電圧がL4とL5、ICのESD印加時の入力インピーダンスZICによって分圧されます。このためICのGNDはこのL5による分圧分変動することになります。このICにESDの影響を受けていないIC_2から信号 VIN2 が入力されている場合、VIN2はICのGNDを基準でみると VIN2-VESD_GNDとなり誤動作する可能性があります。ESD侵入口からDUPまでのGNDのインピーダンスは、この影響を受けないように十分に低い必要があります。

D)ESD保護ダイオードをコネクターの近傍に配置。ICからコネクターへのGNDのインダクタンスも低い。理想的な配置です。

これ以外にも、図-6に示すようにESD対策されていない弱ESDラインをコネクターに接続されたラインに並走させることは危険です。容量結合や電磁誘導によりESDが重畳し、劣化・破壊を招くことがあります。

関連リンク

TVSダイオード (ESD保護用ダイオード) の製品ラインアップについては、以下のページ、ドキュメントをご参照ください。

* HDMI、HDMI High-Definition Multimedia Interface、およびHDMIロゴは、米国およびその他の国におけるHDMI Licensing Administrator, Inc.の商標または登録商標です。

* その他の社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。