-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

静電気保護用ダイオード(ESD保護ダイオード)の選択方法について教えてください。

一般的なインターフェースでESD保護ダイオードを選択する場合、以下の2つの側面から考える必要があります。ここでは選択方法の概要を記します。詳しい説明は後述します。

1.ESDなどの侵入などなく機器として正常動作しているとき

ESD保護ダイオードは何の仕事もしていないので、信号に影響を与えないことが重要です。

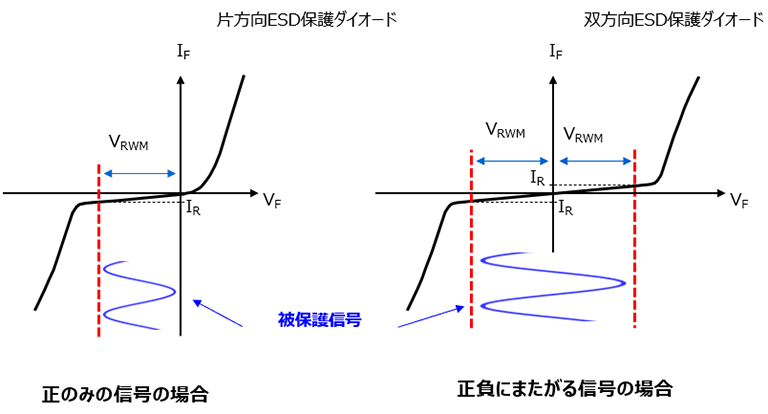

- 信号の最大値より高いピーク逆動作電圧 VRWM の製品を選択

- 信号が正の極性のみであれば片方向タイプ、正負にまたがる信号であれば双方向タイプを選択

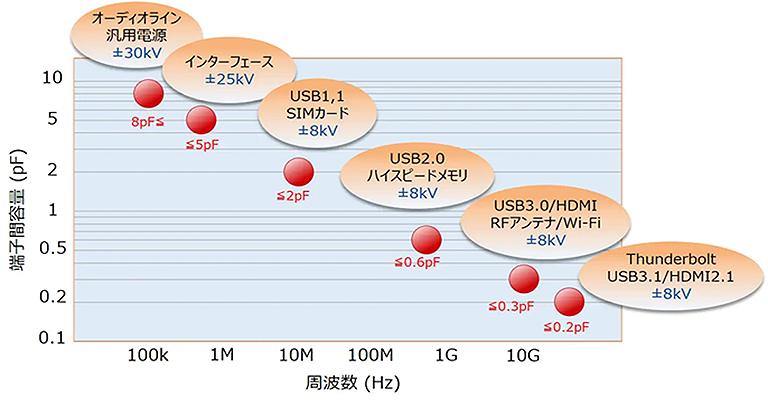

- 信号の周波数に合わせた端子間容量CTのデバイスを選択

2.ESDなどの異常電圧・異常電流の侵入を受けたとき

被保護回路に侵入するESDエネルギーを被保護回路が破壊しないレベルまで小さくすることが重要です。

- クランプ電圧VCの低いデバイスを選択

- ダイナミック抵抗(動的抵抗)RDYNの低いデバイスを選択

正イオン・負イオンになりやすい傾向を示す帯電列の離れた異種の物質が摩擦など密着接触させると、電子が移動し移動先は負電荷、移動元は正電荷に帯電蓄積します。

(FAQ:“静電気放電(ESD : Electrostatic Discharge)とは何ですか?” を参照ください)

静電気放電(ESD : Electrostatic Discharge)とは何ですか?

この電荷が蓄積した物質が、機器のコネクターなどに接触すると、帯電した電荷が瞬時に電流パルスとして流れ出します。この現象を静電気放電(Electro Static Discharge: ESD)と呼びます。

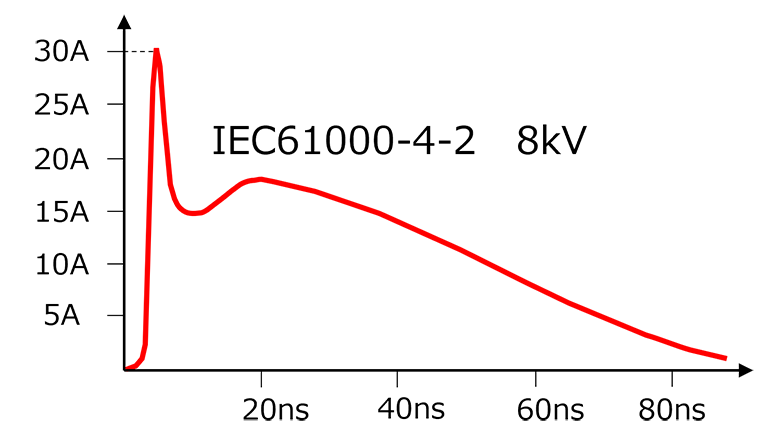

この現象はコンデンサーの放電によく似ています。ESDのシミュレーション波形として良く知られている IEC 61000-4-2 の試験波形を図-1に示します。立ち上がりから1 ns程度の短時間で30 Aに電流が急増しています。

実際にはESD送出側の出力インピーダンス(物質の持つ比抵抗)、異常電圧侵入時の受け側の入力インピーダンスによって大きく変わりますが、通常時の電流・電圧をはるかに上回るエネルギーが流入することになります。これにより機器内部の素子の劣化・破壊などが生じることがあります。

破壊のモードにはいくつかあります。半導体での破壊の例として以下のようなものがあります。

- 高電圧: 絶縁膜の絶縁破壊強度を超える電圧が印加されパンチスルーが生じショート

- 高電流: 半導体中の抵抗・配線などに高電流が流れ込み融解してOpen

- 高電圧・高電流の複合: ESDのエネルギーによりpnジャンクションが破壊されショート

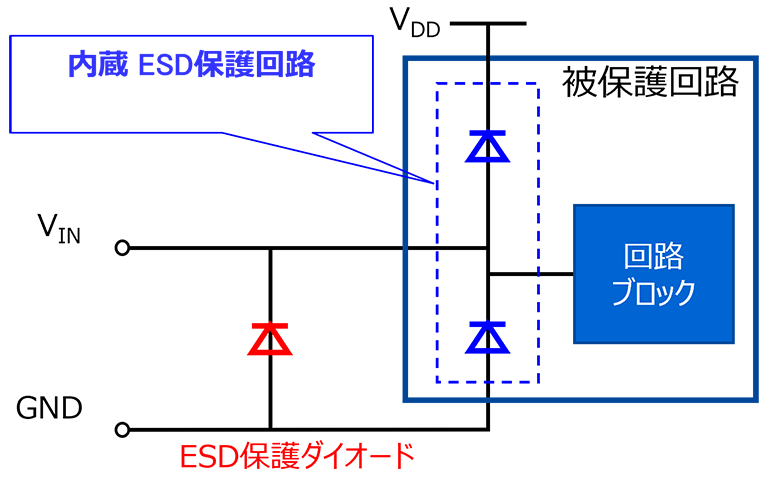

一般的にESD耐性の低い部品ではESD保護回路を内蔵しています。この回路の目的は製造現場におけるESD保護です。従って、静電気が管理された環境下におけるESD(デバイスレベルのESD)を想定しています。日常生活で問題となるESD(システムレベルのESD)はこれよりエネルギーが大きく、対応できていないことがほとんどです。(デバイスレベルとシステムレベルの説明はFAQ:“ESD(Electrostatic Discharge)試験とはどのようなものですか?”を参照ください)

ESD(Electrostatic Discharge)試験とはどのようなものですか?

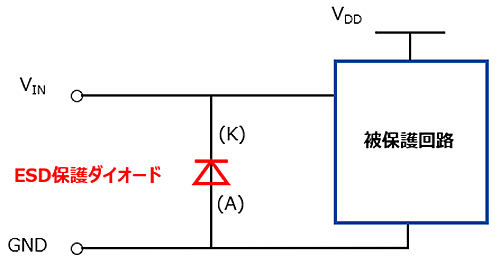

このため、製品設計ではESD侵入口となるコネクターやタッチセンサーなど外部に露出したI/O端子やアンテナなどに接続された信号線 VIN では図-2 のように外付けのESD保護ダイオードを信号線とGND間に挿入します。

ESD保護ダイオードは入っていれば良いというわけではありません。被保護回路の信号や回路などの状態に合わせて選択する必要があります。また、選択したESD保護ダイオードの保護性能を十分に生かすためには配置も最適化する必要があります。配置に関してはFAQ:“静電気保護用ダイオード(ESD保護ダイオード)基板設計上の注意点はありますか?”をご覧ください。

静電気保護用ダイオード(ESD保護ダイオード)基板設計上の注意点はありますか?

文頭に記載した以下の2つの側面からESD保護ダイオードに求められる特性を説明します。

- ESDなどの侵入などなく機器として正常動作しているとき

- ESDなどの侵入を受けたとき

- ESDなどの侵入などなく機器として正常動作しているとき

ESD保護ダイオードが接続されている信号・制御ラインの信号品質が劣化しないことが重要です。ESD保護ダイオードはオフの状態であり、オープン(インピーダンスが無限大)が理想的ですが、少し異なります。

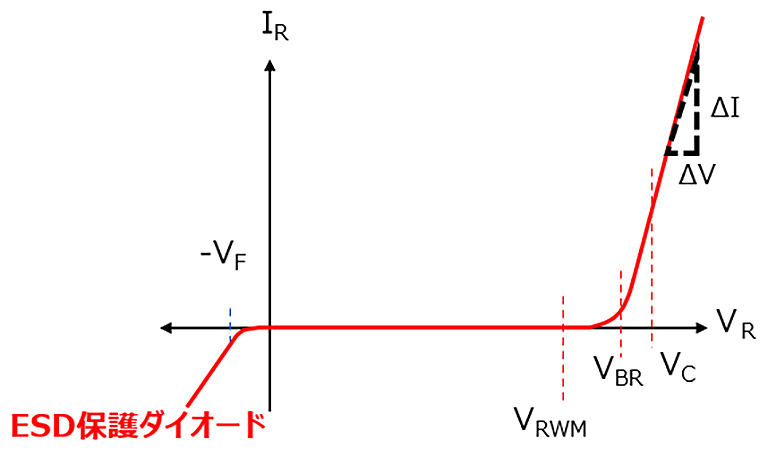

ESD保護ダイオードはpn接合ダイオード(ツェナーダイオード)を基本としています。このためオフ時でもわずかながらリーク電流(逆電流 IR)があります。この電流はブレークダウン電圧 VBR(ツェナー電圧)に近づくほど大きくなり、要求仕様によっては問題になることがあります。

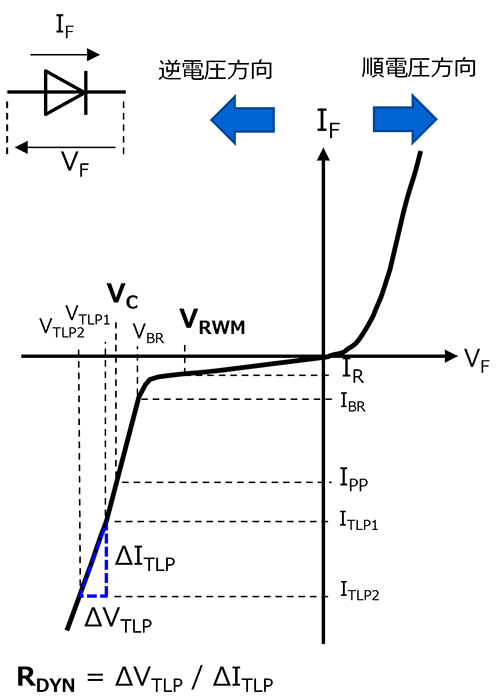

この逆電流は図-3に示すように、IRは規定の逆電圧を加えたときに流れる電流で、製品によって異なります(0.05 μA~2.5 μA)。ESD保護ダイオードでは規定の電圧をピーク逆動作電圧 VRWM と呼びます。仮にICの出力に47 kΩのプルアップ抵抗が存在した場合、2.5uAの製品では118 mVの影響があります。このVRWMより大きな電圧が加わると指数関数的に電流が増加します。従って、被保護信号の最大値はVRWMより低くなければなりません。

被保護信号が正と負にまたがる場合は、双方向タイプを選択する必要があります。この場合、被保護信号の最大値と最小値の値がVRWMより低くなるように選択してください。(双方向のタイプに関して、以下のFAQに説明があります。)

FAQ: プラス/マイナス両極のESDに対応するのですが双方向のTVSダイオード(ESD保護ダイオード)を選択する必要がありますか?

またpn接合では、オフ状態で接合部分に空乏層があります。これが外部から容量(キャパシタンス)として見えます。従って、ESD保護ダイオードではこれら空乏層容量と寄生容量を合わせて、端子間容量(CT)と定義しています。ESD保護ダイオードが接続されている被保護信号の周波数が高い場合、CTの低いものを選択する必要があります。選択の目安として、図-5信号周波数に対する端子間容量選択の目安 を示します。参考にしてください。

空乏層容量に関しては、以下のe-ラーニングに説明があります。

e-ラーニング: 可変容量ダイオード

2. ESDなどの侵入を受けたとき

ESDが侵入したときにオンして電圧をクランプし、被保護回路に印加される電圧下げることが重要です。このためには、すでに説明した正常時の動作におけるVRWMによる制限を加味しつつクランプ電圧VCの低い製品を選択する必要があります。

ICなどでの動作状態に関して少し説明します。

すでに述べていますが、ESD耐性の低い製品ではESD保護回路を内蔵しています。保護回路の一例を図-6に示します。この回路はpn接合ダイオード2個で構成されています。

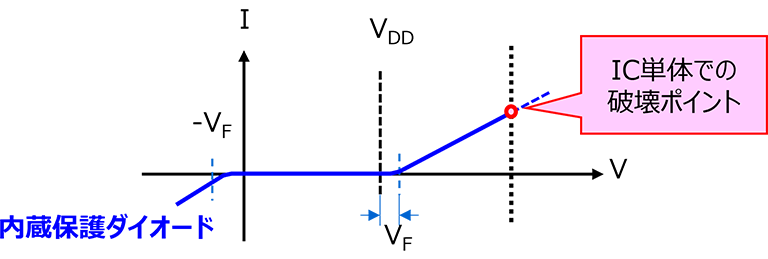

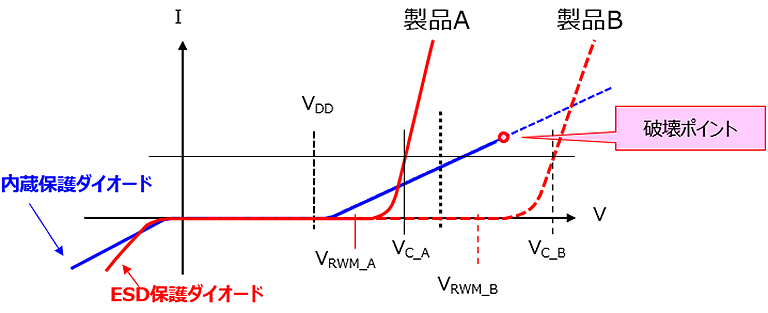

図-7に示すようにVINに入力した信号やESDの電圧レベルが ICの電源電圧VDD+順方向電圧VFより高くなる、またはGNDよりVF低くなるとオンし入力電圧をクランプします。この保護回路はデバイスレベルの保護を目的としているので、これを超えるESDなどが侵入するとICは劣化・破壊する可能性があります。右側の波形上の赤丸の点は許容レベルを上回るESDなどが侵入したときの破壊ポイントです。

ESD保護ダイオードのI-V特性を図-8に示します(注: IC内蔵の保護ダイオードに合わせ、この図ではESD保護ダイオードにとっての逆方向VRを正に描いています)。VR方向は逆方向降伏電圧VBRでオンし始めます。順電圧方向VFは順方向電圧VFでオンし始めます。

IC内蔵の保護回路と異なる点は、順方向・逆方向とも波形の傾きが急峻、つまり動的抵抗(ダイナミック抵抗)RDYNが低いことです。この抵抗値が低いことは電流によるクランプ電圧が動きにくいことを意味します。電圧が動きにくいので、大きなエネルギーを持つESDが侵入しても被保護回路に印加される電圧が大きく変わらない(=保護性能が変わらない)ことになります。

ダイナミック抵抗が低いことは、VR方向はツェナー降伏(またはアバランシェ降伏)であることが理由の1つですが、これ以外にもジャンクション面積が広いこと、またプロセスで急峻になるように合わせこんでいることがあげられます。

ESD保護ダイオードのクランプ電圧に関して考えます。

保護するラインの信号レベルは0 V ~ VDDとします。従って、ESD保護ダイオードのVRWMはVDD<VRWMです。この条件を満たすクランプ電圧VCの異なる2つの製品(製品Aと製品B)を考えます。製品Aのクランプ電圧VC_A<製品Bのクランプ電圧VC_Bの関係とします。ESDが侵入した直後、内蔵のESD回路とESD保護回路はともにオンします。このオンしたときの電圧(保護ラインの電圧)は主にESD保護ダイオードで決まります。

製品Bは明らかに破壊ポイントを超える電圧・電流でオンすることになります。これではICを守ることができません。

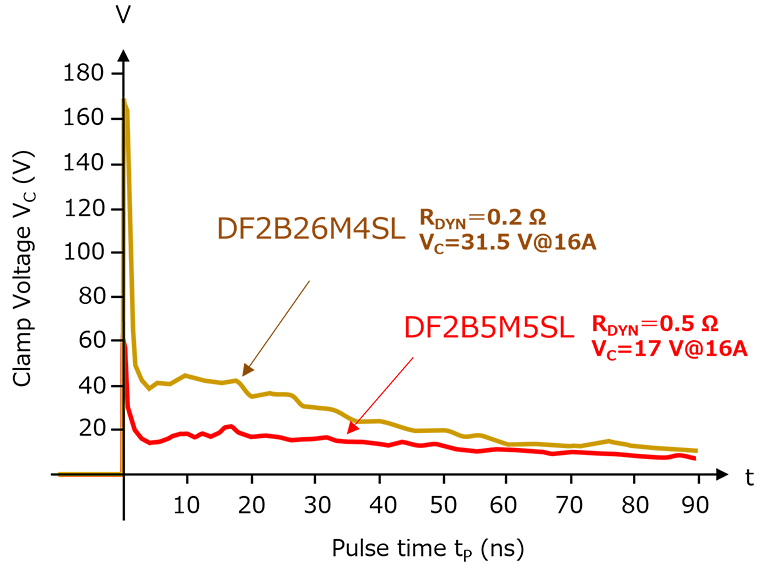

クランプ電圧の異なる2つの製品のESDクランプ波形(単体)を図-10に示します。

クランプ電圧はできるだけ低い製品を選択することによってシステムの安全性を増すことができます。

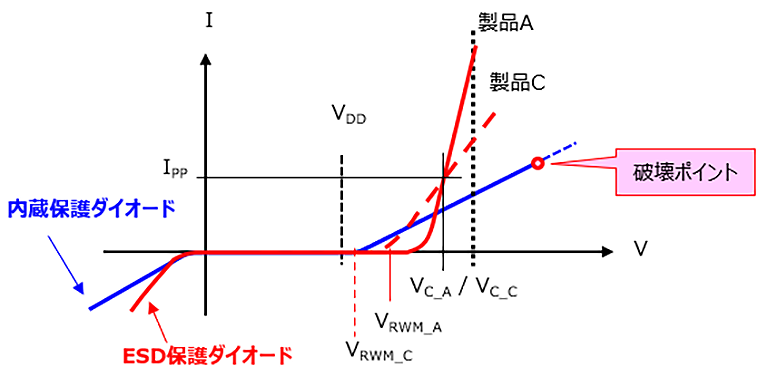

次にクランプ電圧が同じで、ダイナミック抵抗RDYNが異なる2つの製品(製品Aと製品C)について考えます。

RDYN_A < RDYN_C です。

図-11を見て分かるように、高電流領域(クランプ電圧VCより高い領域)では常に、同じ電圧であれば多くの電流がESD保護ダイオードに流れ(内蔵保護ダイオードに流れる電流が少なく流れ)、同じ電流であれば内蔵保護ダイオード端( ESD保護ダイオード端)の電圧が低くなります。このことは、ESDによるICへのストレスが減少することを意味します。従って、同じクランプ電圧であればダイナミック抵抗の低いデバイスを選択することが重要となります。

関連リンク

TVSダイオード (ESD保護用ダイオード) の製品ラインアップについては、以下のページ、ドキュメントをご参照ください。