-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

静電気対策に使用されるESD保護ダイオードはどのように動作しますか?

ESD保護ダイオードはツェナー電圧を超えるESDなどのパルスが侵入したときに、低インピーダンスで素早くオンしてICを守る素子です。この用途に最もよく使用されているESD保護ダイオードの動作を説明します。

スマートフォンをはじめとする移動体機器・IoT機器の普及により、機器へUSBやライトニングケーブルなどを着脱する機会が増加しています。これに伴い、静電気放電(ESD)が機器に印加される可能性も増加し、静電気に対するシステムレベルでの対策が従来以上に重要になっています。

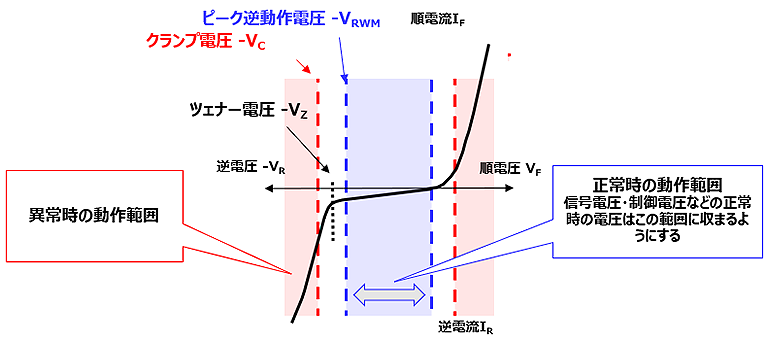

ESD保護ダイオードはpn接合ダイオードのツェナー降伏*を利用した保護素子です。pn接合ダイオードは図に示すように、順バイアスでは約0.7 Vでオン、逆バイアスでは素子ごとに固有の電圧(ツェナー電圧VZ)でオンします。この逆バイアスでの特性を利用したものがESD保護ダイオードです。

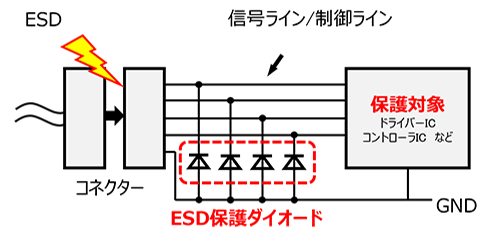

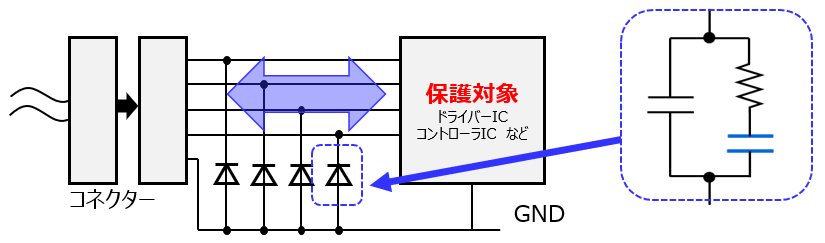

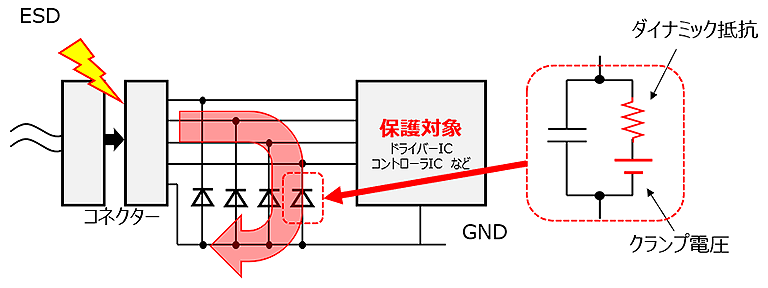

ESD保護ダイオードは信号ラインや制御ラインなどに対し、保護対象とESD侵入口であるコネクターなどの間に図のように接続されます。ESD保護ダイオードでは逆バイアス時の電圧の定義として、ツェナー電圧 VZ以外にピーク逆動作電圧 VRWMが定義されています。VZはオンする最小電圧、VRWMはオフ状態を保つ最大電圧です。ESD保護ダイオードは逆バイアス状態で接続されているので、接続したラインの電圧VINがGNDに対し GND < VIN ≦ VRWM であれば、ESD保護ダイオードはオンしないということになります。

ここで回路が正常に動作しているときとESDなどの異常な電圧が侵入したときの動作を考えます。

通常時の動作では、ESD保護ダイオードはオフの状態にあります。

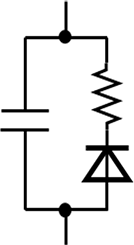

ただし、pn接合ジャンクション面に発生する空乏層などにより端子間容量CTを持つコンデンサーとなります。製品によりこの値は異なり、小さいものでは0.1 pF程度の製品もあります。

ESDなどの異常電圧が印加されると、ESD保護ダイオードはオンの状態になります。

このときESD保護ダイオードは電圧源と微小なダイナミック抵抗(動的抵抗)RDYNを持つ素子として考えることができます。電圧源は印加電圧がダイオードに対し順方向の場合、順電圧VF、逆方向の場合、クランプ電圧VC(大電流で定義されるツェナー電圧)です。

このようにオフ時はコンデンサー、オン時は電圧源と微小抵抗として動作します。扱う信号が高周波の時は端子間容量にも注意して選択する必要があります。

オン時の微小抵抗(ダイナミック抵抗 RDYN)について考えます。

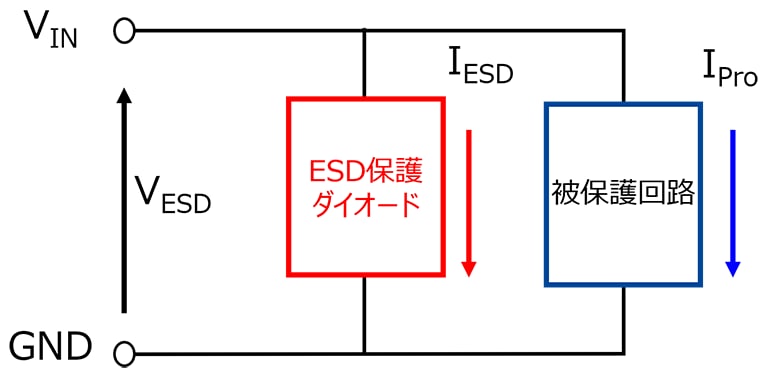

ESDなどの異常電圧侵入時のもっとも単純な回路構成は以下です。

ESD保護回路は図に示すように、被保護回路に並列に接続されています。従って、ESD保護回路の異常入力侵入時の電圧VESDは被保護回路にも印加されます。(実際にはパターンなどの寄生インダクタンスや寄生容量があるので少し電圧とタイミングが異なることがあります。)また、被保護回路に流れる電流IProは内部にある能動回路の状態に影響されますが、VESDに依存します。

従って、VESDを下げることが被保護回路を守るうえで最も重要なことになります。このVESDはESD保護ダイオードのクランプ電圧に依存します。

図-5のオン時の等価回路を見ると、電圧源(クランプ電圧)に直列に抵抗(ダイナミック抵抗)があります。従って、電流が大きくなるとこの抵抗による電圧降下分がクランプ電圧に加算されることになります。

静電気放電(ESD)は物質に蓄積された電荷が接触などにより放電される現象です(詳しい説明はFAQ:”静電気放電(ESD : Electrostatic Discharge)とは何ですか?”を参照ください)。

静電気放電(ESD : Electrostatic Discharge)とは何ですか?

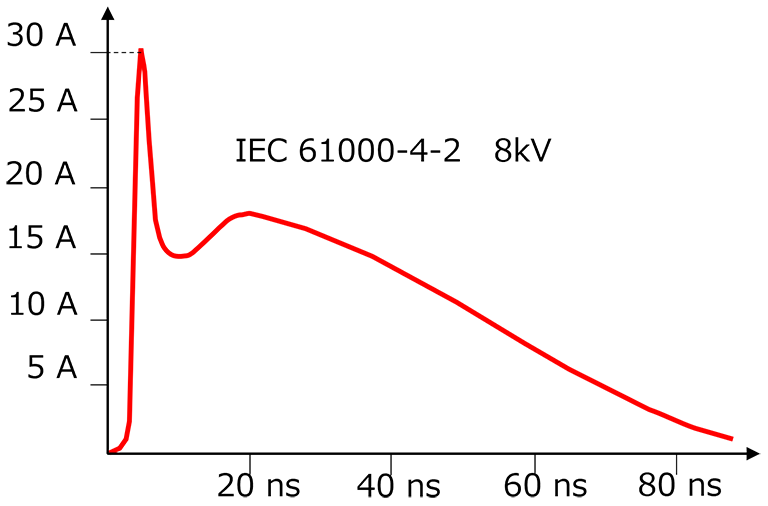

コンデンサーに蓄積された電荷が放電される時のように、接触直後の電流は非常に高い電流です。例えば、ESD試験として知られる図-7に示すIEC 61000-4-2の試験波形ではピーク値は30 Aにもなります。仮にダイナミック抵抗が0.5 Ωだとすると、15 Vの電圧降下が生じます。

従って、ESD保護ダイオードを選択する場合、クランプ電圧が低いだけでなくダイナミック抵抗による電圧降下を考慮し、できるだけ低いものを選択することが保護性能を高める上で重要です。

また、図-7を見て分かるように、ESDのパルスは非常に短時間で印加される高周波のパルスです。このため、ESD保護ダイオードの性能を生かしきるためには、配置や接続するためのパターンにも注意が必要です。

詳しくはFAQ:“TVSダイオード(ESD保護ダイオード)基板設計の注意点”を参照ください。

TVSダイオード(ESD保護ダイオード)基板設計の注意点

* ここではツェナー降伏と呼んでいますが、Si(シリコンの)pnダイオードには逆バイアス印加時の降伏にはツェナー降伏とアバランシェ降伏があります。これらの降伏現象は個々独立して発生するわけでは無く混在しています。5.6V付近を境目に、これ以下ではツェナー降伏が支配的、これ以上ではアバランシェ降伏が支配的に発生すると考えられています。

関連リンク

TVSダイオード (ESD保護用ダイオード) の製品ラインアップについては、以下のページ、ドキュメントをご参照ください。