-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

MOSFETのアバランシェとは何ですか? (アバランシェ耐量)

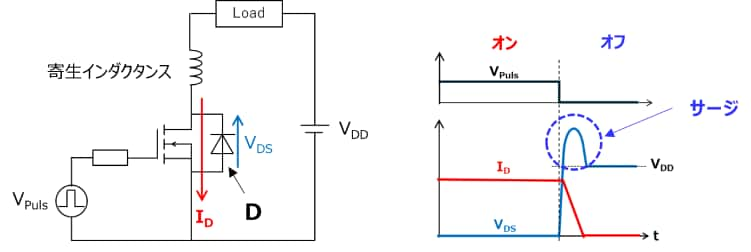

MOSFETのターンオフ時、ドレイン・ソース間にかかる電圧が絶対最大定格VDSSを超えるとアバランシェ降伏が生じます。ドレインのDC電圧が定格内であっても、配線の浮遊インダクタンスなどにより、このDC電圧にサージ電圧が重畳し最大定格を超えることがあります。アバランシェ降伏時には急激に電流が流れ、これによってアバランシェ破壊に至る可能性があります。回路設計時には、アバランシェ耐量を保証している製品もありますが、基本的にはドレインの最大電圧に対して、余裕を持ったドレイン・ソース間電圧VDSSを持つMOSFETを選択してください。また、サージ電圧が発生しないように後述の対策を実施してください。

MOSFETのアバランシェ降伏

MOSFETのターンオフ時、回路内の寄生インダクタンスなどの影響により、ドレイン・ソース間にサージ電圧が発生することがあります (図1参照)。

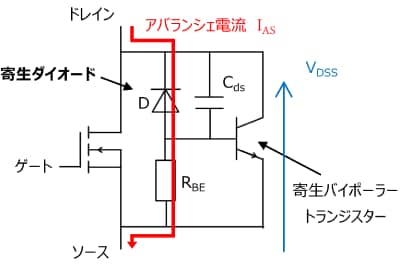

このサージ電圧がMOSFET (図2の等価回路を参照) に逆バイアスとして加わると、内部の寄生ダイオードにあるpn接合の自由電子が加速され、大きな運動エネルギーを持つようになります。加速された電子が原子と衝突すると、新たな自由電子と正孔が生成され (電子–正孔対)、これらもさらに加速されて連鎖的に電子-正孔対を生み出します。このようにして電流が急激に増加し、大きな電流'-アバランシェ電流 (IAS) -が流れる現象を「アバランシェ降伏」と呼びます。

アバランシェ降伏については、以下の資料「2.4 ツェナーダイオード」の項目にも詳しく記載されていますので、ぜひ参考にしてください。

アプリケーションノート: ダイオードの基礎 (ダイオードの種類とその概要) (2.54MB)

アバランシェ破壊

アバランシェ破壊には、大きく分けて熱的破壊と寄生トランジスターによる電流破壊の2つがあります。

1. 熱的破壊

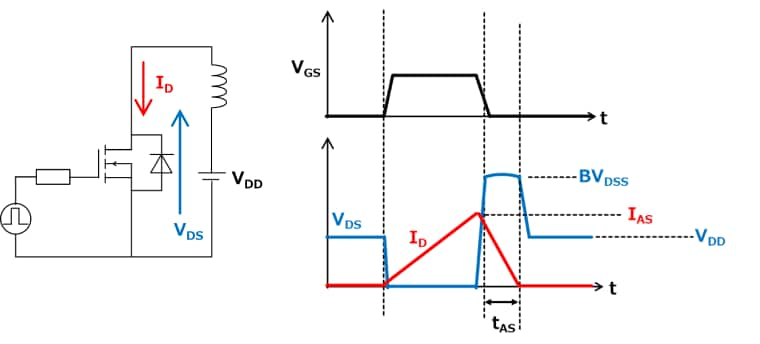

図4に示すアバランシェ測定回路と波形を用いて説明します。この回路では、MOSFETがターンオフする際、インダクタンスLがそれまで流れていた電流を維持しようとします。その結果、Lによる逆起電圧が発生し、ドレイン・ソース間の電圧が定格VDSSを超えると、アバランシェ降伏が発生することがあります。

この降伏期間中には、アバランシェ電流 (IAS) が流れ、MOSFETはこの電流とブレークダウン電圧 (BVDSS) によって電力損失を受けます。この損失により、素子内部のジャンクション温度 (Tj) が上昇し、最悪の場合は破壊に至る可能性があります。

このときに発生する電力損失はアバランシェエネルギー (EAS) と呼ばれ、回路設計上の重要な指標となります。

アバランシェエネルギーは以下で表されます。

![]()

EAS: アバランシェエネルギー IAS: アバランシェ電流 BVDSS: ドレイン・ソース間ブレークダウン電圧 (降伏電圧)

VDD: 電源電圧 tAS: アバランシェ期間 PA: アバランシェ期間の電力 L: インダクタンス

2. 寄生トランジスターによる電流破壊

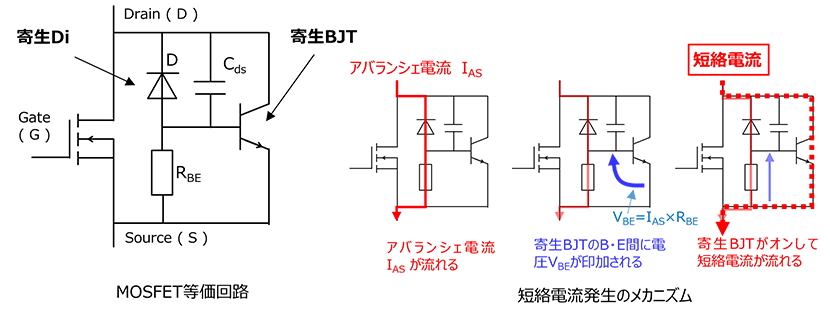

MOSFETのドレイン・ソース間電圧が定格VDSSを超えてアバランシェ降伏が発生すると、図3に示すように、内部の抵抗RBEにアバランシェ電流 (IAS) が流れ込みます。このとき、寄生バイポーラートランジスター (BJT) のベース・エミッター間には、

VBE=IAS×RBE

の電圧がかかります。

このVBEが十分に大きくなると、寄生トランジスターがオン状態になり、大電流 (短絡電流) が流れます。その結果、MOSFETが短絡破壊を起こす可能性があります。

アバランシェ降伏への対策

アバランシェ降伏によるMOSFETの破壊を防ぐために、以下のような対策が有効です。

- 余裕を持った素子の選定

ドレイン・ソース間電圧(VDSS)の最大定格に対して、十分なマージンを持つMOSFETを選択してください。

また、アバランシェ降伏時でも破壊されないよう、単発の電流やエネルギー量 (アバランシェ耐量) を絶対最大定格として保証している製品もあります。以下はその一例です:

| 項目 | 記号 | 定格 | 単位 |

|---|---|---|---|

| アバランシェエネルギー (単発) (注) | EAS | 1049 |

mJ |

| アバランシェ電流 (単発) | IAS | 8.0 | A |

注: アバランシェエネルギー (単発) 印加条件 VDD = 90V、Tch = 25°C (初期)、L = 29mH、IAS = 8.0A

- 配線の浮遊インダクタンスを低減:

電流が流れる配線は、できるだけ短く・太く設計してください。

また、小型パッケージや面実装パッケージを使用することで、リードインダクタンスも抑えられます。 - 外付けゲート抵抗の値を大きくする:

ゲート抵抗を大きくするとスイッチング速度が遅くなり、ドレイン電流の変化率 (di/dt) が小さくなります。

サージ電圧VSは以下の式で表されます。

VS = LS * di/dt

したがって、di/dtを抑えることでサージ電圧も低減できます。

ただし、スイッチング速度が遅くなるとスイッチング損失が増えるため、損失とサージ抑制のバランスを考慮して最適な抵抗値を選定してください。 - スナバ回路やクランプ回路の活用:

これらの回路は、MOSFETがオンからオフに切り替わる際に発生するサージ電圧を吸収・抑制します。

浮遊インダクタンスに蓄積されたエネルギーを安全に処理するために有効です。

関連リンク

製品ラインアップについては、以下のページ、ドキュメントをご参照ください。

パラメトリック検索

MOSFET

FAQ

* このFAQ内で使用している社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。