-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

3-2-2. 通常動作時 (ESDパルス非侵入時) の重要特性②

3-2-2. 保護する信号ラインの周波数に対して、適切な端子間容量Ctを持っているか?

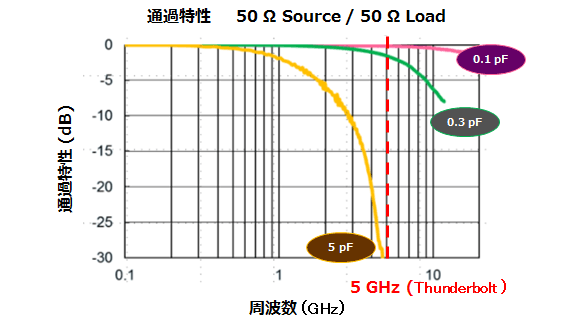

ESD保護用ダイオードの等価回路を図3.3に示します。通常動作時は、ダイオード部分はオフしており図3.3に示すようにpnジャンクション境界面に空乏層が広がっています。この空乏層は電気的にはコンデンサーとして働きます。このため、信号ラインの周波数に対して適切な素子を選択しないと信号品質は低下します。 ESD保護用ダイオードの容量 (端子間容量Ct) が5pF/0.3pF/0.1pF のときの通過特性を図3.4のグラフに示しています。容量が大きい素子に関しては、損失が大きく (数値がマイナスに大きく変動) なっており、使用できる周波数範囲が狭くなります。例えば、Thunderbolt (10Gbps/周波数換算: 5GHz) のポイントをみると、容量の小さい素子 (0.1~0.3pF) は、損失が小さく通過信号への影響が少ないですが、容量の大きい素子 (5pF) は、損失が大きく、通過信号が大幅に減衰してしまっていることが分かります。

端子間容量の低減 (端子間容量: ダイオードの静電容量とパッケージなどの寄生容量による容量で静電容量用が大きいな割合を示します。)

静電容量は逆バイアス時に形成される空乏層により生じます。静電容量に対し空乏層内は少数キャリアーのない、いわば絶縁対のような働きをします。この空乏層は元々の不純物濃度を低くすることで広がります。従ってダイオードの静電容量を低減するにはpn (p: p型半導体、n: n型半導体) 接合の面積を小さくするか逆方向降伏電圧VBRを高くする必要がありますが、どちらの方法も後段のICに対する保護性能が悪化します。ダイオードを直列に接続することで合成静電容量を小さくできること、ダイオードのESD耐量は順方向よりも逆方向の方が低いことを考慮して複数のダイオードを組み合わせること (EAP構造: ESD Diode Array Process) により、保護性能を維持しながら静電容量の低いESD保護用ダイオードを実現しています。

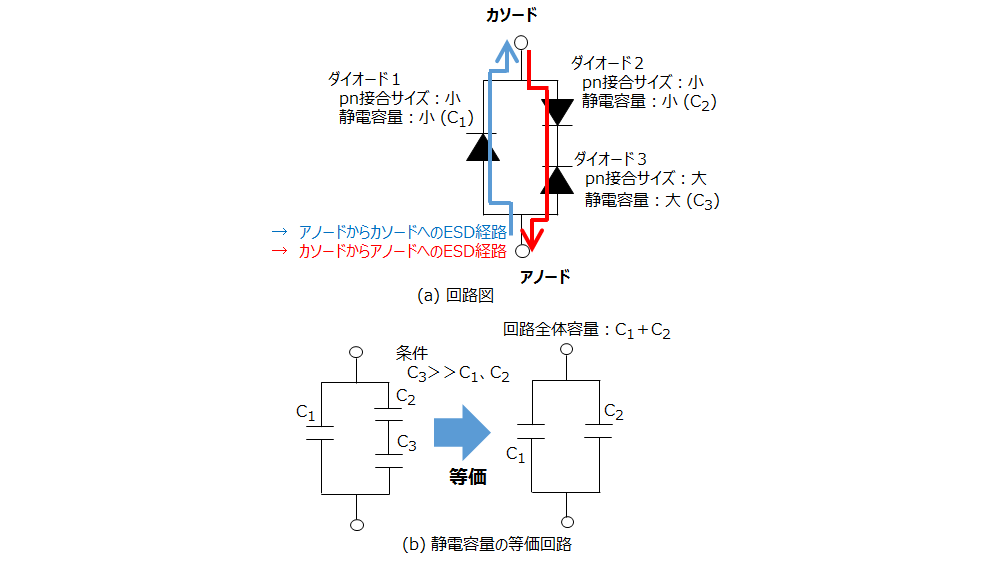

図3.5にEAP構造を使用した低静電容量ESD保護用ダイオードの回路図を示します。回路はpn接合面積が小さく高VBRで低静電容量のダイオード1 (静電容量C1) 及びダイオード2 (C2) とpn接合面積が大きく適切なVBRで静電容量の大きいダイオード3 (C3) の三つのダイオードで構成されています。アノードに印加されるESDは、ダイオード1の順方向に流れ、カソードに印加されるESDはダイオード2の順方向を経由してダイオード1と比較してVBRの低いダイオード3の逆方向に流れます。一般に、ダイオードのESD耐量は順方向よりも逆方向の方が低くダイオード1やダイオード2はpn接合の面積が小さいため更に逆方向のESD耐量は低くなります。しかしEAP構造にすることでダイオード1やダイオード2の逆方向にはESDによる電流が流れません。したがって、回路全体として高いESD耐量を実現できます。図3.5 (b) に、この回路の静電容量等価回路を示します。静電容量の小さいダイオード2と大きいダイオード3を直列に接続することで合成静電容量を小さくできます。また、この回路のVBRの値はダイオード3のVBRで決まるため、保護する信号ラインに合わせたVBRの値に調整することで、保護性能を高めることができます。

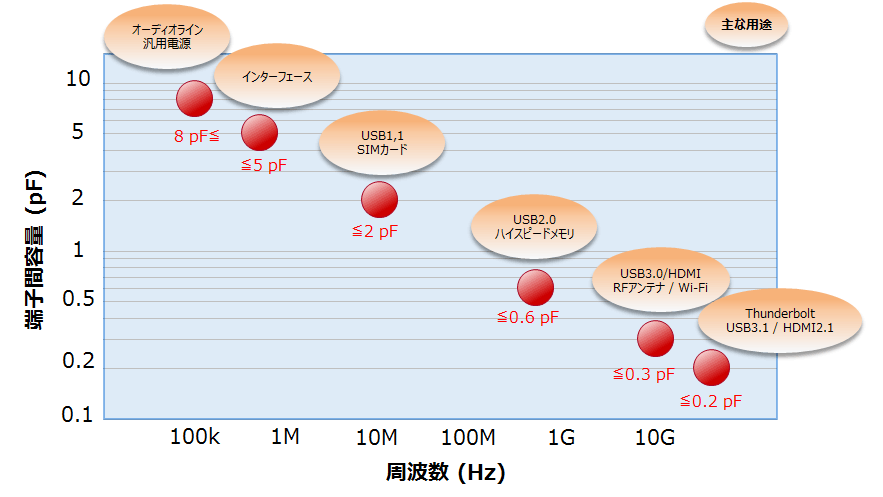

周波数に対する端子間容量の目安

グラフは周波数に対するESD保護用ダイオード選択の目安を示しています。

3. TVSダイオード (ESD保護用ダイオード) の重要特性

関連情報

- 製品ページ

TVSダイオード (ESD保護用ダイオード) - アプリケーションノート

ダイオード - FAQ

TVSダイオード (ESD保護用ダイオード) - TVSダイオード (ESD保護用ダイオード) 全製品のパラメトリックサーチはこちら:

パラメトリックサーチ - 製品の購入はこちら

Stock Check & Purchase