-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

MOSFETを並列に使用する場合、何に注意すればいいですか?

パワーMOSFETを大電力対応やパワーMOSFETのオン抵抗低減による低損失化を目的として、並列接続して使用する場合があります。この場合、素子に電流が均等に流れるようにすることが重要です。もし電流がアンバランス状態になると、一部の素子に過大な電流が流れ、素子を破壊する可能性があります。この電流アンバランスは導通時とスイッチング時の両方を考慮する必要があります。

導通時 (定常状態) のアンバランス対策

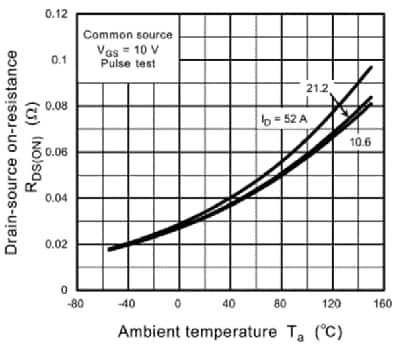

並列接続したデバイスの オン抵抗RDS(on)の差や、基板や配線の抵抗の差によってドレイン電流のアンバランスが生じ、素子の破壊の可能性があります。また、このドレイン電流の差がスイッチング時の電流値や過渡的な損失にも影響を及ぼします。 MOSFETの場合、オン抵抗RDS(on)は正の温度係数 (図1参照) を持ち、温度の上がった素子に流れる電流を抑えるため、発熱条件によるリスクは特別大きくはありません。対策として以下が挙げられます。

- MOSFETの同一ロット製品を使用するなど、RDS(on)のばらつきのないものを使用する。

- 基板のレイアウトを最適化する。 (抵抗成分を合わせる。)

スイッチング時 (過渡状態) のアンバランス対策

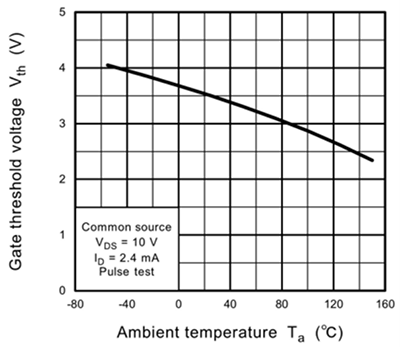

素子がスイッチング時(過渡状態)には、定常状態でのアンバランス要因に加え、並列接続した素子のVthの差や、基板や配線のインダクタンス成分の差によってドレイン電流のアンバランスが生じます。また、Vthは負の温度係数 (図2参照)を持つため、温度が上がった素子のVthはさらに下がります。これによって、更なる電流のアンバランスを生じます。また、並列接続は電流のアンバランスだけでなく発振を招くことがあります。対策として以下が挙げられます。

- MOSFETの同一ロット製品を使用するなど、Vthのばらつきのないものを使用する。

- 基板のレイアウトを最適化する。(抵抗成分・インダクタンス成分を合わせる。)

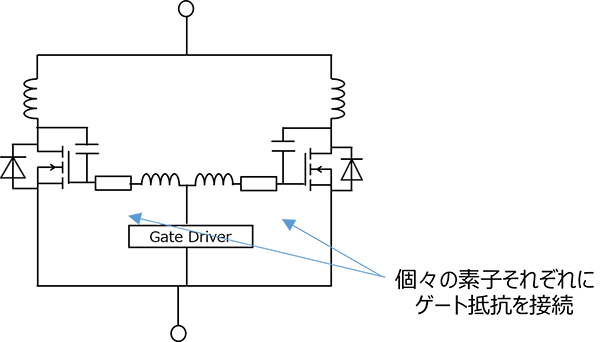

- 発振対策として各MOSFETのゲートに直列抵抗を挿入する。注1(図3)

- 各素子の放熱条件を合わせる。

その他、スイッチング時のオーバーシュートによりMOSFETがブレークダウンすることがあります。この場合、製品のバラつきによりドレイン耐圧の低い素子に全電流が集中し破壊させる可能性があるため注意が必要です。

以下のアプリケーションノートにも発振などの情報があります。参考にしてください。

このようにMOSFETを並列に接続するときには注意が必要です。バイポーラートランジスター(BJT)でも同じことが言えます。定常状態のアンバランスに対しては、BJTに比べるとMOSFETはオン抵抗の温度特性が正であるため熱暴走はしにくいと考えられます。ただし、MOSFETはスイッチング速度が速いため、スイッチング時のアンバランスに対しては、BJTよりも注意が必要です。

注1:パワーMOSFETを単体で使用する場合に比べ、並列接続で使用する場合は寄生発振が起こりやすくなります。また、発振しなくてもゲートに振動波形が見られる場合があります。これは、スイッチング時(特にターンオフ)のドレイン配線インダクタンスによる電圧振動と、ゲート・ドレイン間容量、ゲート配線インダクタンスによる共振回路に起因します。寄生発振は並列接続の各々のMOSFETにゲートに抵抗を接続することで抑制します。この対策はオーバーシュートの対策としても有効です。図3を参照ください。

関連リンク

製品ラインアップについては、以下のページ、ドキュメントをご参照ください。

パラメトリック検索

MOSFET

FAQ

* このFAQ内で使用している社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。