-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

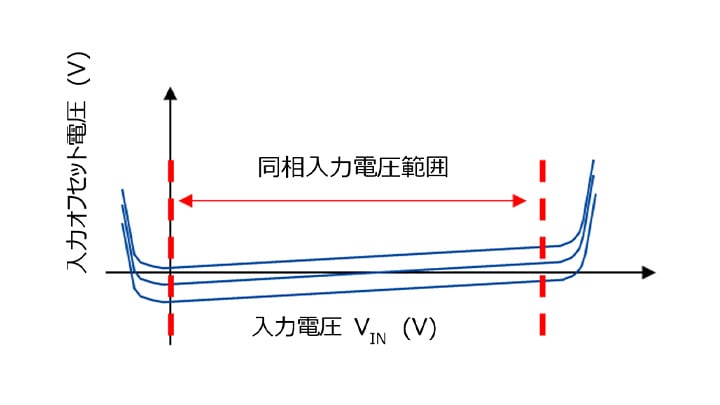

3-3. 同相入力電圧範囲 (CMVIN) / 同相入力信号除去比 (CMRR)

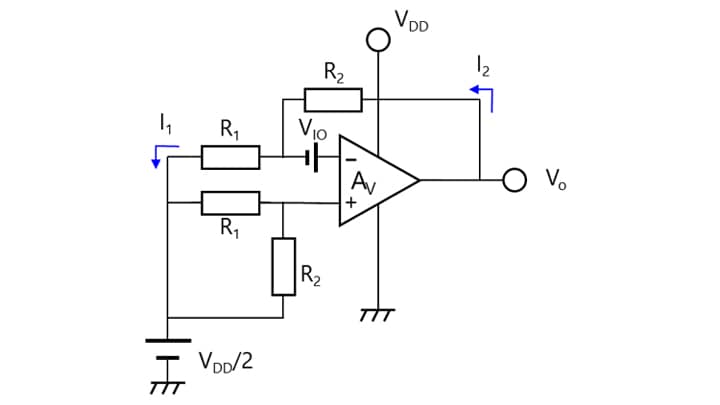

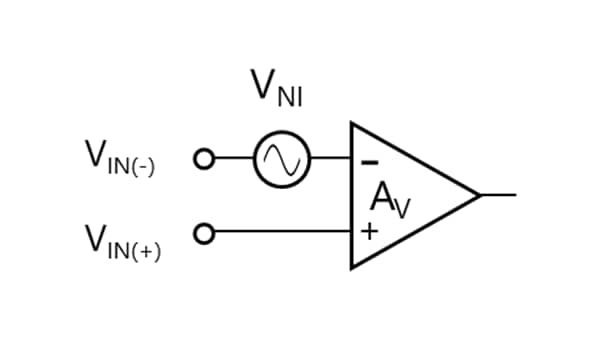

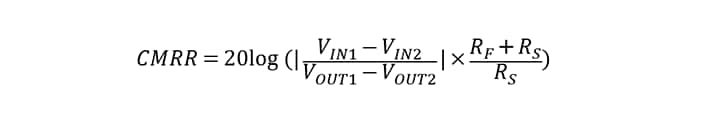

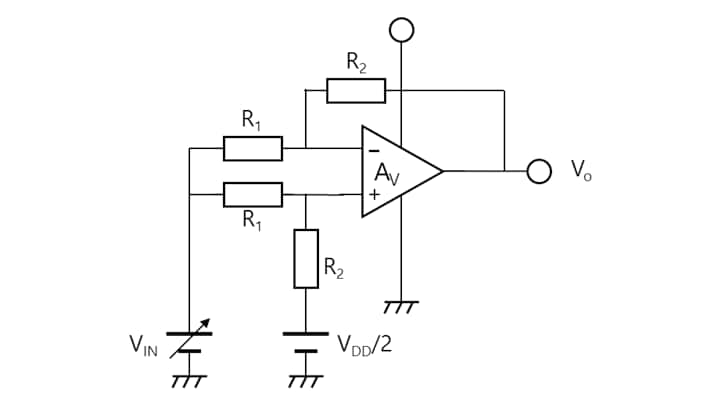

入力信号除去比 (CMRR) とは、差動増幅器で同じ位相、同じ信号レベルの2つの信号やノイズ (同相ノイズ) が入力された場合の除去能力を表す指標で下式で定義しています。図-1に測定回路図を示します。

また、規定の条件下で規定のCMRR値を満足する入力の電圧範囲を同相入力電圧範囲 (CMVIN) としています。東芝オペアンプのデータシートではCMRRをDCで規定しています。

ここで、VIN1とVIN2はCMVINの最大値と最小値、VOUT1とVOUT2はその時の出力VOの値になります。

図 3-5の測定回路図を見てわかるように、3-1項で説明した入力オフセット電圧VIOはCMRRの特殊条件 (VIN = VDD/2) の値になります。

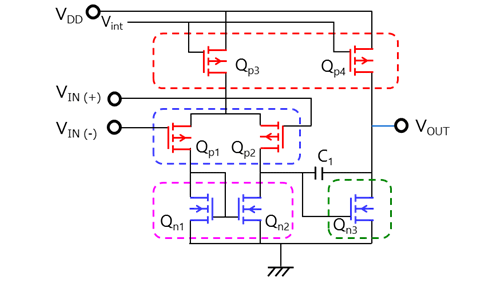

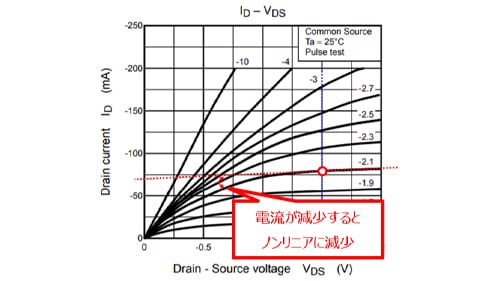

オペアンプは1-2項で説明した動作を行います。一般的なオペアンプは図 3-6に示すように入力段の差動対はPch-MOSFETで構成されています。入力端子VIN(+)とVIN(-)の電圧が上昇すると電流源であるQp3のドレイン・ソース間電圧が減少し差動対とカレントミラーに流れる電流はわずかに減少します。図 3-7はディスクリートのPch-MODFETのID-VDSカーブ例です。IC内部のMOSFETと大きさは大きく異なりますが動作は同じです。仮に初期状態がVDS = -1.5 V、ID = 80 mAにあったとします。電流が減少すると、ID-VDSの変化は飽和領域の範囲内ですが、ノンリニアに変化していきます。

IC内部のMOSFETなどの素子は均一になるように素子配置やプロセスの制御を行っていますが、ミクロ的には完全に一致することはありません。また半導体チップの金属フレームへのマウントや基板にはんだ付けすることによる機械的応力も素子ごとに微妙に異なります。これらの要因により差動対を構成するPch-MOSFETはしきい値電圧などが微妙に異なり、電流減少によるノンリニアの変化に差が生じます。このことから図 3-8に示すように同相入力電圧範囲内で入力電圧VINに対する入力オフセット電圧は傾きを持ちます。このようなことから、CMRRは同相入力電圧範囲の最大電圧と最小電圧で計算しています。

関連情報

関連情報

- 製品ページ

- アプリケーションノート

- オペアンプFAQ

- オペアンプのパラメトリックサーチはこちら

- オペアンプの購入はこちら