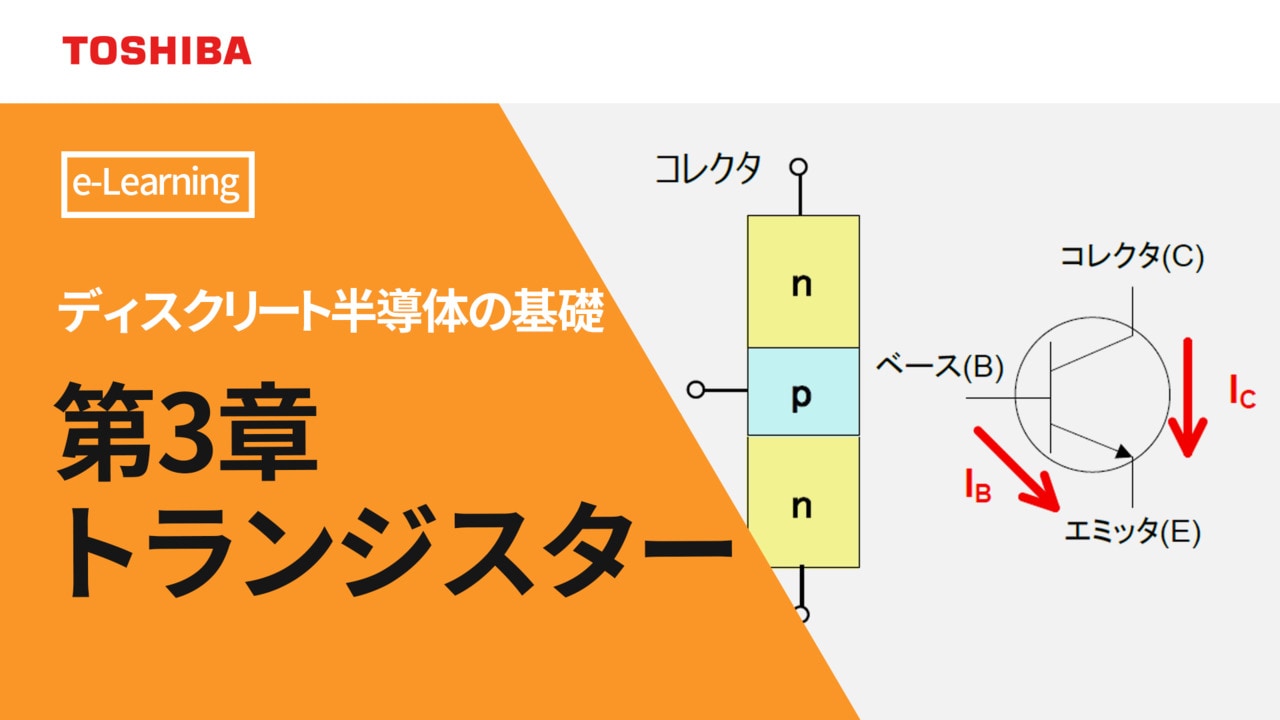

トランジスターとは

トランジスターは、少なくとも3つの端子を持ち、電気信号を増幅する機能やスイッチングする機能を持つ半導体デバイスです。その構造によって大きくバイポーラ-トランジスター (BJT) と電界効果トランジスター (FET) に分けられます。また、これ以外に入力段がMOSFET、出力段がBJTの特性を持つ絶縁ゲートバイポーラ-トランジスター (IGBT) があります。

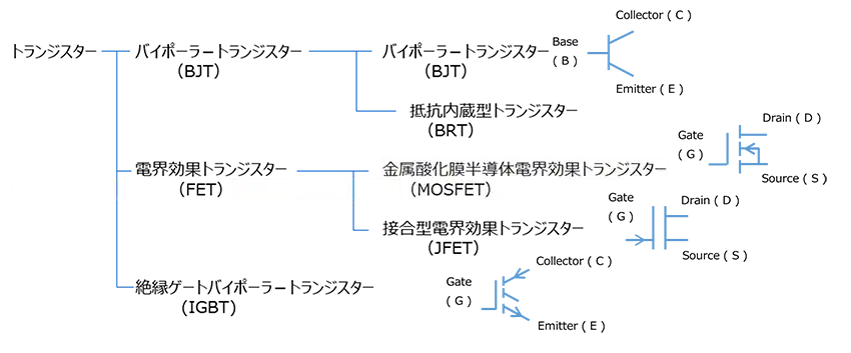

トランジスターの種類と特徴

トランジスターの分類を 図-1 に示します。図では、トランジスターを起点としたツリー構造として整理されており、バイポーラ-トランジスター(BJT)、電界効果トランジスター(FET)、絶縁ゲートバイポーラ-トランジスター(IGBT)に分類されます。

以下のFAQにも説明があります。

- バイポーラ-トランジスター (BJT: Bipolar Junction Transistor)

BJTは2つのpn接合を持ち、電子と正孔の両方を電荷キャリアーとして使用します。このためバイポーラ-トランジスターと呼ばれます。BJTにはベース、コレクター、エミッターの3つの端子があります。NPN-BJTとPNP-BJTの2種類があります。

ベースからエミッターに流れる電流 (ベース電流) に比例してコレクター電流が流れます。このためBJTは電流制御型 (電流駆動型) の素子と呼ばれます。ベース電流が流れない範囲ではトランジスターはオフとなります。

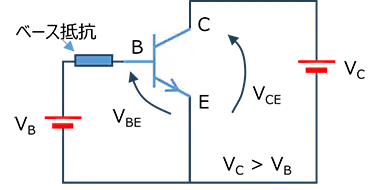

通常は制御信号として電圧を用い、制御電圧を抵抗で電流に変換してベースに入力します (図-3)。この抵抗を内蔵し主にスイッチで使用される抵抗内蔵型トランジスター (BRT: Bias Resistor built-in Transistor) はバイポーラ-トランジスターの一種です。

BJTはMOSFETと異なりベースに電流を流す必要があるためMOSFETに比較して駆動電力が大きくなります。スイッチング速度は低速ですがデバイスの高耐圧化が容易です。また、ゲイン (利得) が得やすく増幅率が高いことが特徴です。高い増幅率を求める回路では、BJTを使います。BJTは伝導度変調効果 (少数キャリアー蓄積効果) により、飽和時の電圧降下が低くなりますが、この効果によりオンからオフへの遷移時間が長くなる欠点も持ちます。

以下のFAQも参考にしてください- FAQ: バイポーラ-トランジスターとは?

- FAQ: 抵抗内蔵型トランジスター (BRT) とは?

- FAQ: 伝導度変調とは何ですか?

- 電界効果トランジスター (FET: Field Effect Transistor)

FETは電流が流れる経路にpn接合を持たないトランジスターです。電荷キャリアーとして電子、または正孔のどちらかのみが使用されます。このためバイポーラートランジスターに対してユニポーラートランジスターとも呼ばれます。FETには主にスイッチングで使用される金属酸化膜半導体電界効果トランジスター (MOSFET) と主に増幅器で使用される接合型電界効果トランジスター (JFET) があります。

FETにはゲート、ドレイン、ソースの3つの端子があります。

ゲート・ソース間に印加する電圧 (ゲート電圧) によって素子がオン・オフします。また飽和領域では、ゲート電圧の大きさによって出力電流の大きさが変化します。このためFETは電圧制御型 (電圧駆動型) の素子と呼ばれます。

寄生容量を充電する電流を除き、ゲート端子に電流は流れません。駆動電流が少ないことが特徴です。また高速スイッチングも特徴として挙げられます。

以下のFAQも参考にしてください

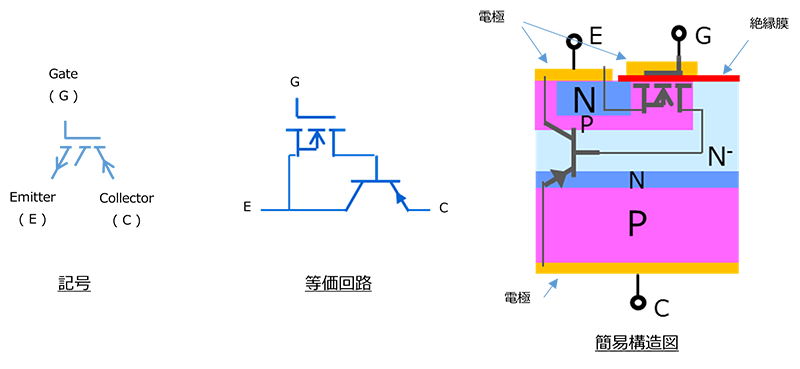

- 絶縁ゲートバイポーラ-トランジスター (IGBT: Insulated Gate Bipolar Transistor)

IGBTは入力段をMOSFET、出力段をBJTとする構造を持ちます。MOSFETの特徴である高速スイッチングとBJTの特徴である低オン電圧 (低飽和電圧) の2つの特徴を併せ持つ製品です。IGBTは動作的には電荷キャリアーとして電子と正孔を使用するため、バイポーラ-トランジスターに分類されることもあります。

IGBTにはゲート、コレクター、エミッターの3つの端子があります。

以下のFAQも参考にしてください- FAQ: IGBTとは何ですか?

トランジスターの構造

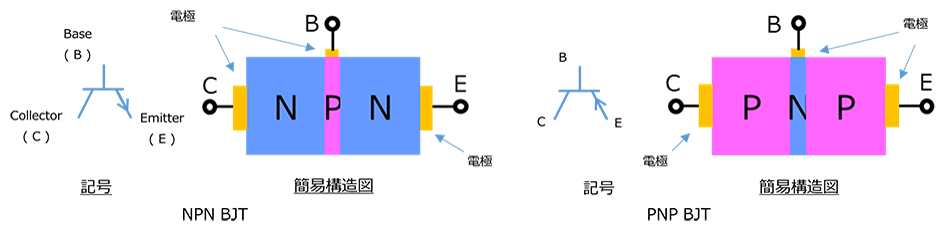

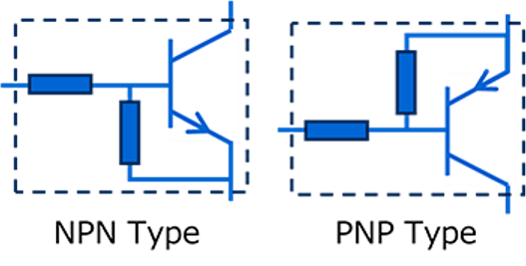

各種トランジスターの簡易構造図と記号を図-2に示します。

- バイポーラ-トランジスター (BJT: Bipolar Junction Transistor)

NPN BJTはn層であるコレクターとエミッターにp層のベースが挟まれる形となります。PNP BJTはp層であるコレクターとエミッターにn層のベースが挟まれる形となります。

直流電流増幅率hFEを高くするために、ベースは非常に薄く、また不純物濃度は コレクター < ベース << エミッター となります。

バイポーラ-トランジスター(BJT)の記号と簡易構造図を図-2 (a)に示します。図中の簡易構造図では、例えば NPN 型では薄い P 層のベースを N 層のエミッターおよびコレクターで挟んだ形として表現していますが、これは動作原理を理解しやすくするための模式図であり、実際の BJT の物理構造がそのまま表現されているわけではありません。

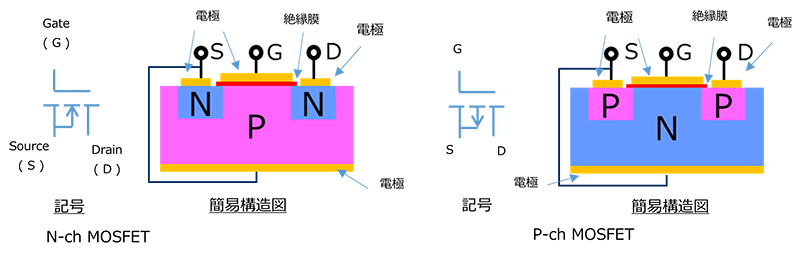

- MOSFET (Metal Oxide Semiconductor Field Effect Transistor)

N-ch MOSFETはp層の中に、n層であるドレインとソースが埋め込まれているような形となります。 (縦構造もありますが、ここでは基本となる横構造で説明します。) 制御端子となるゲートはn層の直上にドレインとソースのp層の一端に被さる形で絶縁膜 (酸化膜) を形成し、その上にゲート電極を配置しています。従って、ゲートはDC的に絶縁されています。ゲートに電圧を印加すると絶縁膜と接するp層に電流の経路が形成されn層であるドレインとソースが電気的に接続されます。このようにp層にn層と同等の経路 (チャネル) が形成されることからnチャネルと (N-ch) MOSFETと呼ばれます。P-ch MOSFETも同様で、 n層の中にp層であるドレインとソースが埋め込まれているような形となります。ゲート電極はドレインとソースのn層の一端に被さる形でp層の直上に絶縁膜を通して配置されています。

MOSFET の記号と簡易構造図を図-2 (b)に示します。図では、横型構造の断面図として N‑ch MOSFET および P‑ch MOSFET を示しており、N‑ch MOSFET では P 型基板、P‑ch MOSFET では N 型基板を用いた構造となっています。基板中にソース(S)およびドレイン(D)を形成し、その上に絶縁膜を介してゲート(G)を配置することで、ゲート電圧によってドレイン・ソース間の導通状態を制御します。

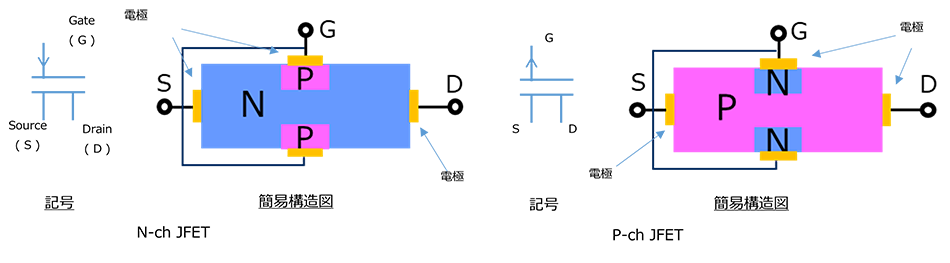

- JFET (Junction Field Effect Transistor)

N-ch JFETはドレインとソースとなるn層にゲートであるp層を埋め込む形となります。接合 (ジャンクション) を形成するn層とp層は逆バイアスで使用されるため、p層からn層に電流は流れません。電流の経路がn層であるためnチャネル (N-ch) と呼ばれます。このn層は抵抗体として動作しています。ゲートに電圧を印加すると、電圧に比例して空乏層が伸びてゲート間の電流の経路を狭め抵抗値が大きくなります。

JFET の記号と簡易構造図を図-2 (c)に示します。例えば N‑ch JFET の場合、N 層を基板として、その上下に P 層を配置する構造として表現されます。ただし、この構造図は JFET の動作原理を理解しやすくすることを目的とした模式図であり、実際のデバイス構造とは一部異なっています。ゲート(G)によってチャネル幅を制御する点が JFET の特徴です。

- IGBT

IGBTはMOSFETとBJTの特徴をあわせ持つデバイスです。入力部はスイッチングが早くドライブ電流が少ないMOSFET構造、出力部は高電流高耐圧が可能なBJT構造となっています。このためBJTに比べ高速スイッチングスピードで、MOSFETに比べ高耐圧、低オン抵抗のデバイスを実現しています。

IGBT の記号と簡易構造図を図-2 (d)に示します。図では、N‑ch IGBT を例に、等価回路およびその等価回路を重ねて表現した簡易構造図を示しています。IGBT は N‑ch MOSFET を基本構造とし、出力段にバイポーラ-トランジスターの要素を組み合わせた構成を持つデバイスであり、MOSFET の高速スイッチング特性と、バイポーラ-トランジスターの低オン電圧特性を併せ持つ点が特徴です。

トランジスターの動作

- バイポーラートランジスター (BJT)

NPN BJTの場合、コレクター (C) に電圧を印加し、ベース (B) ・エミッター (E) 間に約0.7Vの電圧 (オン電圧) を印加するとコレクター電流が流れBJTはオンします。VBEがこのオン電圧より低くなるとオフします。

BJTの相互コンダクタンス (gm: ベースとエミッター間の電圧変化に対するコレクター電流変化) は大きいため、ベースに直接電圧を印加し電圧で制御することは現実的ではありません。図-3に示す回路ではベース抵抗を挿入しベース端子に加えた電圧を電流に変換しています。この電流の変化で制御しています。

NPN‑BJT の最も簡素なバイアス回路の例を図‑3に示します。図では、ベースにはベースバイアス電圧 VB を印加し、その直列に ベース抵抗を挿入する構成としています。また、コレクター・エミッター間にはバイアス電圧 VC を印加しており、VC > VB の関係となっています。この回路では、ベース抵抗によってベース電流の制限が行われるため、エミッター抵抗は挿入していません。

スイッチ用途を目的とし外部抵抗を内蔵した抵抗内蔵型トランジスター (BRT 図-4) もあります。

抵抗内蔵型トランジスター(BRT)の等価回路を図‑4に示します。BRT は、BJT をスイッチ用途で使用する際に必要となるベース抵抗を内蔵したデバイスであり、外付け抵抗を用いずに駆動することができます。これにより、外付け部品点数の削減や実装面積の縮小が可能となり、回路の簡素化に貢献します。

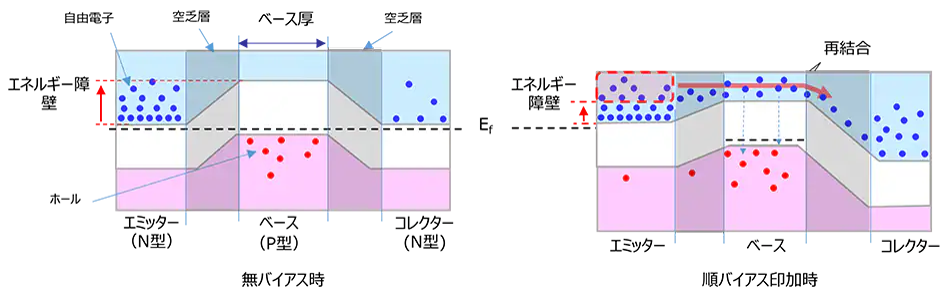

BJTの動作を少しだけ物性的に考えてみます。トランジスターはベース電流を増幅してコレクター電流を流す電流制御型素子ですが、ここではベース電流ではなくベースにかかる電圧で説明します。NPNトランジスターのエネルギーバンド図を図-5に示します。図-5では、無バイアス時とベース・エミッター間に順バイアスを印加した場合の状態を示しています。無バイアス時には、エミッターとベースの pn 接合に形成されるエネルギー障壁により、エミッター中の自由電子はベース側へ移動できず、コレクター・エミッター間に電流は流れません。一方、ベース・エミッター間に順バイアスを印加すると、このエネルギー障壁が低下し、エミッター中の自由電子の一部がベースを越えてコレクター側へ流れ込みます。これが コレクター電流となります。

NPNトランジスターのエミッター・ベース・コレクターの不純物濃度をそれぞれNE・NB・NCとすると、NE >> NB > NC となります。この不純物濃度に比例して、自由電子または正孔が存在します。また、各自由電子の持つエネルギーは、フェルミ分布 (フェルミディラック分布) に従います。

無バイアス状態では各pn接合には空乏層生成による内蔵電位 (エミッターの伝導帯 (Conduction band) の最下限とベースの伝導帯の最下限までのエネルギー差) が発生し、エネルギー障壁が生じています。エミッターの電子はこの障壁を超えることができず、コレクター・エミッター間に電流は流れません。

図-3に示す回路でベース・エミッター間に順バイアス (オン電圧より高いVBE) を印加するとエネルギー障壁が下がり、エミッターにある自由電子の一部は障壁を超えてベースに拡散します。同時にベースにはベース電流として正孔が注入されます。ただし、NE >> NB なので、エミッターから拡散される自由電子の数はベースの正孔の数よりはるかに多い状態です。拡散してきた自由電子の一部はホールと再結合しますが、自由電子の数に対してホールの数が少ないこと (ベース・コレクターの不純物濃度差)、ベースの厚 (幅) が薄いため、そのほとんどがベース・コレクター間の電界によってドリフトしコレクターに流入することになります。これがコレクター電流となります。

- MOSFET

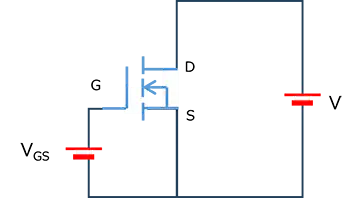

N‑ch MOSFET の最も簡素なバイアス回路の例を図‑6に示します。図では、ゲート・ソース間にバイアス電圧 VGS を印加し、ドレイン・ソース間にバイアス電圧 V を印加する構成としています。ゲート電圧 VGS によってチャネルが形成されますが、ゲートは絶縁されているためゲート電流は流れません。このため、BJT のように電流制限を目的とした抵抗は不要です。ただし、立ち上がりタイミングの調整や発振防止を目的として、ゲートに抵抗を挿入する場合があります。

ゲート・ソース間にしきい値以上の電圧 (VGS) を印加するとドレイン・ソース間が小さな抵抗値RDS (ON) で導通しMOSFETはオンします。VGSがしきい値以下になるとドレイン・ソース間は非導通となりオフします。MOSFETのゲート端子は絶縁されているので、オフさせる場合にゲート電圧がなかなか下がらず時間がかかることがあります。このような場合、ゲート・ソース間に抵抗を挿入することがあります。

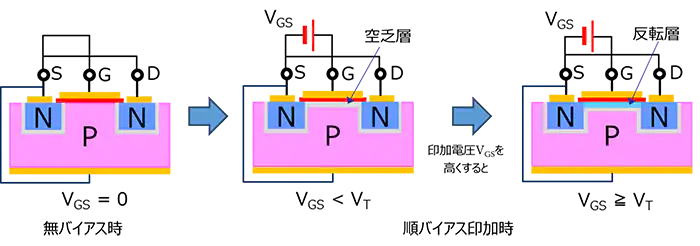

N‑ch MOSFET におけるバイアス状態とVGS印加時の反転層の形成を図‑7に示します。図では、無バイアス状態(VGS=0 V)、しきい値電圧未満の順バイアス状態(VGS<VT)、および しきい値電圧以上の順バイアス状態(VGS≧VT) の 3 つの状態を断面図で示しています。簡単のため、ここではドレイン(D)とソース(S)は外部で短絡された状態としています。短絡しない状態については、以下のFAQを参照してください。

FAQ:MOSFETの動作原理と仕組み|遮断・線形・飽和領域をわかりやすく解説

無バイアス時には、ゲート直下の P 型基板に大きな変化はありませんが、VGS<VT では空乏層が形成されます。さらに VGS≧VT になると、ゲート直下に反転層が形成され、この反転層がドレインとソースを電気的に接続するチャネルとなります。

N型半導体は電子が過多、P型半導体は正孔が過多となっています。ゲート・ソース間に電圧 (VGS) を印加するとゲート電極とその直下のP型半導体はコンデンサーと同様の働きをします。ここでゲート・ソース間に電圧を印加すると電極板側はプラスに帯電し、P型半導体側はマイナスに帯電します (電子が集まり電子過多の状態)。つまり、ゲート直下のP型半導体表面 にはマイナスの電荷が集められ自由電子が多い状態となります。この状態はP型半導体でありながらN型半導体と同じ性質を持つことから、反転層と呼ばれます。

無バイアス状態からゲートに電圧VGSを印加します。まず、反転層形成前にゲート電極と対抗するP型半導体の正孔が消滅し、空乏層が生じます。しきい値電圧VTと呼ばれる電圧に達すると、反転層が形成されます。ソースとドレインはこの反転層で接続されることになります。この反転層をチャネルと呼び、この例の場合、N型のチャネルなのでN-ch MOSFETとなります。

このようにMOSFETはOFFからONへの遷移時に、このコンデンサーの充電電流が必要ですが、オンしてしまえば、BJTのベース電流のような電流は必要ないので、省電力化が可能となります。 (ただし、電力用途のMOSFETなどでは寄生のコンデンサー容量が大きく、この容量を急速に充電しオンさせるためにドライブ回路が必要です)

- JFET

動作モードとしてはエンハンスメント型 (ゲート・ソース間の電圧が0Vの時には電流が流れない) とデプレッション (ディプリーション型) (ゲート・ソース間の電圧が0Vの時に電流が流れる) があります。

以下デプレッション型の動作を説明します。

N-ch JFETはN型半導体にゲートとしてP型半導体を埋め込んだ形となっています。ゲートとドレイン・ソース間にはpn接合が形成されています。この接合は逆バイアスの状態で使用されます。

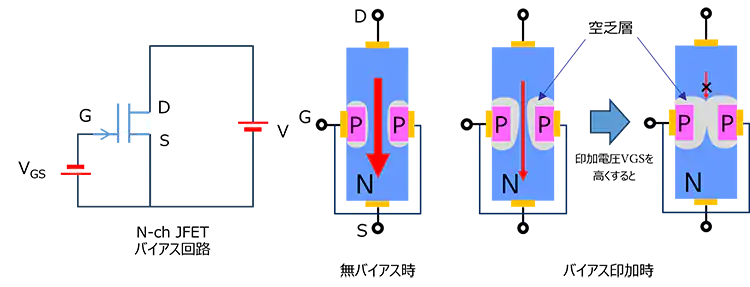

N‑ch JFET におけるバイアス状態と空乏層の変化を図‑8に示します。図では、最も簡素な動作回路とともに、無バイアス時およびバイアス印加時の断面図を示しています。ゲート・ソース間電圧 VGS が大きくなるにしたがって、ゲート接合部に形成される空乏層が広がり、チャネル幅が次第に狭まっていく様子を示しています。

ゲート・ソース間にVG<VSとなるように逆バイアスVGSを印加していくと、空乏層が伸びてチャネルが狭まります。これによって電流の流れは阻害される (抵抗を持つ) ようになります。さらに逆バイアスを大きくすると、チャネルは空乏層によって遮断されます。

- IGBT

IGBTはN-ch MOSFETのドレイン (n層) にp層を追加しコレクターとしたデバイスです。入力部はスイッチングが早くドライブ電流が少ないMOSFET構造、出力部は高電流高耐圧が可能なBJT構造を持つのデバイスです。このことでBJTに比べ高スピードで、MOSFETに比べ高耐圧、低オン抵抗のデバイスを実現しています。

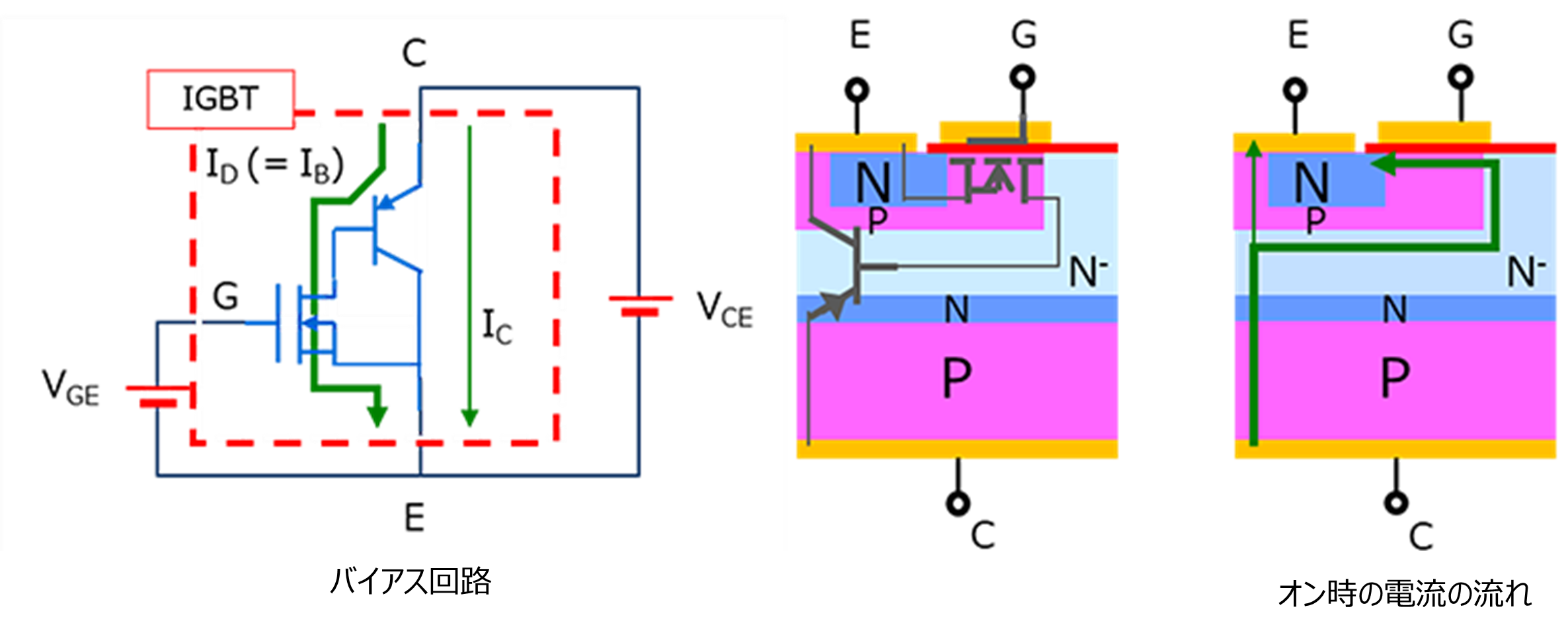

IGBT のオン時における電流の流れを図‑9に示します。(a)は回路図、(b)は構造図にIGBTの等価回路を重ねた図、(c)はオン状態における電流経路を示した構造図を示しています。ゲート・エミッター間に電圧が印加されると、入力段である MOSFET がオンし、これにより出力段のバイポーラ-トランジスターが動作します。オン時の電流経路を矢印で示しています。動作に関して詳しくは以下のFAQを参照してください。

FAQ: IGBTとは

図-9バイアス回路に示すように、、ゲート(G)・エミッター(E)間に電圧VGE、コレクター(C)・エミッター(E)間に電圧VCEを印加します。この時、VGEがN-ch MOSFETのしきい値以上であれば、MOSFETはオンします。これによって、PNPトランジスターのベースがエミッターと等電位となり、PNPトランジスターがオンして、コレクター電流ICが流れます。

VGEがN-ch MOSFETのしきい値より下がれば、オフになります。ただし、IGBTはオフになるまでにテール電流と呼ばれる電流がある期間流れます。これはオン時にオン抵抗を低減する電導度変調効果によります。

トランジスターの用途

トランジスターはあらゆる電子機器に使用され、主に電気信号をスイッチ (オン/オフ) する回路や増幅させる回路に使用されます。スイッチとしてはロジック信号レベル (~5V) 程度でオン/オフさせる回路やスイッチング電源などがあります。増幅回路も単なる信号の増幅だけでなく発振回路などにも使用されます。このようにトランジスターは広範囲に使用されてています

これらの回路にはBJTとMOSFETのどちらも使用される可能性があります。その回路でどの特性 (スピード、損失、ゲインなど) を重要視するか、どの電圧・電流・周波数で使用するかによって、その選択は変わってきます。

参考のために、それぞれのデバイスに関係するキーワードを列挙しておきます。

- MOSFET: 省電力、高速スイッチング、入力インピーダンスが高い

- BJT: アナログ (リニアリティー・高ゲイン)、低ノイズ、低電圧 (オン電圧0.7V程度) でオン

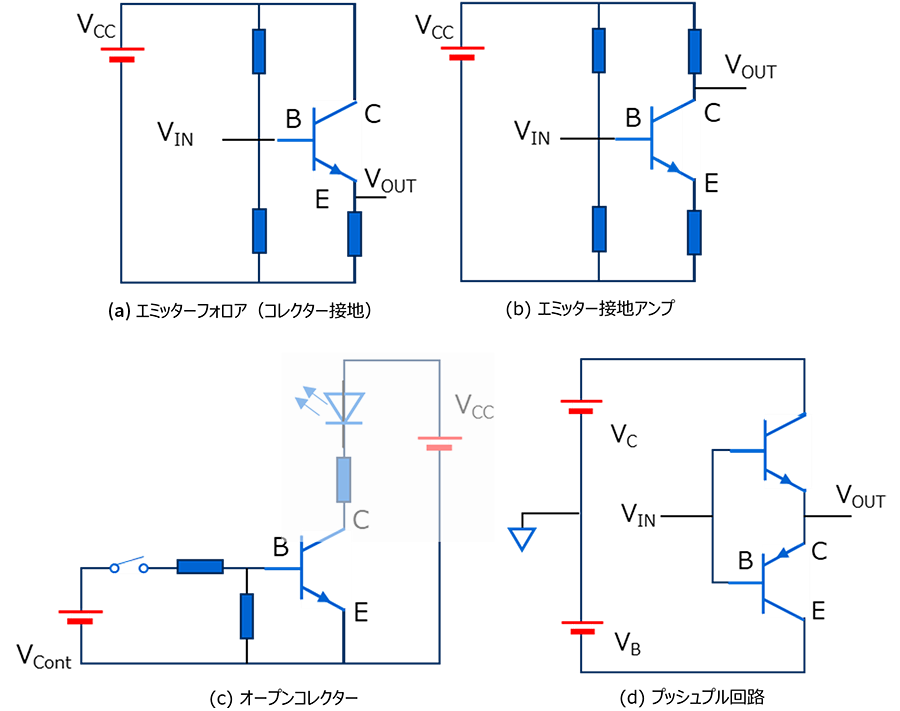

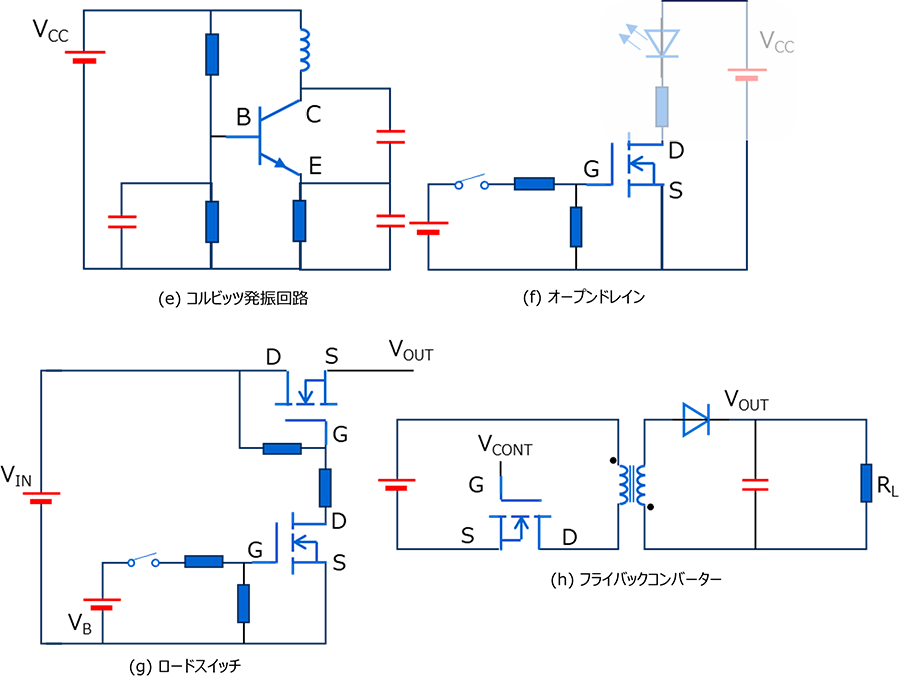

いくつかの回路例を下記に示します。

図-10 トランジスターを用いた回路例

スイッチング電源に興味のある方は、以下の動画も参考にしてください

[教育] スイッチング電源の基礎 (5) ~フルブリッジコンバーター~

[教育] スイッチング電源の基礎 (6) ~DCDCコンバーターについて~

[教育] スイッチング電源の基礎 (7) ~共振ハーフブリッジコンバーター~

[教育] スイッチング電源の基礎 (8) ~ブリッジレスPFC~

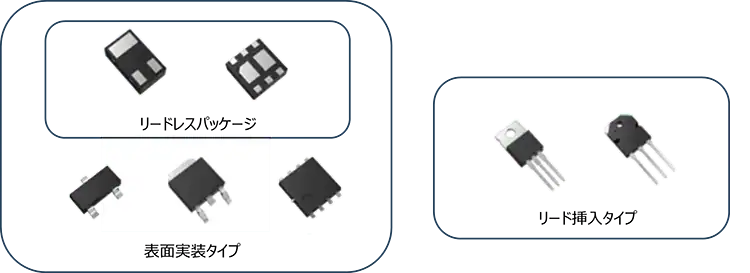

トランジスターのパッケージ

東芝のBJT・MOSFETは小型のパッケージからパワー用途のパッケージまで多種多様なパッケージを展開しています。小型の製品では2in1などの複合タイプも提供しています。

パッケージの詳細 (寸法・参考PAD) については、以下のページを参照ください

関連リンク

製品ラインアップについては、以下のページ、ドキュメントをご参照ください。

パラメトリック検索

FAQ

* このFAQ内で使用している社名・商品名・サービス名などは、それぞれ各社が商標として使用している場合があります。