-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

1-13. ESD対策

CMOSロジックICは静電気に対し規定に沿った強度がありますが、それ以上の大きさの静電気が印加されると誤動作や破壊が起きる可能性があります。

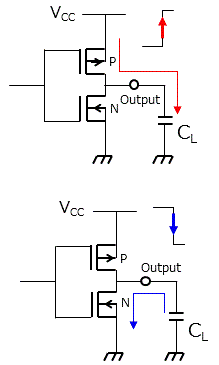

CMOSロジックICは入力ゲートに用いられるゲート酸化膜が数百Å~千数百Å程度と薄いため,静電気のような数百から数千ボルトの電圧が印加されると電気的に破壊してしまいます。

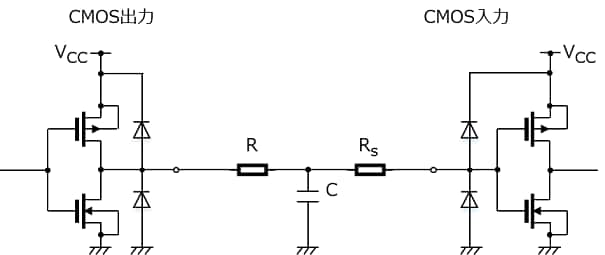

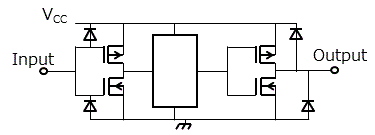

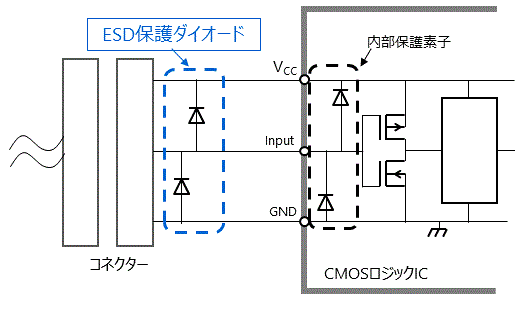

一般的に、これを防ぐため、各入力端子に保護回路を設け入力ゲートを静電気から保護しています。しかしながら、内蔵の保護素子では保護に限界があります。静電気などの異常な入力が予想される入力(基板外部と接続される入力など)に対しては、ESD保護ダイオードなどを挿入し保護能力を強化してください。

ESD発生モデルは色々ありますが、代表的なモデルを紹介します。

人体帯電モデル(HBM: Human Body Model)

このモデルは、人体が静電気の発生源となり、そこから静電気放電が生じることで半導体製品に損傷を起こすモデルです。

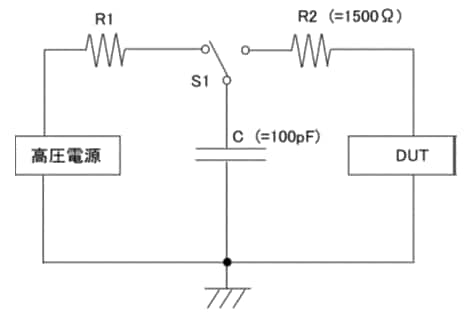

実際に人体がどのくらいの静電容量を持つかについては、いろいろと議論がありますが、評価を行う際には100 pF, 1500 Ωの条件に設定したコンデンサ放電法で行います。

HBMの試験回路は下図の通りです。

- 1-12. ラッチアップ対策

- 16/16