-

My ToshibaSemicon

- セミコンダクタートップ

-

アプリケーション車載

ボディエレクトロニクス

xEV

インフォテインメント

産業用機器業務用機器

民生/個人用機器 -

製品車載用デバイス

ディスクリート半導体

ダイオード

トランジスター

汎用ロジックIC

アナログデバイス

※

: 製品一覧(パラメトリックサーチ)

パワー半導体※

: 製品一覧(パラメトリックサーチ)

アイソレーター/ソリッドステートリレー(SSR)フォトカプラー

デジタルアイソレーター

ソリッドステートリレー (SSR)

光伝送モジュール

※

: 製品一覧(パラメトリックサーチ)

MOSFETIGBT/IEGTバイポーラートランジスター※

: 製品一覧(パラメトリックサーチ)

ダイオード※

: 製品一覧(パラメトリックサーチ)

マイクロコントローラーモータードライバーインテリジェントパワーIC※

: 製品一覧(パラメトリックサーチ)

パワーマネージメントICリニアーIC※

: 製品一覧(パラメトリックサーチ)

汎用ロジックICリニアーイメージセンサーその他専用ICその他専用IC

※

: 製品一覧(パラメトリックサーチ)

-

開発/設計支援

-

知る/学ぶ

- ご購入

- 品番・キーワード検索

- クロスリファレンス検索

- パラメトリック検索

- オンラインディストリビューター在庫検索

本機能は Internet Explorer 11 ではご利用頂けません。最新のGoogle Chrome, Microsoft Edge, Mozilla Firefox, Safariにてご利用ください。

品番は3文字以上指定して下さい。 複数品番の検索はこちら。

クロスリファレンスでは参考品名が表示されますので、製品に関する最新の情報をデータシート等でご確認の上、単独およびシステム全体で十分に評価し、お客様の責任において適用可否を判断してください。参考にしている情報は、取得した時点の各メーカーの公式情報に基づいた当社の推定によるものです。当社は、情報の正確性、完全性に関して一切の保証をいたしません。また、情報は予告なく変更されることがあります。

品番は3文字以上指定して下さい。

オンラインディストリビューターが保有する東芝製品の在庫照会および購入が行えるサービスです。

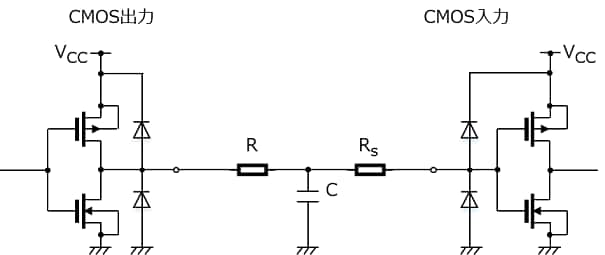

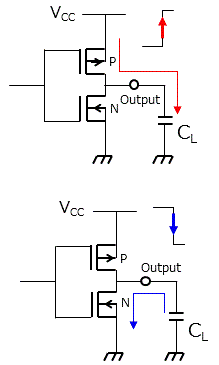

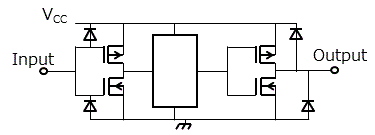

1-9-2. 反射ノイズの対策

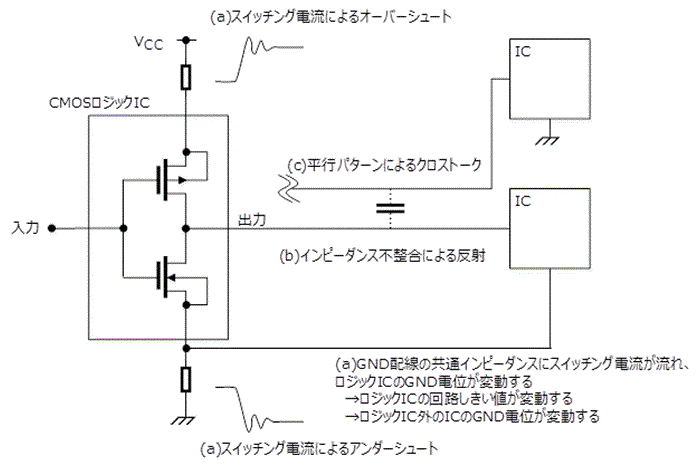

高速ロジックICの出力は、反射により信号の遅延、リンギングおよびオーバー、アンダーシュートが増加します。

<伝送線の反射>

一般に、配線の特性インピーダンス(*1) は75~150 Ω程度ですが、高速ロジックICは入出力インピーダンスが配線の特性インピーダンスと異なるため、送信、受信端とも反射が発生します。

出力の立ち上がりが遅い場合では問題となりません。これは反射波が出力の立ち上がり部分に重なるため、大きく影響しないためです。反射が問題となるのは反射波が立ち上がり後の波形に重なる場合であり、出力のtrが下式を満たす場合が考えられます。

tr く 2T

tr : 出力信号の立ち上がり時間

T : 配線の送信端から受信端までの遅延時間

立ち上がり時間が3 nsの場合、配線の伝搬遅延時間を5 ns/mとすると30 cmから反射の影響が顕著となります。

*1:特性インピーダンスとは

特性インピーダンスは伝送線路(基板配線、同軸ケーブル)の特性を表す指標の一つです。

特性インピーダンスの計算式は、伝送線路の単位長あたりのインダクタンスLとキャパシタンスCから、Z0=(L/C)^(1/2)となり、単位はΩ(オーム)を使用します。

特性インピーダンス50Ωの伝送線路に終端抵抗50Ωを接続した場合、接続点では反射が発生しませんが、特性インピーダンスと抵抗の値に相違がある場合は、接続点で反射が発生します。

<反射対策>

① 実装密度を高くして配線を短くし、配線のインダクタンスやキャパシタンスを減らす。ただし、配線間のクロストークに注意が必要。(クロストークについては後述します)

② 必要以上に出力電流の大きいICを使わない。

➂ CMOSロジックICの入出力インピーダンスと配線の特性インピーダンス間でインピーダンス整合がとれるように終端処理をする。

④ CMOSロジックICの一つの出力端子に複数個のCMOSロジックICを接続する場合配線は一つにする。